Na atual era de rápido avanço da inteligência artificial e da computação de elevado desempenho, a largura de banda da memória tornou-se um estrangulamento crítico que limita o poder computacional - aquilo a que a indústria chama frequentemente o problema da “parede de memória”. Imagine a capacidade de computação da GPU como uma linha de montagem de uma super-fábrica, enquanto a memória tradicional fornece apenas um “tubo de fornecimento de matéria-prima” estreito, deixando os dispendiosos recursos de computação inactivos e à espera de dados. Este é o principal desafio que o treinamento em IA enfrenta atualmente. O HBM4 (High Bandwidth Memory 4) está aqui para acabar com esse gargalo de uma vez por todas, fornecendo a espinha dorsal de armazenamento essencial para a explosão de computação impulsionada por IA.

O que é o HBM4?

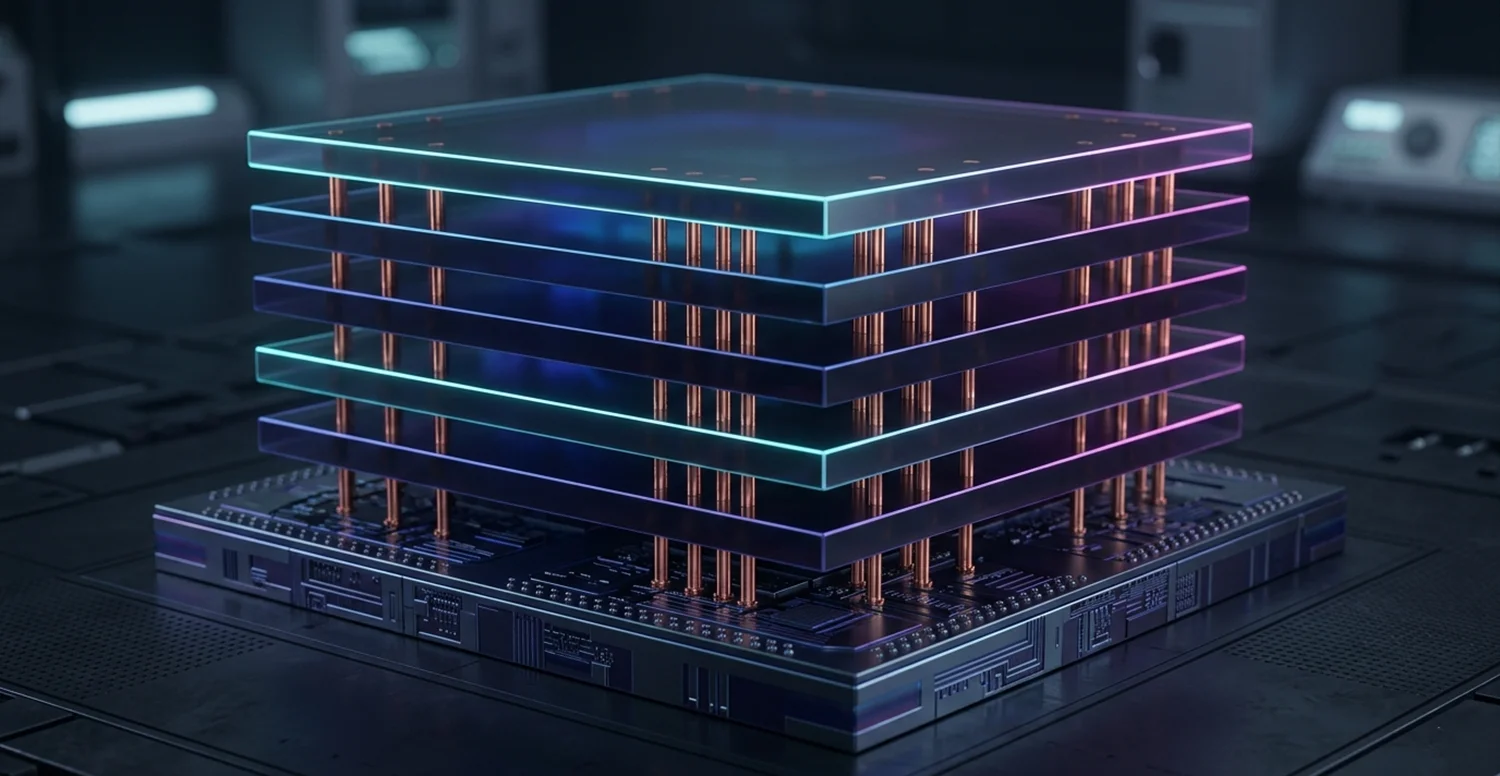

Memória de elevada largura de banda nasceu para resolver o problema da “parede de memória”, aumentando a largura de banda da memória para desbloquear o poder de computação. Ele adota uma filosofia de design completamente diferente da memória tradicional - empilhando verticalmente vários chips DRAM e interconectando-os em alta velocidade usando a tecnologia Through-Silicon Via (TSV), alcançando uma enorme largura de transferência de dados em um espaço físico extremamente pequeno. Desde a primeira geração do HBM em 2013 até hoje, esta família evoluiu ao longo de mais de uma década, e o HBM4 é o seu mais recente marco.

HBM4 é a tecnologia de memória de alta largura de banda de sexta geração, lançada oficialmente como a Norma JESD270-4 pelo JEDEC em abril de 2025. Como sucessor do HBM3/HBM3E, ele foi desenvolvido especificamente para treinamento em IA, computação de alto desempenho e GPUs de data center de ponta. Ele dá continuidade à arquitetura empilhada em 3D da família HBM, empilhando vários chips DRAM verticalmente e integrando-os a uma matriz de base lógica para alcançar uma densidade de largura de banda extremamente alta e um empacotamento compacto, o que lhe rendeu o apelido de “super celeiro” do setor para computação de IA.

O que torna o HBM4 tão poderoso?

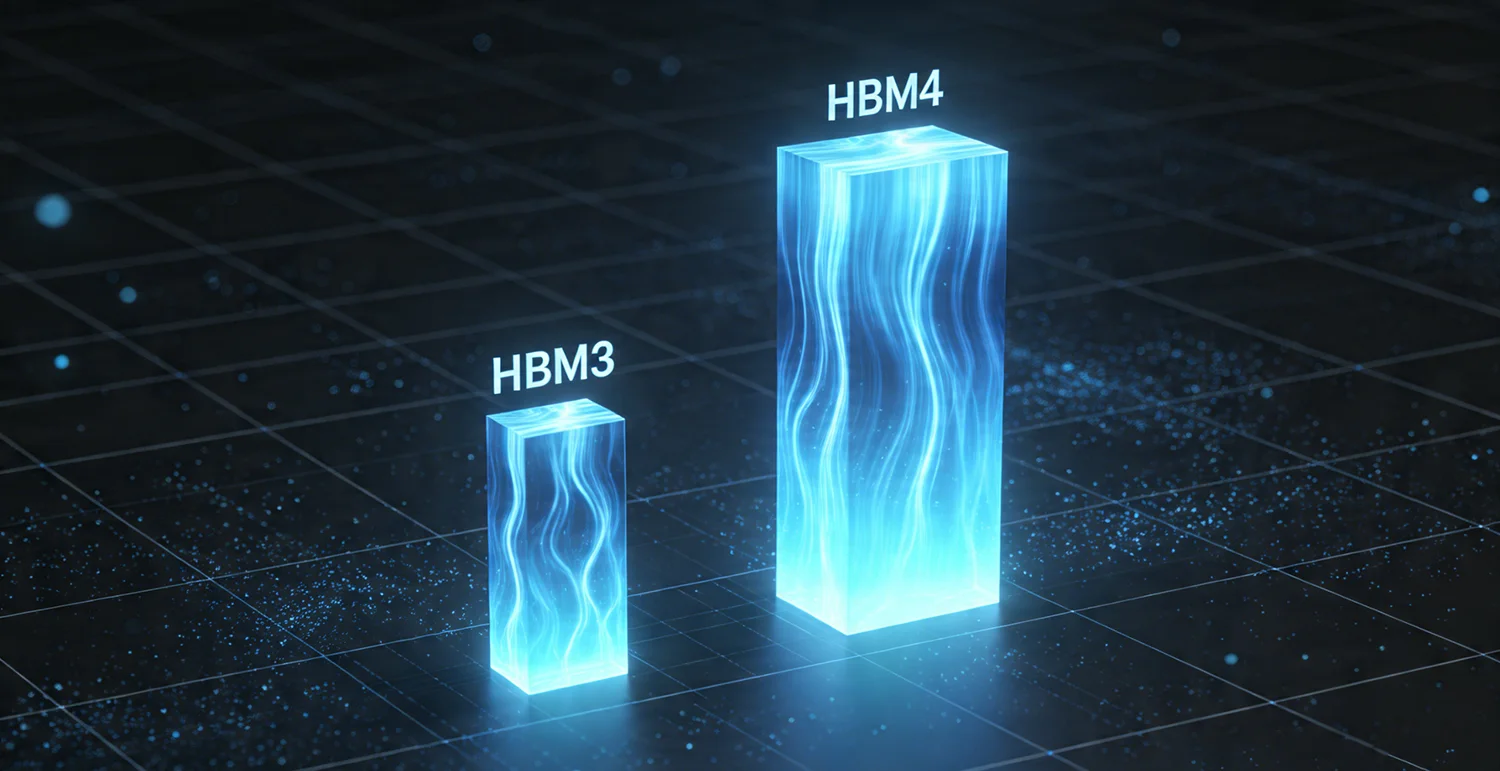

Comparado com a geração anterior HBM3E, o HBM4 oferece um salto de desempenho abrangente. A tabela abaixo dá-lhe um rápido olhar sobre as principais mudanças:

| Especificação | HBM3 | HBM4 | Melhoria |

|---|---|---|---|

| Largura da interface | 1024 bits | 2048 bits | Duplicado |

| Largura de banda padrão | ~819 GB/s | 2 TB/s | ~2.4× |

| Canais independentes | 16 | 32 | Duplicado |

| Capacidade máxima por pilha | 24 GB (8-Hi) | 64 GB (16-Hi) | ~2.7× |

| Tensão de funcionamento | Fixo ~1,1V | VDDQ 0,7-0,9V, VDDC 1,0-1,05V | Mais flexível, mais eficiente |

Vamos agora analisar o que estes números realmente significam.

Interface mais ampla, maior largura de banda

O HBM4 dobra a interface de dados por pilha, de 1024 bits para 2048 bits. O que é que isto significa? A memória DDR5 mais avançada atualmente tem uma largura de interface de canal único de apenas 64 bits. Isso significa que uma pilha HBM4 tem a largura de banda equivalente a 32 canais DDR5 trabalhando simultaneamente. Com a largura de interface dobrada, a largura de banda total dobra automaticamente, mesmo com a mesma taxa de dados. E os produtos de fornecedores reais geralmente são executados em velocidades mais altas, de modo que a largura de banda final pode facilmente exceder 2 TB/s, chegando até mesmo a mais de 3 TB/s.

Mais canais, programação de dados mais flexível

O número de canais aumenta de 16 para 32, e cada canal inclui dois pseudo-canais. Os canais podem ser considerados como “pistas” independentes dentro da memória - mais canais significam que o sistema pode emitir mais pedidos de acesso à memória em simultâneo sem interferir uns com os outros. Isto é especialmente favorável às operações de matriz massivamente paralelas na computação de IA, reduzindo significativamente a contenção de acesso e melhorando a largura de banda efectiva.

Maior capacidade, com capacidade para todo o modelo

Ao aumentar as camadas da pilha DRAM de um máximo de 8 para 16, uma única pilha de memória HBM4 pode atingir até 64 GB. Em produtos reais, um acelerador de IA geralmente integra de 4 a 8 pilhas HBM, o que significa que a capacidade total de memória pode facilmente exceder 256 GB ou até 512 GB. Para modelos grandes com trilhões de parâmetros, essa capacidade permite que os parâmetros do modelo e os resultados intermediários residam inteiramente na memória de alta velocidade, eliminando transferências frequentes da VRAM mais lenta ou da memória do sistema.

Tensão mais baixa, melhor eficiência energética

O HBM4 introduz um gerenciamento de voltagem mais refinado. A tensão de E/S VDDQ pode ser ajustada entre 0,7V e 0,9V, e a tensão do núcleo VDDC pode ser selecionada entre 1,0V e 1,05V. Tensões mais baixas reduzem diretamente o consumo de energia. De acordo com os dados do fornecedor, a energia do HBM4 por bit transferido é cerca de 40% menor do que a do HBM3E. Para grandes centros de dados, isso significa contas de eletricidade mais baixas e demandas de refrigeração reduzidas.

Nova funcionalidade de segurança: DRFM

O HBM4 também adiciona um importante recurso de confiabilidade: o DRFM (Direted Refresh Management). Ele efetivamente se defende contra ataques “Row-Hammer”, uma vulnerabilidade de segurança onde a leitura e gravação repetida e rápida de linhas de memória adjacentes causa inversões de bits nas linhas vizinhas. O DRFM identifica de forma inteligente e actualiza seletivamente essas linhas, aumentando significativamente a segurança da memória e a integridade dos dados.

Quais são os principais avanços técnicos do HBM4?

Ligação híbrida

A ligação híbrida é vista como a próxima solução revolucionária no acondicionamento de memórias. A tecnologia tradicional de micro-bombas utiliza saliências metálicas à escala de microns para ligar os chips, com um passo de cerca de 10μm - uma limitação física que impede o empilhamento de maior densidade e uma transmissão de sinal mais rápida. A ligação híbrida elimina totalmente estas saliências, preparando as superfícies de cobre de dois chips para serem atomicamente planas e limpas e, em seguida, colocando-as em contacto direto para que os átomos de cobre se difundam e se fundam sob temperatura e pressão.

De acordo com os dados de teste publicados pela Samsung, a ligação híbrida pode reduzir o passo da interconexão chip a chip para menos de 10μm, aumentando a densidade da interconexão de várias vezes a dezenas de vezes, ao mesmo tempo em que oferece menor resistência, caminhos de sinal mais curtos e melhor dissipação de calor. Os dados medidos pela Samsung mostram que a ligação híbrida sem bumpless pode aumentar a altura da pilha HBM em um terço e reduzir a resistência térmica em 20%. No entanto, como o equipamento de ligação híbrida é dispendioso (cerca de duas vezes mais caro do que as máquinas de ligação tradicionais) e o rendimento da produção em massa ainda precisa de ser melhorado, esta tecnologia ainda não foi aplicada aos actuais produtos HBM4 produzidos em volume. A Samsung enviou amostras de 16-Hi HBM baseadas em ligação híbrida para clientes, com a expetativa de que a adoção comercial comece gradualmente a partir do HBM4E (a versão aprimorada do HBM4).

Interface distribuída e arquitetura de pseudo-canal

O HBM4 adota um design com 32 canais totalmente independentes - o dobro do HBM3 - e cada canal é equipado com 2 pseudo-canais, suportando 32 modos DQ. A vantagem desta arquitetura distribuída é que ela não requer que todos os canais operem sincronizadamente. Cada canal pode lidar com solicitações de dados independentemente, melhorando dramaticamente a eficiência do acesso paralelo. Isto é especialmente adequado para operações de tensor e padrões de acesso a dados irregulares no treino de modelos de IA.

Em comparação com o design de canal único da memória tradicional, a arquitetura multicanal do HBM4 é como expandir uma rodovia de pista única em 32 rodovias independentes de múltiplas pistas, cada uma capaz de transmitir dados eficientemente ao mesmo tempo - eliminando completamente os engarrafamentos de dados e permitindo que as GPUs utilizem mais plenamente seu poder de computação.

Design de interface ampla e de baixo consumo

O HBM4 usa uma estratégia de “interface ultra-ampla + freqüência de clock relativamente baixa” para alcançar uma largura de banda extremamente alta, mantendo a densidade de potência baixa. As memórias tradicionais geralmente aumentam a largura de banda através do aumento das freqüências de clock, o que leva a um consumo de energia muito maior. O HBM4 faz o oposto: com um barramento de dados de 2048 bits de largura, ele oferece várias vezes a largura de banda da memória convencional em frequências relativamente modestas. Este design reduz a energia do HBM4 por bit em 30-40%, uma vantagem significativa na tendência de redução de custos de IA e melhoria de eficiência.

Além disso, o HBM4 suporta a otimização da tensão VDDQ específica do fornecedor (ajustável entre 0,7V e 0,9V), melhorando ainda mais a eficiência energética. Isso permite que as implantações de centros de dados em larga escala controlem efetivamente a energia total e reduzam os custos operacionais. Ao mesmo tempo, o HBM4 mantém a compatibilidade com os controladores HBM3 - um único controlador pode suportar ambas as gerações de memória, diminuindo a barreira para atualizações de sistema.

HBM4 Progresso e roteiros dos três gigantes

A Samsung é o primeiro fabricante do mundo a anunciar a produção em massa do HBM4. A Samsung Electronics anunciou, em 12 de fevereiro de 2026, que havia iniciado a primeira produção em massa comercial global do HBM4 e começado as remessas para os clientes, usando uma matriz lógica de 4nm e tecnologia de empilhamento de 12-Hi, oferecendo uma taxa de dados de 11,7 Gbps e largura de banda de 3,3 TB/s - excedendo em muito o padrão JEDEC de 8 Gbps e 2 TB/s. A Samsung planeja introduzir amostras do HBM4E no segundo semestre de 2026 para melhorias adicionais de desempenho, enquanto também desenvolve uma versão empilhada de 16-Hi que expande a capacidade por pilha para 48 GB, abrindo caminho para aceleradores de IA de próxima geração.

A SK Hynix está a fazer rápidos progressos no espaço HBM4. De acordo com o seu roteiro tecnológico, planeia lançar um produto HBM4 empilhado de 16-Hi em 2026 com uma capacidade de 48 GB e uma atualização da largura da interface unificada para 2048 bits. Embora a empresa esteja a investir ativamente em tecnologias de empacotamento da próxima geração, como a ligação híbrida, as amostras de 16-Hi que demonstrou até agora ainda utilizam a sua tecnologia MR-MUF madura. A SK Hynix planeia aumentar a produção em volume em 2026, trabalhando em estreita colaboração com clientes importantes como a NVIDIA e a AMD.

A Micron Technology confirmou que sua memória HBM4 entrou em produção em massa no primeiro trimestre de 2026, com remessas iniciais sendo versões de 36 GB 12-Hi oferecendo mais de 2.8 TB / s de largura de banda de memória. O produto será desenvolvido especificamente para a plataforma Vera Rubin da NVIDIA para oferecer suporte ao treinamento de IA de data center de próxima geração. Essa estratégia “personalizada sob demanda” posiciona a Micron favoravelmente em segmentos específicos de clientes.

Como o HBM4 potencializará a IA e a computação de alto desempenho?

Impulsionar os aceleradores de IA da próxima geração

O HBM4 se tornou a memória padrão para GPUs de data center de última geração. Os principais fornecedores de chips de IA - NVIDIA, AMD, Intel - estão todos a adotar o HBM4 nas suas mais recentes plataformas de aceleração. Por exemplo, na plataforma Vera Rubin da NVIDIA, com oito stacks HBM4, a largura de banda teórica da memória pode chegar a 22 TB/s e, com uma capacidade de memória inicial de 288 GB, oferece amplo espaço e canais de dados para o treinamento de modelos grandes de trilhões de parâmetros. A próxima geração da série Instinct MI400 da AMD também planeia configurações robustas de HBM4: o modelo MI455X apresentará 12 pilhas HBM4, totalizando 432 GB de capacidade e 19,6 TB/s de largura de banda, visando tarefas de formação e inferência de IA em grande escala com uso intensivo de memória e largura de banda. Além disso, o acelerador de IA de próxima geração da Intel, Jaguar Shores, também adoptará a tecnologia HBM4 - embora não tenham sido divulgados valores específicos de largura de banda e capacidade, a adesão ao ecossistema HBM4 é uma direção clara.

Permitir o treino de grandes modelos sem restrições de memória

O treinamento generativo de IA, especialmente para grandes modelos de linguagem com centenas de bilhões ou mesmo trilhões de parâmetros, é o cenário de aplicação central para o HBM4. Esses modelos requerem o processamento simultâneo de conjuntos de parâmetros e dados massivos, colocando requisitos extremamente exigentes na largura de banda e capacidade da memória. Os 288-384 GB de memória por placa aceleradora fornecidos pelo HBM4 significam que uma única placa pode conter grandes parâmetros de modelo e longas janelas de contexto que anteriormente exigiam várias placas trabalhando juntas. Isso elimina a necessidade de particionar frequentemente os dados entre placas durante o treinamento, evitando a sobrecarga de comunicação e as perdas de eficiência do sharding de modelo, reduzindo significativamente os ciclos de treinamento. Na implantação real de serviços de IA, o HBM4 pode melhorar o desempenho de inferência de grandes modelos em mais de 69%.

Acelerar a investigação científica e a simulação

Na computação de alto desempenho, o HBM4 fornece uma infraestrutura crítica para a computação científica que requer um rendimento massivo de dados. Quer se trate de previsão do tempo, simulação de computação quântica ou análise de sequenciamento de genoma, todos dependem de sistemas de memória de alta largura de banda e alta capacidade. Veja o caso da previsão do tempo: estações meteorológicas globais, satélites e radares geram grandes quantidades de dados em tempo real a cada momento. O HBM4 pode processar estes fluxos de dados rapidamente, permitindo que os supercomputadores completem cálculos de modelos atmosféricos mais detalhados em menos tempo, melhorando assim a precisão e a velocidade de alerta precoce das previsões de condições meteorológicas extremas. No seqüenciamento do genoma, o HBM4 pode comparar e analisar simultaneamente milhões de seqüências genéticas, acelerando a identificação de genes relacionados a doenças e alvos de drogas, economizando tempo valioso para o desenvolvimento de novas drogas.

Expansão de gráficos de alta qualidade e visualização profissional

Embora as placas gráficas de consumo atualmente usem principalmente a memória GDDR, a série HBM sempre foi uma escolha potencial para estações de trabalho gráficas profissionais e placas de jogos de primeira linha devido à sua largura de banda ultra-alta e baixo consumo de energia. À medida que os custos de produção em massa do HBM4 diminuem gradualmente, os utilizadores comuns podem um dia desfrutar de experiências de criação de conteúdo mais suaves e eficientes em cenários como jogos 8K, renderização em tempo real e edição de vídeo. Para profissionais que lidam com vídeo de altíssima resolução e modelagem 3D complexa, o HBM4 reduzirá significativamente os tempos de espera de renderização, tornando o processo criativo mais fluido e natural.

HBM4, a tecnologia de memória de alta largura de banda de sexta geração, alcança um salto duplo em largura de banda e capacidade através da sua interface ultra-larga de 2048 bits, arquitetura de 32 canais e tecnologia de ligação híbrida. É uma solução de memória essencial para ultrapassar o estrangulamento da “parede de memória”. Não só fornece um poderoso suporte de armazenamento para treino de IA, computação de alto desempenho e GPUs de centros de dados topo de gama, como também marca o início de uma nova era em que a tecnologia de memória entra na era da ligação híbrida e do empilhamento 3D. Com a comercialização em larga escala do HBM4 e o amadurecimento contínuo de sua tecnologia, temos todos os motivos para acreditar que o poder de computação de IA verá uma nova explosão de crescimento, desbloqueando mais tecnologias de ponta e cenários de aplicação, e trazendo mudanças tremendas para o desenvolvimento da sociedade humana.