In today’s rapidly advancing era of artificial intelligence and high-performance computing, memory bandwidth has become a critical bottleneck limiting computational power—what the industry often calls the “memory wall” problem. Imagine the GPU’s compute capability as a super-factory assembly line, while traditional memory provides only a narrow “raw material supply pipe,” leaving expensive compute resources idling and waiting for data. This is the core challenge facing AI training today. HBM4 (High Bandwidth Memory 4) is here to shatter this bottleneck once and for all, providing the essential storage backbone for the AI-driven compute explosion.

What is HBM4?

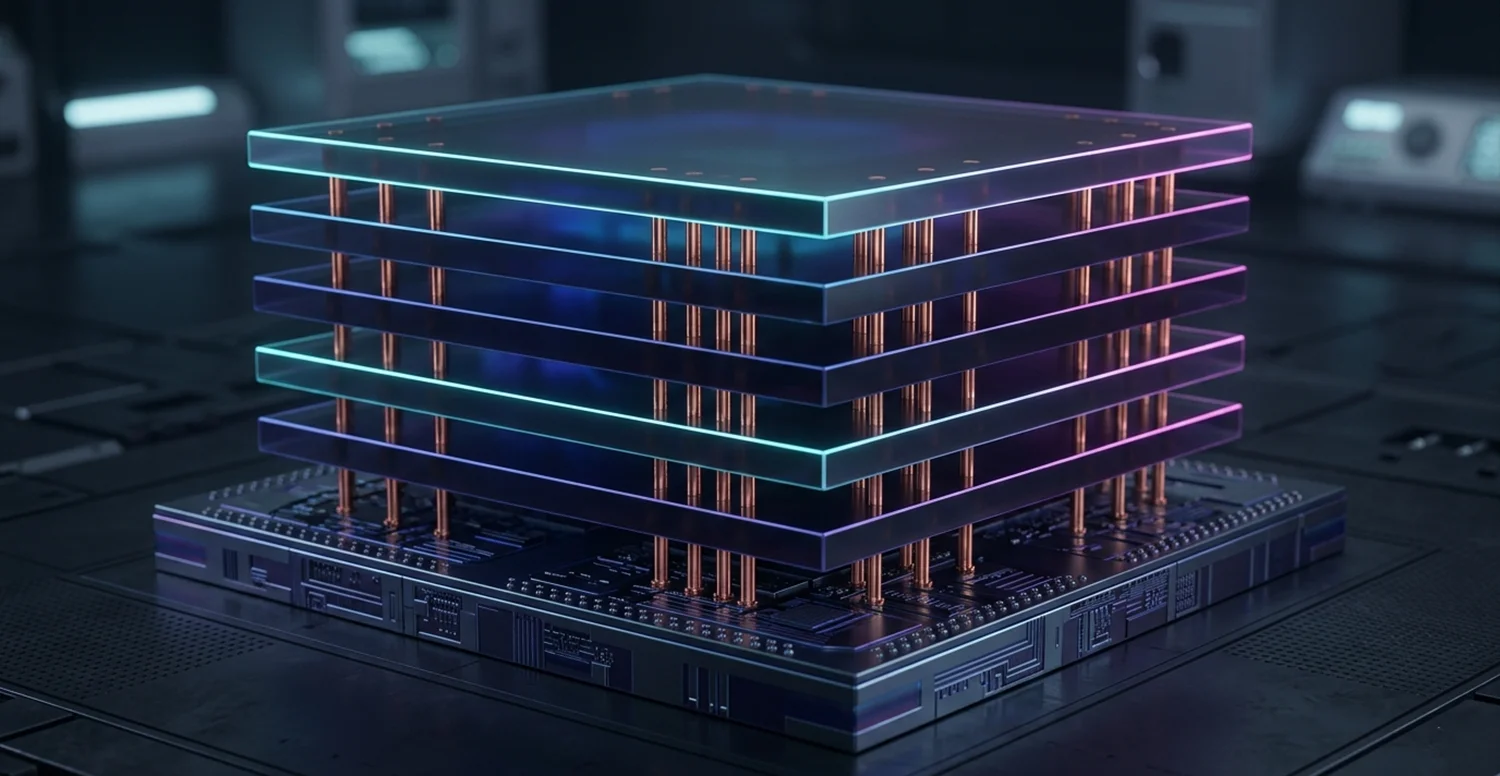

Mémoire à large bande passante was born to solve the “memory wall” problem by increasing memory bandwidth to unlock compute power. It adopts a design philosophy completely different from traditional memory—vertically stacking multiple DRAM chips and interconnecting them at high speed using Through-Silicon Via (TSV) technology, achieving massive data transfer width within an extremely small physical footprint. From the first-generation HBM in 2013 to today, this family has evolved over more than a decade, and HBM4 is its latest milestone.

HBM4 is the sixth-generation high-bandwidth memory technology, officially released as the JESD270-4 standard by JEDEC in April 2025. As the successor to HBM3/HBM3E, it is purpose-built for AI training, high-performance computing, and high-end data center GPUs. It continues the 3D stacked architecture of the HBM family, stacking multiple DRAM chips vertically and integrating them with a logic base die to achieve extremely high bandwidth density and compact packaging, earning it the industry nickname “super granary” for AI compute.

What Makes HBM4 So Powerful?

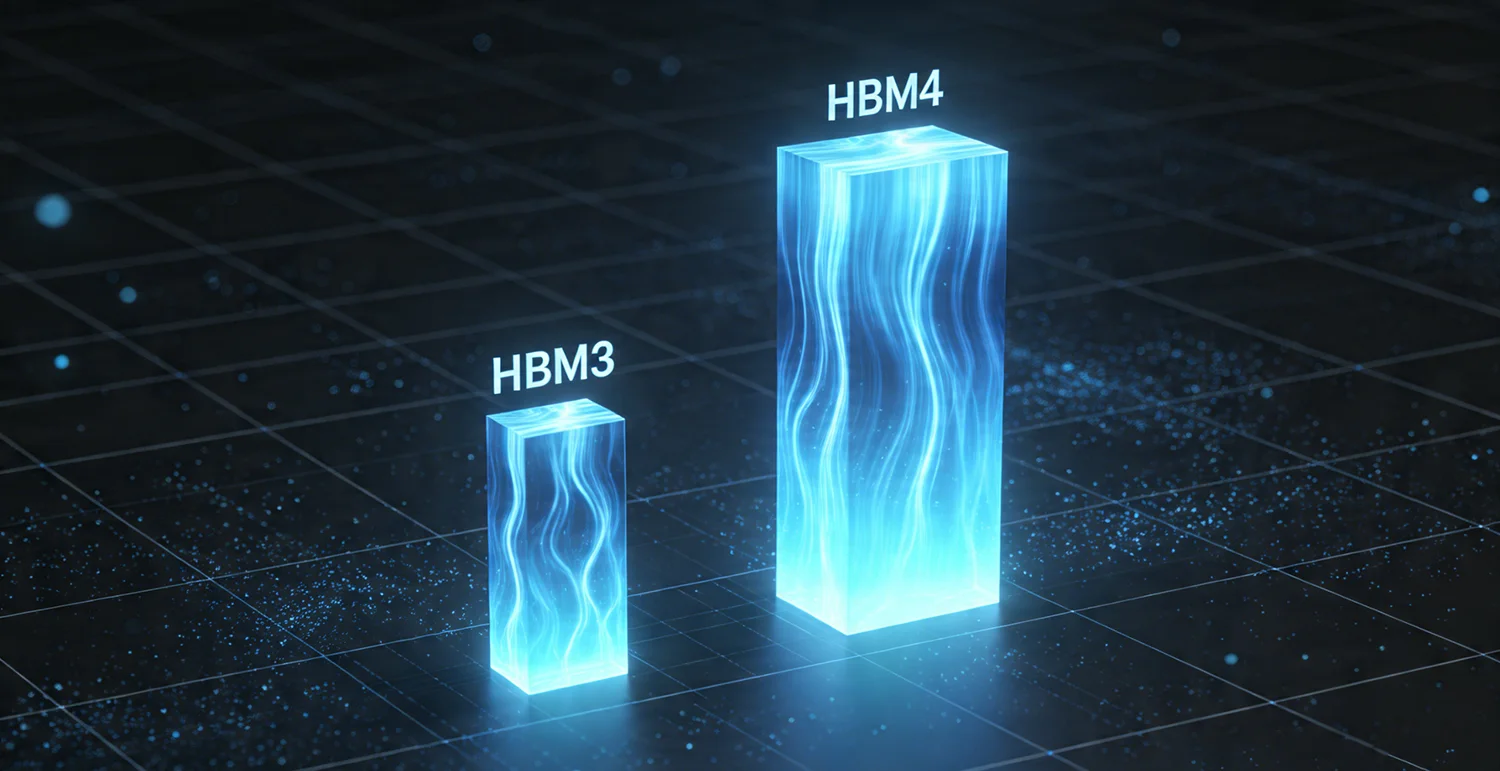

Compared to the previous generation HBM3E, HBM4 delivers a comprehensive performance leap. The table below gives you a quick look at the core changes:

| Spécifications | HBM3 | HBM4 | Improvement |

|---|---|---|---|

| Interface width | 1024 bit | 2048 bit | Doubled |

| Standard bandwidth | ~819 GB/s | 2 TB/s | ~2.4× |

| Independent channels | 16 | 32 | Doubled |

| Max capacity per stack | 24 GB (8-Hi) | 64 GB (16-Hi) | ~2.7× |

| Operating voltage | Fixed ~1.1V | VDDQ 0.7-0.9V, VDDC 1.0-1.05V | More flexible, more efficient |

Now let’s break down what these numbers really mean.

Wider Interface, Higher Bandwidth

HBM4 doubles the data interface per stack from 1024 bits to 2048 bits. What does this mean? The most advanced DDR5 memory today has a single-channel interface width of only 64 bits. That means one HBM4 stack has the equivalent bandwidth of 32 DDR5 channels working simultaneously. With the interface width doubled, total bandwidth automatically doubles even at the same data rate. And actual vendor products often run at higher speeds, so final bandwidth can easily exceed 2 TB/s, even reaching over 3 TB/s.

More Channels, More Flexible Data Scheduling

The number of channels increases from 16 to 32, and each channel includes two pseudo-channels. Channels can be thought of as independent “lanes” inside the memory—more channels mean the system can issue more memory access requests concurrently without interfering with each other. This is especially friendly to the massively parallel matrix operations in AI computing, significantly reducing access contention and improving effective bandwidth.

Larger Capacity, Holding the Entire Model

By increasing the DRAM stack layers from a maximum of 8 to 16, a single HBM4 memory stack can reach up to 64 GB. In actual products, an AI accelerator typically integrates 4 to 8 HBM stacks, meaning total memory capacity can easily exceed 256 GB or even 512 GB. For trillion-parameter large models, such capacity allows model parameters and intermediate results to reside entirely in high-speed memory, eliminating frequent transfers from slower VRAM or system memory.

Lower Voltage, Better Energy Efficiency

HBM4 introduces more refined voltage management. The I/O voltage VDDQ can be adjusted between 0.7V and 0.9V, and the core voltage VDDC can be selected between 1.0V and 1.05V. Lower voltages directly reduce power consumption. According to vendor data, HBM4’s energy per bit transferred is about 40% lower than HBM3E. For large data centers, this means lower electricity bills and reduced cooling demands.

New Security Feature: DRFM

HBM4 also adds an important reliability feature—Directed Refresh Management (DRFM). It effectively defends against “Row-Hammer” attacks, a security vulnerability where repeatedly and rapidly reading and writing adjacent memory rows causes bit flips in neighboring rows. DRFM intelligently identifies and selectively refreshes those rows, greatly enhancing memory security and data integrity.

What Are the Key Technical Breakthroughs in HBM4?

Hybrid Bonding

Hybrid bonding is seen as the next revolutionary solution in memory packaging. Traditional micro-bump technology uses micron-scale metal bumps to connect chips, with a pitch around 10μm—a physical limitation that prevents higher-density stacking and faster signal transmission. Hybrid bonding eliminates these bumps entirely, preparing the copper surfaces of two chips to be atomically flat and clean, then bringing them into direct contact so that copper atoms diffuse and fuse under temperature and pressure.

According to test data published by Samsung, hybrid bonding can shrink chip-to-chip interconnect pitch to below 10μm, increasing interconnect density by several times to tens of times, while delivering lower resistance, shorter signal paths, and better heat dissipation. Samsung’s measured data shows that bumpless hybrid bonding can increase HBM stack height by one-third and reduce thermal resistance by 20%. However, because hybrid bonding equipment is costly (roughly twice that of traditional bonders) and mass-production yield still needs improvement, this technology has not yet been applied to current volume-produced HBM4 products. Samsung has shipped 16-Hi HBM samples based on hybrid bonding to customers, with commercial adoption expected to begin gradually from HBM4E (the enhanced version of HBM4).

Distributed Interface and Pseudo-Channel Architecture

HBM4 adopts a design with 32 fully independent channels—twice that of HBM3—and each channel is equipped with 2 pseudo‑channels, supporting 32 DQ modes. The advantage of this distributed architecture is that it does not require all channels to operate synchronously. Each channel can handle data requests independently, dramatically improving parallel access efficiency. This is especially well-suited for tensor operations and irregular data access patterns in AI model training.

Compared to traditional memory’s single-channel design, HBM4’s multi-channel architecture is like expanding a single-lane highway into 32 independent multi‑lane highways, each capable of transmitting data efficiently at the same time—completely eliminating data traffic jams and enabling GPUs to more fully utilize their compute power.

Wide‑Interface, Low‑Power Design

HBM4 uses a strategy of “ultra‑wide interface + relatively low clock frequency” to achieve extremely high bandwidth while keeping power density low. Traditional memory often increases bandwidth by raising clock frequencies, which leads to sharply higher power consumption. HBM4 does the opposite: with a 2048‑bit wide data bus, it delivers several times the bandwidth of conventional memory at relatively modest frequencies. This design reduces HBM4’s energy per bit by 30‑40%, a significant advantage in the trend toward AI cost reduction and efficiency improvement.

Additionally, HBM4 supports vendor‑specific VDDQ voltage optimization (adjustable between 0.7V and 0.9V), further improving energy efficiency. This allows large‑scale data center deployments to effectively control total power and lower operational costs. At the same time, HBM4 maintains backward compatibility with HBM3 controllers—a single controller can support both memory generations, lowering the barrier for system upgrades.

HBM4 Progress and Roadmaps of the Three Giants

Samsung is the first manufacturer in the world to announce HBM4 mass production. Samsung Electronics announced on February 12, 2026, that it had started global first commercial mass production of HBM4 and begun customer shipments, using a 4nm logic die and 12‑Hi stacking technology, delivering an 11.7 Gbps data rate and 3.3 TB/s bandwidth—far exceeding JEDEC’s standard of 8 Gbps and 2 TB/s. Samsung plans to introduce HBM4E samples in the second half of 2026 for further performance improvements, while also developing a 16‑Hi stacked version that expands per‑stack capacity to 48 GB, paving the way for next‑generation AI accelerators.

SK Hynix is making rapid progress in the HBM4 space. According to its technology roadmap, it plans to launch a 16‑Hi stacked HBM4 product in 2026 with a capacity of 48 GB and a unified interface width upgrade to 2048 bits. Although the company is actively investing in next‑generation packaging technologies such as hybrid bonding, the 16‑Hi samples it has demonstrated so far still use its mature MR‑MUF technology. SK Hynix plans to ramp up volume production in 2026, working closely with major customers like NVIDIA and AMD.

Micron Technology has confirmed that its HBM4 memory entered mass production in the first quarter of 2026, with initial shipments being 36 GB 12‑Hi versions delivering over 2.8 TB/s of memory bandwidth. The product will be purpose‑built for NVIDIA’s Vera Rubin platform to support next‑generation data center AI training. This “customized on demand” strategy positions Micron favorably within specific customer segments.

How Will HBM4 Empower AI and High‑Performance Computing?

Driving Next‑Generation AI Accelerators

HBM4 has become the standard memory for next‑gen data center GPUs. Major AI chip vendors—NVIDIA, AMD, Intel—are all adopting HBM4 across their latest accelerator platforms. For example, on NVIDIA’s Vera Rubin platform, with eight HBM4 stacks, theoretical memory bandwidth could reach 22 TB/s, and with a starting memory capacity of 288 GB, it provides ample space and data channels for trillion‑parameter large model training. AMD’s next‑gen Instinct MI400 series also plans robust HBM4 configurations: the MI455X model will feature 12 HBM4 stacks, totaling 432 GB of capacity and 19.6 TB/s of bandwidth, targeting memory‑ and bandwidth‑intensive large‑scale AI training and inference tasks. Additionally, Intel’s next‑gen AI accelerator Jaguar Shores will also adopt HBM4 technology—while specific bandwidth and capacity figures have not been disclosed, joining the HBM4 ecosystem is a clear direction.

Enabling Large Model Training Without Memory Constraints

Generative AI training, especially for large language models with hundreds of billions or even trillions of parameters, is the core application scenario for HBM4. These models require simultaneous processing of massive parameter sets and data, placing extremely demanding requirements on memory bandwidth and capacity. The 288–384 GB of memory per accelerator card provided by HBM4 means that a single card can hold large model parameters and long context windows that previously required multiple cards working together. This eliminates the need to frequently partition data across cards during training, avoiding communication overhead and efficiency losses from model sharding, thereby significantly shortening training cycles. In actual AI service deployment, HBM4 can improve large model inference performance by more than 69%.

Accelerating Scientific Research and Simulation

In high‑performance computing, HBM4 provides critical infrastructure for scientific computing that requires massive data throughput. Whether it’s weather forecasting, quantum computing simulation, or genome sequencing analysis, all rely on high‑bandwidth, high‑capacity memory systems. Take weather forecasting: global weather stations, satellites, and radars generate vast amounts of real‑time data every moment. HBM4 can process these data streams quickly, allowing supercomputers to complete more detailed atmospheric model calculations in less time, thereby improving the accuracy and early warning speed of extreme weather predictions. In genome sequencing, HBM4 can simultaneously compare and analyze millions of genetic sequences, accelerating the identification of disease‑related genes and drug targets, saving valuable time for new drug development.

Expanding High‑End Graphics and Professional Visualization

Although consumer graphics cards today mainly use GDDR memory, the HBM series has always been a potential choice for professional graphics workstations and top‑tier gaming cards due to its ultra‑high bandwidth and low power consumption. As HBM4 mass‑production costs gradually decline, ordinary users might someday enjoy smoother, more efficient content creation experiences in scenarios like 8K gaming, real‑time rendering, and video editing. For professionals dealing with ultra‑high‑resolution video and complex 3D modeling, HBM4 will significantly reduce rendering wait times, making the creative process more fluid and natural.

HBM4, the sixth‑generation high‑bandwidth memory technology, achieves a dual leap in bandwidth and capacity through its 2048‑bit ultra‑wide interface, 32‑channel architecture, and hybrid bonding technology. It is a key memory solution for breaking through the “memory wall” bottleneck. Not only does it provide powerful storage support for AI training, high‑performance computing, and high‑end data center GPUs, it also marks the beginning of a new era where memory technology enters the age of hybrid bonding and 3D stacking. With the large‑scale commercialization of HBM4 and the continued maturation of its technology, we have every reason to believe that AI compute power will see a new burst of growth, unlocking more cutting‑edge technologies and application scenarios, and bringing tremendous changes to the development of human society.