En la actual era de la inteligencia artificial y la computación de alto rendimiento, el ancho de banda de la memoria se ha convertido en un cuello de botella crítico que limita la capacidad de cálculo, lo que la industria suele denominar el problema del “muro de memoria”. Imaginemos la capacidad de cálculo de la GPU como una cadena de montaje de una superfábrica, mientras que la memoria tradicional sólo proporciona un estrecho “conducto de suministro de materia prima”, lo que deja los costosos recursos de cálculo parados y a la espera de datos. Este es el principal reto al que se enfrenta el entrenamiento de la IA en la actualidad. HBM4 (High Bandwidth Memory 4) está aquí para acabar con este cuello de botella de una vez por todas, proporcionando la columna vertebral de almacenamiento esencial para la explosión de computación impulsada por la IA.

¿Qué es HBM4?

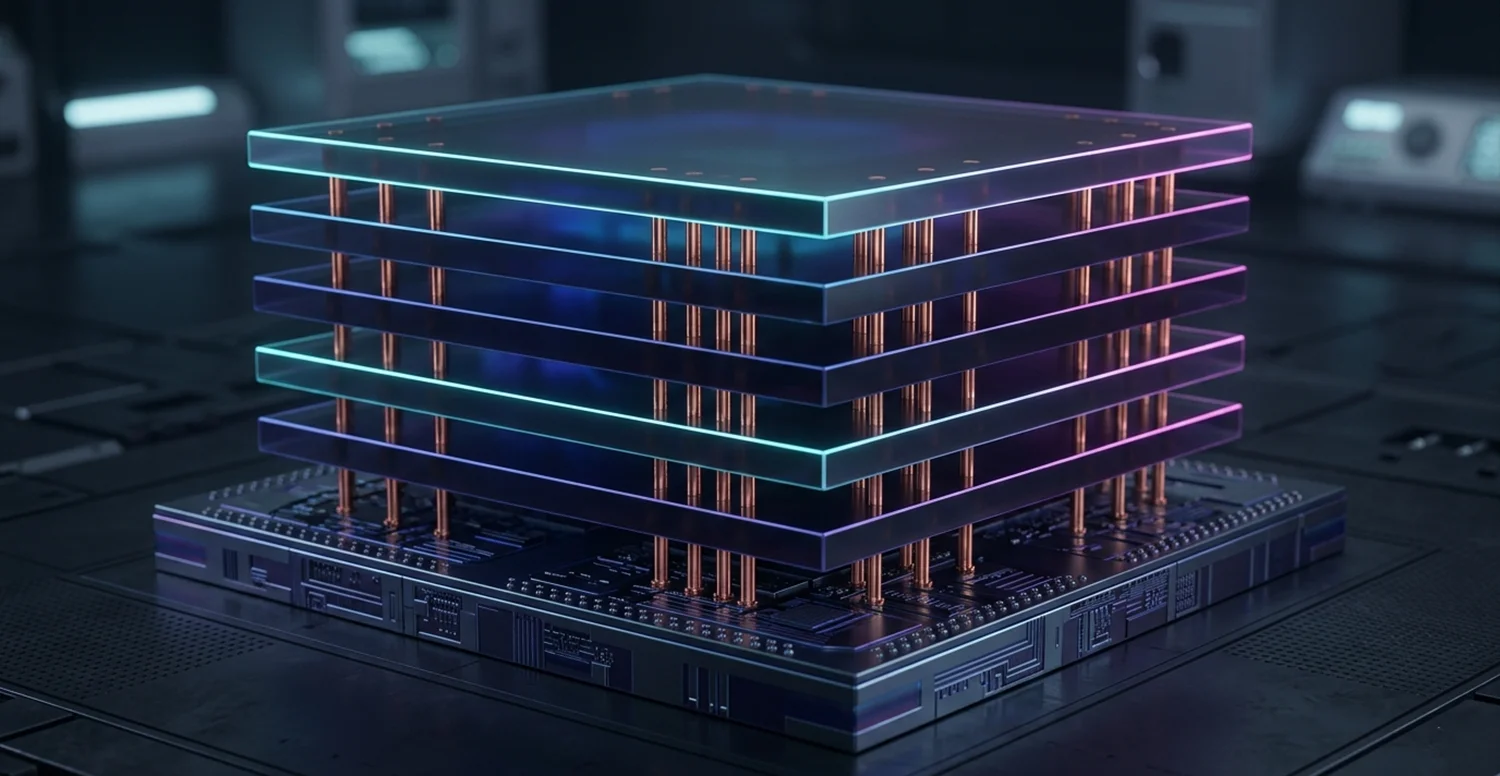

Memoria de gran ancho de banda nació para resolver el problema del “muro de memoria” aumentando el ancho de banda de la memoria para liberar potencia de cálculo. Adopta una filosofía de diseño completamente distinta a la de las memorias tradicionales: apila verticalmente varios chips DRAM y los interconecta a alta velocidad mediante la tecnología TSV (Through-Silicon Via), con lo que consigue una enorme anchura de transferencia de datos en un espacio físico extremadamente reducido. Desde la primera generación de HBM en 2013 hasta hoy, esta familia ha evolucionado a lo largo de más de una década, y HBM4 es su último hito.

HBM4 es la tecnología de memoria de gran ancho de banda de sexta generación, lanzada oficialmente como la Norma JESD270-4 por el JEDEC en abril de 2025. Como sucesora de HBM3/HBM3E, está diseñada para el entrenamiento de inteligencia artificial, la computación de alto rendimiento y las GPU de centros de datos de gama alta. Continúa la arquitectura apilada en 3D de la familia HBM, apilando varios chips DRAM verticalmente e integrándolos con un chip lógico base para lograr una densidad de ancho de banda extremadamente alta y un empaquetado compacto, lo que le ha valido el sobrenombre de “supergranero” para la computación de IA.

¿Qué hace que HBM4 sea tan potente?

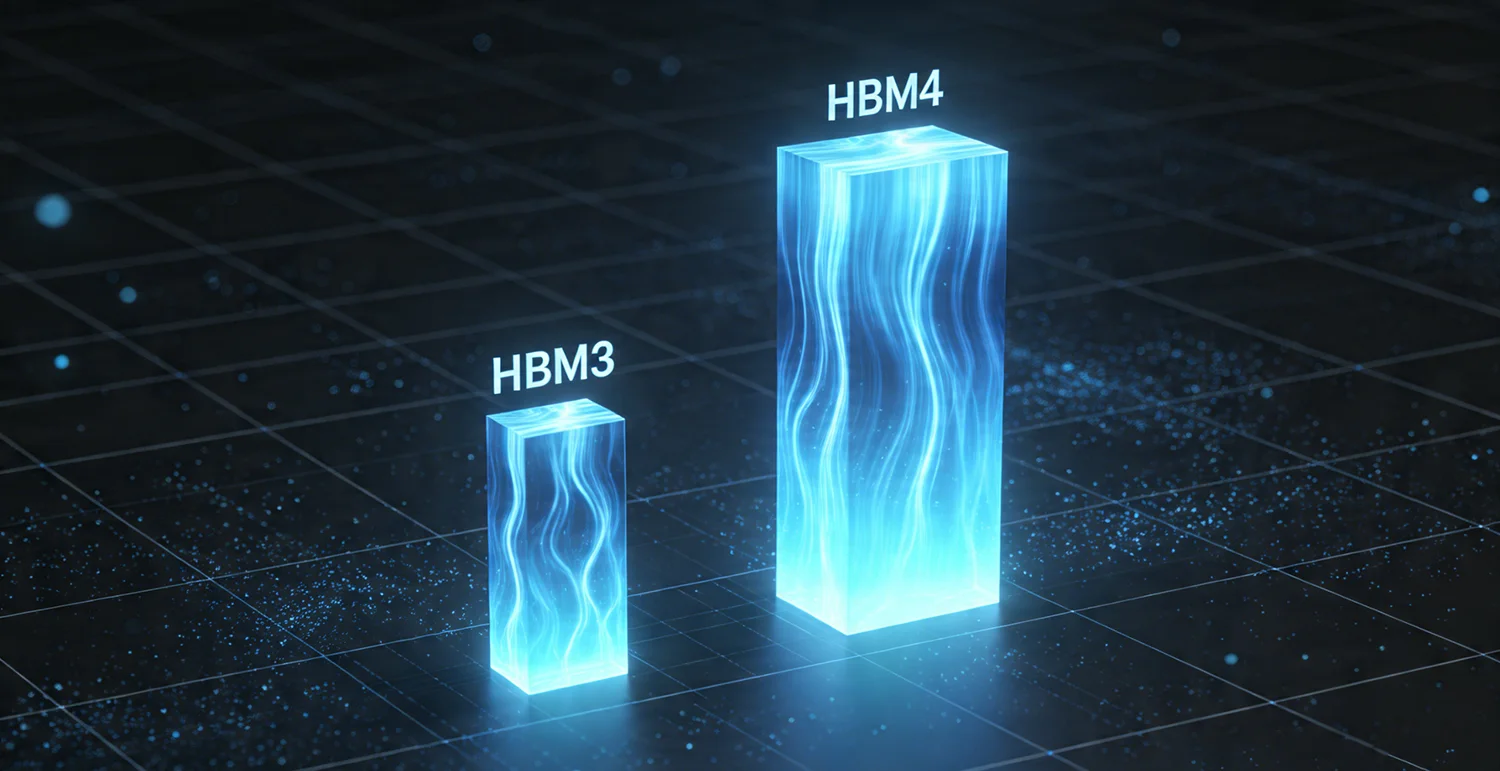

En comparación con la generación anterior HBM3E, HBM4 ofrece un salto de rendimiento integral. La tabla siguiente ofrece un resumen de los principales cambios:

| Especificación | HBM3 | HBM4 | Mejora |

|---|---|---|---|

| Anchura de interfaz | 1024 bits | 2048 bits | Doble |

| Ancho de banda estándar | ~819 GB/s | 2 TB/s | ~2.4× |

| Canales independientes | 16 | 32 | Doble |

| Capacidad máxima por pila | 24 GB (8-Hi) | 64 GB (16-Hi) | ~2.7× |

| Tensión de funcionamiento | Fijo ~1,1V | VDDQ 0,7-0,9V, VDDC 1,0-1,05V | Más flexible, más eficaz |

Veamos ahora qué significan realmente estas cifras.

Interfaz más amplia, mayor ancho de banda

HBM4 duplica la interfaz de datos por pila de 1024 bits a 2048 bits. ¿Qué significa esto? La memoria DDR5 más avanzada de la actualidad tiene un ancho de interfaz de un solo canal de sólo 64 bits. Esto significa que una pila HBM4 tiene el ancho de banda equivalente a 32 canales DDR5 funcionando simultáneamente. Al duplicarse la anchura de la interfaz, el ancho de banda total se duplica automáticamente incluso a la misma velocidad de datos. Y los productos reales de los fabricantes suelen funcionar a velocidades superiores, por lo que el ancho de banda final puede superar fácilmente los 2 TB/s, llegando incluso a superar los 3 TB/s.

Más canales, programación de datos más flexible

El número de canales aumenta de 16 a 32, y cada canal incluye dos pseudocanales. Se puede pensar en los canales como “carriles” independientes dentro de la memoria: un mayor número de canales significa que el sistema puede emitir más solicitudes de acceso a la memoria de forma simultánea sin interferir entre sí. Esto es especialmente beneficioso para las operaciones matriciales masivamente paralelas de la informática de IA, ya que reduce significativamente la contención de acceso y mejora el ancho de banda efectivo.

Mayor capacidad para todo el modelo

Al aumentar las capas de la pila DRAM de un máximo de 8 a 16, una sola pila de memoria HBM4 puede alcanzar hasta 64 GB. En los productos reales, un acelerador de IA suele integrar de 4 a 8 pilas HBM, lo que significa que la capacidad total de memoria puede superar fácilmente los 256 GB o incluso los 512 GB. Para modelos de billones de parámetros de gran tamaño, esta capacidad permite que los parámetros del modelo y los resultados intermedios residan por completo en la memoria de alta velocidad, lo que elimina las frecuentes transferencias desde la VRAM o la memoria del sistema, más lentas.

Menor voltaje, mayor eficiencia energética

HBM4 introduce una gestión del voltaje más refinada. La tensión de E/S VDDQ puede ajustarse entre 0,7V y 0,9V, y la tensión del núcleo VDDC puede seleccionarse entre 1,0V y 1,05V. Los voltajes más bajos reducen directamente el consumo de energía. Según datos del fabricante, la energía por bit transferido de HBM4 es aproximadamente 40% inferior a la de HBM3E. Para los grandes centros de datos, esto se traduce en una reducción de la factura eléctrica y de la demanda de refrigeración.

Nuevo dispositivo de seguridad: DRFM

HBM4 también añade una importante función de fiabilidad: la gestión de refresco dirigida (DRFM). Defiende eficazmente contra los ataques “Row-Hammer”, una vulnerabilidad de seguridad en la que la lectura y escritura rápida y repetida de filas de memoria adyacentes provoca cambios de bits en las filas vecinas. DRFM identifica de forma inteligente y actualiza selectivamente esas filas, lo que mejora enormemente la seguridad de la memoria y la integridad de los datos.

¿Cuáles son los principales avances técnicos de HBM4?

Vinculación híbrida

La unión híbrida se considera la próxima solución revolucionaria para el empaquetado de memorias. La tecnología tradicional de microbump utiliza protuberancias metálicas a escala micrométrica para conectar los chips, con un paso de unos 10μm, una limitación física que impide un apilamiento de mayor densidad y una transmisión de señales más rápida. La unión híbrida elimina por completo estas protuberancias, preparando las superficies de cobre de dos chips para que sean atómicamente planas y limpias, y luego poniéndolas en contacto directo para que los átomos de cobre se difundan y fusionen bajo temperatura y presión.

Según los datos de las pruebas publicadas por Samsung, la unión híbrida puede reducir el paso de interconexión chip a chip por debajo de 10μm, lo que aumenta la densidad de interconexión entre varias y decenas de veces, al tiempo que ofrece menor resistencia, rutas de señal más cortas y mejor disipación del calor. Los datos medidos por Samsung muestran que la unión híbrida sin bola puede aumentar la altura de la pila HBM en un tercio y reducir la resistencia térmica en 20%. Sin embargo, como el equipo de unión híbrida es costoso (aproximadamente el doble que el de las uniones tradicionales) y el rendimiento de la producción en masa aún debe mejorar, esta tecnología aún no se ha aplicado a los productos HBM4 producidos en serie. Samsung ha enviado a sus clientes muestras de HBM 16-Hi basadas en la unión híbrida, y se espera que la adopción comercial comience gradualmente a partir de HBM4E (la versión mejorada de HBM4).

Interfaz distribuida y arquitectura de pseudocanales

HBM4 adopta un diseño con 32 canales totalmente independientes -el doble que HBM3- y cada canal está equipado con 2 pseudocanales, que admiten 32 modos DQ. La ventaja de esta arquitectura distribuida es que no requiere que todos los canales funcionen de forma sincrónica. Cada canal puede gestionar las peticiones de datos de forma independiente, lo que mejora notablemente la eficiencia del acceso paralelo. Esto es especialmente adecuado para operaciones tensoriales y patrones irregulares de acceso a datos en el entrenamiento de modelos de IA.

En comparación con el diseño monocanal de la memoria tradicional, la arquitectura multicanal de HBM4 es como ampliar una autopista de un solo carril en 32 autopistas independientes de varios carriles, cada una de ellas capaz de transmitir datos de forma eficiente al mismo tiempo, lo que elimina por completo los atascos de datos y permite a las GPU aprovechar mejor su capacidad de cálculo.

Diseño de bajo consumo y amplia interfaz

HBM4 utiliza una estrategia de “interfaz ultraancha + frecuencia de reloj relativamente baja” para conseguir un ancho de banda extremadamente alto manteniendo baja la densidad de potencia. Las memorias tradicionales suelen aumentar el ancho de banda incrementando las frecuencias de reloj, lo que conlleva un consumo muy superior. HBM4 hace lo contrario: con un bus de datos de 2048 bits de ancho, ofrece varias veces el ancho de banda de la memoria convencional a frecuencias relativamente modestas. Este diseño reduce la energía por bit de HBM4 en 30-40%, una ventaja significativa en la tendencia hacia la reducción de costes y la mejora de la eficiencia de la IA.

Además, HBM4 admite la optimización del voltaje VDDQ específica del proveedor (ajustable entre 0,7 V y 0,9 V), lo que mejora aún más la eficiencia energética. Esto permite a los centros de datos a gran escala controlar eficazmente la potencia total y reducir los costes operativos. Al mismo tiempo, HBM4 mantiene la retrocompatibilidad con los controladores HBM3: un único controlador puede admitir ambas generaciones de memoria, lo que reduce la barrera para las actualizaciones del sistema.

HBM4 Progresos y hojas de ruta de los tres gigantes

Samsung es el primer fabricante del mundo en anunciar la producción en masa de HBM4. Samsung Electronics anunció el 12 de febrero de 2026 que había iniciado la primera producción comercial masiva mundial de HBM4 y comenzado los envíos a los clientes, utilizando una matriz lógica de 4 nm y una tecnología de apilamiento de 12 Hi, que proporciona una velocidad de datos de 11,7 Gbps y un ancho de banda de 3,3 TB/s, superando con creces la norma JEDEC de 8 Gbps y 2 TB/s. Samsung planea introducir muestras de HBM4E en la segunda mitad de 2026 para mejorar aún más el rendimiento, al tiempo que desarrolla una versión apilada de 16 Hi que amplía la capacidad por pila a 48 GB, allanando el camino para los aceleradores de IA de próxima generación.

SK Hynix avanza rápidamente en el campo de la HBM4. Según su hoja de ruta tecnológica, tiene previsto lanzar un producto HBM4 apilado de 16 Hi en 2026 con una capacidad de 48 GB y una actualización del ancho de interfaz unificado a 2048 bits. Aunque la empresa está invirtiendo activamente en tecnologías de empaquetado de nueva generación, como la unión híbrida, las muestras de 16 Hi que ha mostrado hasta ahora siguen utilizando su madura tecnología MR-MUF. SK Hynix tiene previsto aumentar la producción en serie en 2026, en estrecha colaboración con grandes clientes como NVIDIA y AMD.

Micron Technology ha confirmado que su memoria HBM4 entró en producción masiva en el primer trimestre de 2026, con envíos iniciales de versiones de 36 GB 12-Hi que ofrecen más de 2,8 TB/s de ancho de banda de memoria. El producto se fabricará específicamente para la plataforma Vera Rubin de NVIDIA, destinada al entrenamiento de IA en centros de datos de última generación. Esta estrategia de “personalización bajo demanda” posiciona a Micron favorablemente en segmentos específicos de clientes.

¿Cómo potenciará HBM4 la IA y la informática de alto rendimiento?

Impulsar los aceleradores de IA de nueva generación

HBM4 se ha convertido en la memoria estándar para las GPU de los centros de datos de última generación. Los principales fabricantes de chips de IA -NVIDIA, AMD e Intel- están adoptando HBM4 en sus últimas plataformas aceleradoras. Por ejemplo, en la plataforma Vera Rubin de NVIDIA, con ocho pilas de HBM4, el ancho de banda teórico de la memoria podría alcanzar los 22 TB/s y, con una capacidad de memoria inicial de 288 GB, proporciona amplio espacio y canales de datos para el entrenamiento de modelos de un billón de parámetros de gran tamaño. La próxima generación de la serie Instinct MI400 de AMD también prevé potentes configuraciones HBM4: el modelo MI455X incluirá 12 pilas HBM4, con un total de 432 GB de capacidad y 19,6 TB/s de ancho de banda, dirigidas a tareas de formación e inferencia de IA a gran escala que requieran mucha memoria y ancho de banda. Además, el acelerador de IA de próxima generación Jaguar Shores de Intel también adoptará la tecnología HBM4; aunque no se han revelado las cifras concretas de ancho de banda y capacidad, unirse al ecosistema HBM4 es una dirección clara.

Entrenamiento de modelos de gran tamaño sin limitaciones de memoria

El entrenamiento generativo de la IA, especialmente para modelos lingüísticos de gran tamaño con cientos de miles de millones o incluso billones de parámetros, es el principal escenario de aplicación de HBM4. Estos modelos requieren el procesamiento simultáneo de enormes conjuntos de parámetros y datos, lo que impone requisitos muy exigentes en cuanto a ancho de banda y capacidad de memoria. Los 288-384 GB de memoria por tarjeta aceleradora que proporciona HBM4 significan que una sola tarjeta puede contener grandes parámetros de modelos y largas ventanas de contexto que antes requerían el trabajo conjunto de varias tarjetas. Esto elimina la necesidad de dividir con frecuencia los datos entre las tarjetas durante el entrenamiento, evitando la sobrecarga de comunicación y las pérdidas de eficiencia derivadas de la fragmentación de modelos, lo que acorta considerablemente los ciclos de entrenamiento. En el despliegue real de servicios de IA, HBM4 puede mejorar el rendimiento de inferencia de grandes modelos en más de 69%.

Acelerar la investigación científica y la simulación

En la computación de alto rendimiento, HBM4 proporciona una infraestructura crítica para la computación científica que requiere un caudal de datos masivo. Ya se trate de predicciones meteorológicas, simulación de computación cuántica o análisis de secuenciación genómica, todo depende de sistemas de memoria de gran capacidad y ancho de banda. Por ejemplo, las estaciones meteorológicas, los satélites y los radares generan enormes cantidades de datos en tiempo real a cada instante. HBM4 puede procesar estos flujos de datos con rapidez, lo que permite a los superordenadores completar cálculos más detallados de modelos atmosféricos en menos tiempo, mejorando así la precisión y la velocidad de alerta temprana de las predicciones meteorológicas extremas. En la secuenciación del genoma, HBM4 puede comparar y analizar simultáneamente millones de secuencias genéticas, acelerando la identificación de genes relacionados con enfermedades y dianas farmacológicas, lo que ahorra un tiempo valioso para el desarrollo de nuevos fármacos.

Expansión de los gráficos de gama alta y la visualización profesional

Aunque hoy en día las tarjetas gráficas de consumo utilizan principalmente memoria GDDR, la serie HBM siempre ha sido una opción potencial para las estaciones de trabajo gráficas profesionales y las tarjetas de juego de gama alta por su altísimo ancho de banda y su bajo consumo de energía. A medida que los costes de producción en serie de HBM4 disminuyan gradualmente, los usuarios de a pie podrán disfrutar algún día de experiencias de creación de contenidos más fluidas y eficientes en escenarios como los juegos 8K, el renderizado en tiempo real y la edición de vídeo. Para los profesionales que trabajan con vídeo de altísima resolución y modelado 3D complejo, HBM4 reducirá significativamente los tiempos de espera de renderizado, haciendo que el proceso creativo sea más fluido y natural.

HBM4, la tecnología de memoria de gran ancho de banda de sexta generación, consigue un doble salto en ancho de banda y capacidad gracias a su interfaz ultraancha de 2048 bits, su arquitectura de 32 canales y su tecnología de enlace híbrido. Es una solución de memoria clave para romper el cuello de botella del “muro de memoria”. No sólo proporciona un potente soporte de almacenamiento para la formación en IA, la computación de alto rendimiento y las GPU de centros de datos de gama alta, sino que también marca el comienzo de una nueva era en la que la tecnología de memoria entra en la era de la unión híbrida y el apilamiento 3D. Con la comercialización a gran escala de HBM4 y la continua maduración de su tecnología, tenemos todos los motivos para creer que la potencia de cálculo de la IA experimentará un nuevo estallido de crecimiento, desbloqueando más tecnologías de vanguardia y escenarios de aplicación, y aportando enormes cambios al desarrollo de la sociedad humana.