大規模言語モデル、ジェネレーティブAI、ハイパフォーマンス・コンピューティング(HPC)の急速な発展により、従来のメモリ・アーキテクチャは物理的な限界に達している。 高い 帯域幅メモリー(HBM) しかし、スタックの高さと密度が上がるにつれて、容量、消費電力、熱管理のボトルネックが大きくなっている。

2026年2月初旬、 Zアングルメモリー(ZAM) は、このような課題を解決するための専用ソリューションとして登場しました。インテルとソフトバンクの完全子会社であるSAIMEMORYが共同開発したZAMは、データ集約型ワークロードのメモリ・スケーリングを再定義するために設計された次世代スタック型DRAMアーキテクチャである。

Zアングル・メモリーとは

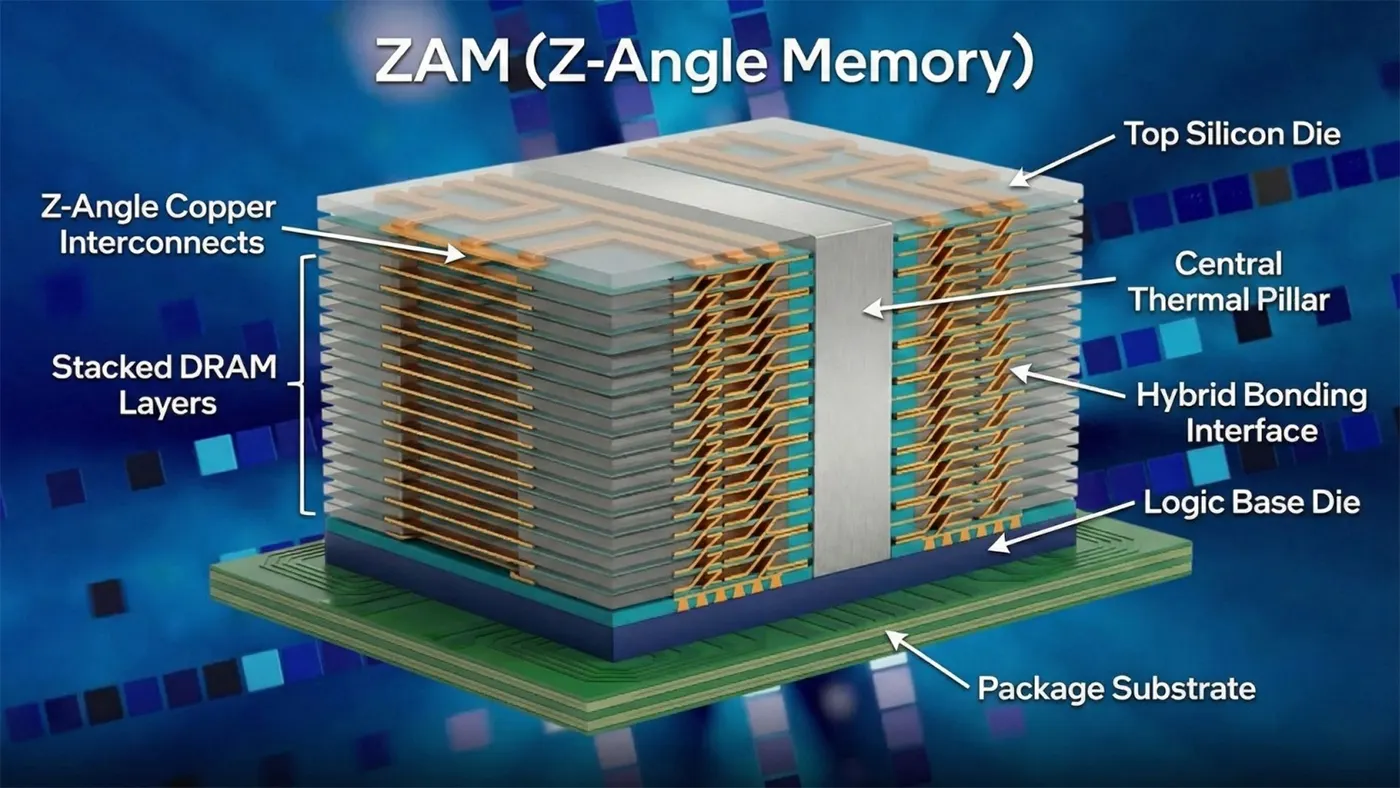

Zアングルメモリー(ZAM) は、従来のHBMのスケーリング限界を克服するために構築された3Dスタック型DRAMアーキテクチャです。その名前は、決定的な革新技術である 斜めZ型相互接続トポロジー これは、現在のすべてのHBM設計で使用されている垂直シリコン貫通ビア(TSV)に代わるものである。

信号を上下にまっすぐ配線する従来のメモリ・スタックとは異なり、ZAMはスタック内のデータ移動に斜めの千鳥配線を使用している。この小さな、しかし抜本的な変更により、3つの重要なペインポイントに対処している: 大規模なAIモデルのための不十分な容量、データセンターでの過剰な電力消費、高密度パッケージでの手に負えない熱の蓄積。 ZAMはインクリメンタル・アップグレードではない。スタックド・メモリのグランドアップ再設計であり、2030年のAIデータセンターとHPCシステムへの商用展開を目標としている。

コア技術革新

ZAMの性能向上は、緊密に統合された5つの技術的ブレークスルーによるもので、それぞれが現代の半導体製造ルールの中で機能するように設計されている。

対角相互接続トポロジー。 ZAMの基盤は、垂直TSVから千鳥配置の斜めインターコネクトへの移行である。この構造は、機械的ストレスと熱を狭い縦列に集中させるのではなく、スタック全体に均等に分散させる。また、平均的な信号経路を短縮し、レイテンシーと電力損失を低減する。

銅と銅のハイブリッド・ボンディング。 ZAM は、従来のマイクロバンプとはんだ接続を、銅と銅のハイブリッド直接接合に置き換えます。この原子レベルの接続は抵抗とインダクタンスを下げ、シグナル・インテグリティを改善し、スタックが一連のディスクリート・ダイではなく、単一のモノリシック・シリコン・ブロックのように動作することを可能にします。

ビア・イン・ワン・マニュファクチャリング。 ZAMは、簡素化されたビア・イン・ワン・プロセスを使用し、対角相互接続を1回の製造工程で形成します。これにより、HBMに必要な多段階のTSVプロセスに比べ、製造の複雑さを軽減し、歩留まりを向上させ、製造コストを削減します。

コンデンサーレス設計。 ZAMはオンダイ・キャパシタを完全に排除する。これにより、メモリ・セル用に貴重なシリコン・エリアが解放され、プロセス・ノードを縮小することなく、ストレージ密度を直接的に高めることができる。また、チップ設計を簡素化し、電気効率を向上させます。

EMIBの統合。 ZAMはインテルの エンベデッド・マルチ・ダイ・インターコネクト・ブリッジ(EMIB) パッケージングされる。これにより、ZAMスタックとAIプロセッサー間の高速で低レイテンシーの接続が可能になり、まとまりのある高性能なコンピュート・コンプレックスが実現します。

ZAM対HBM

以下の表は、公表されているプロトタイプと設計目標を用いて、ZAMが広く展開されているHBM3eおよび今後予定されているHBM4ソリューションと比較した結果をまとめたものです。

| メートル | ザム | HBM3e(現行) | HBM4(予定) |

|---|---|---|---|

| スタックあたりの容量 | 最大512GB | 24-36GB | 24-48GB |

| 最大スタックレイヤー | 50層以上 | 12~16層 | 16~20層 |

| 消費電力 | HBM3eより低い40-50% | ベースライン | ~HBM3eより20%低い |

| 相互接続タイプ | 対角Zアングル銅 | 垂直TSV | 垂直TSV |

| 熱性能 | 中央の熱柱;ホットスポットが少ない | 高層のホットスポット | 中程度の改善 |

| 対象ユースケース | 大規模AIトレーニング、HPC | クラウドAI推論 | 中規模から大規模のAIワークロード |

ZAMの主な利点

比類なきメモリー容量。 ZAMが提供 2~3倍の容量 スタックあたり512GBを目標としています。これにより、より大きな基盤モデルをより少ないアクセラレータで実行できるようになり、システム設計が簡素化され、総所有コストが削減される。

劇的な電力効率。 電力使用量は次のように削減される。 40-50% HBM3eと比較して大規模なAIクラスタでは、エネルギーコストの削減、冷却需要の低減、持続可能性目標の達成に役立ちます。

優れた熱管理。 従来のHBMは、熱ボトルネックのため、およそ16~20層が上限でした。ZAMの斜め配線は、スタック全体に熱を分散させる中央の熱柱を作り出し、信頼性の高い積層を可能にします。 50層以上 危険なホットスポットがない。

強化された機械的安定性。 斜めの相互接続はダイ全体に均等に応力を分散し、背の高いスタックでの反りや故障のリスクを低減します。これにより、企業やデータセンター環境における長期信頼性が向上します。

製造の簡素化。 ビア・イン・ワン・プロセスとコンデンサレス設計により、生産が効率化される。初期の見積もりでは、ZAMは複雑なHBMスタックよりも低コストで製造できる一方、はるかに大容量を実現できるとされている。

開発背景と業界パートナーシップ

このテクノロジーは、インテルの 次世代DRAMボンディング(NGDB) プログラムは、米国エネルギー省の先進メモリ技術(AMT)プロジェクトとサンディア国立研究所の支援を受けて開発された。この研究は、従来のDRAMを制限していた電力-容量-帯域幅のトレードオフを解消することに焦点を当てたものです。

SAIMEMORYは、ソフトバンクの子会社として2024年12月に設立され、AIのための次世代メモリを開発することを唯一の使命としている。インテルとSAIMEMORYの正式なパートナーシップは、以下の通り発表された。 2026年2月2日で、ZAMはその1日後に世界的なプロトタイプデビューを飾った。 インテル コネクション ジャパン 2026.この協力関係の下、インテルは高度なパッケージングとボンディングの専門知識を提供し、サイメモリはアーキテクチャ開発と商業化を主導する。

実際の使用例

ZAMは、現代のコンピューティングにおいて最も要求の厳しいワークロードのために設計されている:

- 大規模AIモデルトレーニング。 スタックあたりの大容量により、数兆パラメータの基礎モデルのメモリボトルネックが解消され、より高速なトレーニングとシンプルなクラスタ設計が可能になります。

- クラウドAIによる大規模推論。 消費電力の低減は、継続的な推論ワークロードを実行するハイパースケールクラウドプロバイダーの運用コストを削減します。

- 高性能コンピューティング。 科学シミュレーション、気象モデリング、金融モデリングは、大容量と安定した低レイテンシのメモリアクセスから恩恵を受けます。

- CXL メモリ・プーリング。 ZAMの効率的なスタッキングと広帯域幅は、コンピュート・エクスプレス・リンク(CXL)メモリー・プーリングに自然に適合し、最新のデータセンターで柔軟な共有メモリー・リソースを可能にする。

- エッジAIと自律システム。 電力効率の向上は、産業オートメーションから自律走行車まで、電力に制約のあるエッジ環境におけるAIの展開をサポートする。

現状と今後のスケジュール

2026年初頭現在、ZAMは明確なロードマップを公開し、活発な開発を続けている:

- 2026年2月:インテル・コネクション・ジャパンで初のプロトタイプ・デモンストレーション。

- 2027:エンジニアリングサンプルとテストチップは、ハードウェアパートナーにリリースされる予定。

- 2030:AIデータセンターとHPCシステムの大量商業展開を目指す。

このプラットフォームはまだ改良中だが、初期のプロトタイプの結果は、容量、消費電力、熱性能に関する中核的な主張を検証している。ZAMは、2030年以降のAIメモリ状況において、HBMの後継となる有力候補として広く見られている。

Z-Angleメモリは、スタック型DRAM設計におけるパラダイムシフトを象徴しています。垂直TSVを斜めのZ型インターコネクト・トポロジーに置き換えることで、HBMの最も根強い制約に取り組んでいる。しかし、AIメモリの競争環境はダイナミックだ。サムスンが最近発表したzHBMのようなライバル技術も、積極的な性能主張を掲げてポストHBM4時代を狙っている。さらに、どのような新しいメモリー・アーキテクチャーの商業化も、高い製造歩留まり、競争力のあるコスト構造、そして重要なのは主要なAIアクセラレーターやシステム・ベンダーによる採用の達成にかかっている。したがって、ZAMは魅力的な青写真を提示しているが、プロトタイプから業界標準への道のりは、これらの現実的なエンジニアリングとエコシステムの課題を克服することが条件となる。