لقد أدى النمو السريع لنماذج اللغات الكبيرة والذكاء الاصطناعي التوليدي والحوسبة عالية الأداء (HPC) إلى دفع بنيات الذاكرة التقليدية إلى أقصى حدودها المادية. عالية ذاكرة النطاق الترددي (HBM) لطالما كان المعيار الذهبي لمسرعات الذكاء الاصطناعي، ولكنه يواجه معوقات متزايدة في السعة واستهلاك الطاقة والإدارة الحرارية مع ارتفاع ارتفاع ارتفاعات المكدسات وكثافتها.

في أوائل فبراير 2026, ذاكرة الزاوية Z-زاوية (ZAM) ظهرت كحل مصمم لهذا الغرض لمواجهة هذه التحديات. تم تطوير ZAM بالاشتراك بين Intel وSAIMEMEMORY، وهي شركة تابعة مملوكة بالكامل لشركة SoftBank Corp. ZAM هي بنية DRAM مكدسة من الجيل التالي مصممة لإعادة تعريف توسيع نطاق الذاكرة لأعباء العمل كثيفة البيانات.

ما هي ذاكرة الزاوية Z- الزاوية

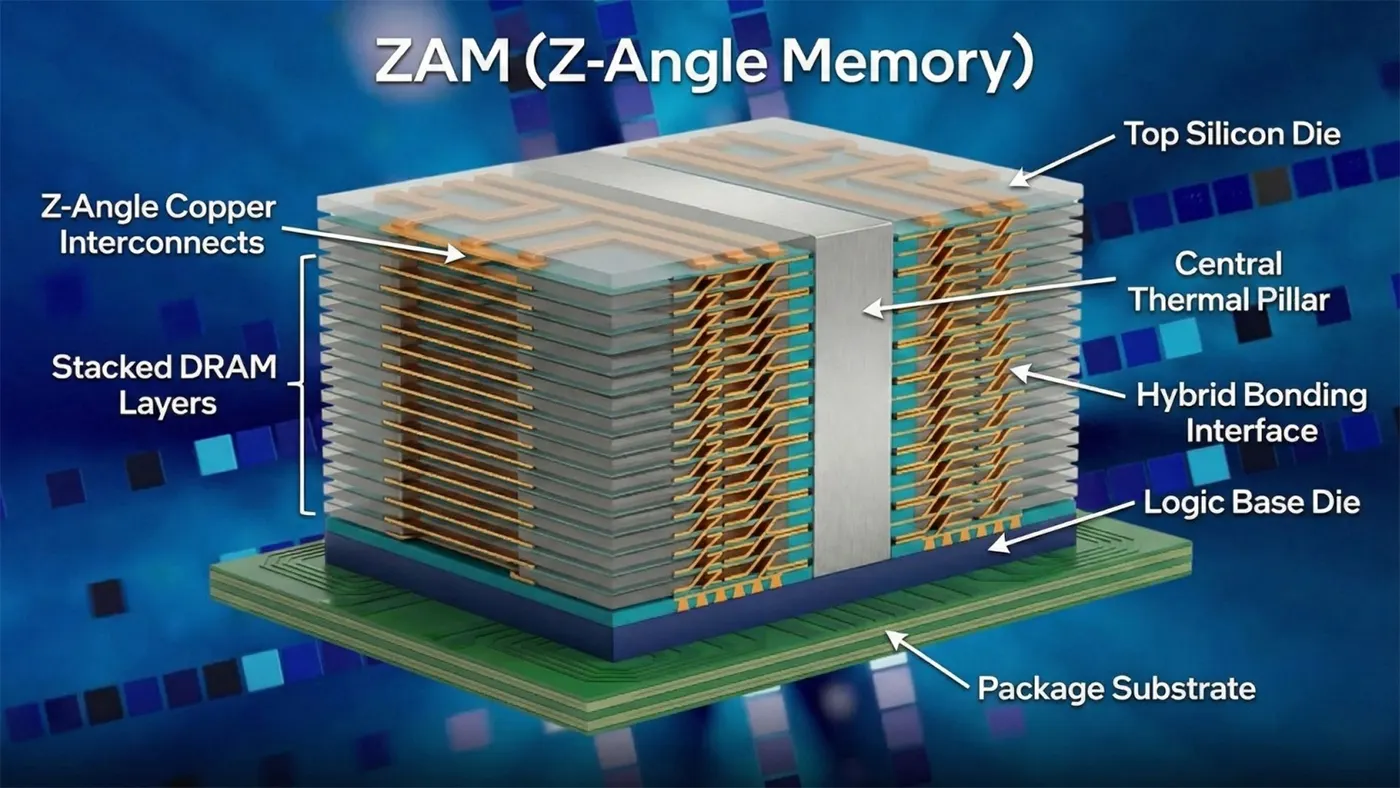

ذاكرة الزاوية Z-زاوية (ZAM) هي عبارة عن بنية DRAM مكدسة ثلاثية الأبعاد مصممة للتغلب على حدود التوسع في HBM التقليدية. ويأتي اسمها من ابتكارها المميز: وهي عبارة عن طوبولوجيا الوصلة البينية القطرية على شكل حرف Z التي تحل محل الشقوق العمودية عبر السيليكون (TSVs) المستخدمة في جميع تصميمات HBM الحالية.

على عكس مكدسات الذاكرة التقليدية التي توجه الإشارات بشكل مستقيم لأعلى ولأسفل، تستخدم ZAM أسلاكًا قطرية متداخلة لنقل البيانات عبر المكدس. يعالج هذا التغيير البسيط ولكن الجذري ثلاث نقاط حرجة: السعة غير الكافية لنماذج الذكاء الاصطناعي الكبيرة، والسحب المفرط للطاقة في مراكز البيانات، وتراكم الحرارة الذي لا يمكن التحكم فيه في الحزم الكثيفة. ZAM ليست ترقية تدريجية. إنها إعادة تصميم من الألف إلى الياء للذاكرة المكدسة، وتستهدف النشر التجاري لمراكز بيانات الذكاء الاصطناعي وأنظمة الحوسبة عالية الأداء في الإطار الزمني لعام 2030.

الابتكارات التقنية الأساسية

تأتي مكاسب الأداء في ZAM من خمسة اختراقات تقنية متكاملة بإحكام، كل منها مصمم للعمل ضمن قواعد تصنيع أشباه الموصلات الحديثة.

طوبولوجيا الوصلة البينية القطرية. ويتمثل أساس ZAM في تحولها من الوصلات البينية الرأسية إلى الوصلات البينية القطرية المتداخلة. يوزع هذا الهيكل الإجهاد الميكانيكي والحرارة بالتساوي عبر المكدس، بدلاً من تركيز كليهما على طول الأعمدة الرأسية الضيقة. كما أنها تقصّر متوسط مسارات الإشارة، مما يقلل من زمن الاستجابة وفقدان الطاقة.

الترابط الهجين النحاسي النحاسي النحاسي. يستبدل ZAM الوصلات الميكروية القديمة ووصلات اللحام بوصلات نحاسية نحاسية هجينة مباشرة. يقلل هذا التوصيل على المستوى الذري من المقاومة والحث، ويحسن من سلامة الإشارة، ويسمح للمكدس بالتصرف ككتلة سيليكون واحدة متجانسة بدلاً من سلسلة من القوالب المنفصلة.

التصنيع عبر واحد في واحد. يستخدم ZAM عملية مبسطة عبر في واحد لتشكيل الوصلات البينية القطرية في خطوة إنتاج واحدة. وهذا يقلل من تعقيد التصنيع ويحسن الإنتاجية ويقلل من تكاليف الإنتاج مقارنةً بعملية TSV متعددة الخطوات المطلوبة ل HBM.

تصميم بدون مكثفات. يزيل ZAM المكثفات الموجودة على القالب بالكامل. وهذا يحرر مساحة قيمة من السيليكون لخلايا الذاكرة، مما يعزز كثافة التخزين مباشرةً دون تقليص عقد المعالجة. كما أنه يبسط تصميم الرقاقة ويحسن الكفاءة الكهربائية.

تكامل EMIB. تم تحسين ZAM ل ZAM ل Intel جسر التوصيل البيني متعدد القوالب المدمج (EMIB) التغليف. يتيح ذلك اتصالاً عالي السرعة ومنخفض الكمون بين حزم ZAM ومعالجات الذكاء الاصطناعي، مما يؤدي إلى إنشاء مجمع حوسبة متماسك وعالي الأداء.

ZAM ضد HBM

يوضّح الجدول أدناه كيفية مقارنة ZAM بحلول HBM3e المنتشرة على نطاق واسع وحلول HBM4 القادمة، باستخدام النماذج الأولية وأهداف التصميم التي تم الكشف عنها علنًا.

| متري | زام | HBM3e (حالي) | HBM4 (قادم) |

|---|---|---|---|

| السعة لكل كومة | حتى 512 جيجابايت | 24-36 جيجابايت | 24-48 جيجابايت |

| الحد الأقصى لطبقات المكدس | أكثر من 50 طبقة | 12-16 طبقة | 16-20 طبقة |

| استهلاك الطاقة | 40-50% أقل من HBM3e | خط الأساس | ~20% أقل من HBM3e |

| نوع الوصلة البينية | نحاس بزاوية Z قطرية | المتغيرات الرأسية المؤقتة الرأسية | المتغيرات الرأسية المؤقتة الرأسية |

| الأداء الحراري | عمود حراري مركزي؛ نقاط ساخنة منخفضة | النقاط الساخنة العالية في الطبقات العالية | تحسن متوسط |

| حالة الاستخدام المستهدفة | التدريب الكبير للذكاء الاصطناعي والحوسبة عالية الأداء | الاستدلال السحابي للذكاء الاصطناعي | أعباء عمل الذكاء الاصطناعي المتوسطة إلى الكبيرة |

المزايا الرئيسية لـ ZAM

سعة ذاكرة لا مثيل لها. يقدم ZAM 2-3 أضعاف السعة من مكدسات HBM الحالية، مع هدف 512 جيجابايت لكل مكدس. يسمح ذلك بتشغيل نماذج الأساس الأكبر حجماً على عدد أقل من المسرّعات، مما يبسّط تصميم النظام ويقلل التكلفة الإجمالية للملكية.

كفاءة الطاقة الدراماتيكية. يتم تقليل استخدام الطاقة عن طريق 40-50% مقارنةً بـ HBM3e. بالنسبة لمجموعات الذكاء الاصطناعي واسعة النطاق، يقلل ذلك من تكاليف الطاقة ويقلل من متطلبات التبريد ويساعد على تحقيق أهداف الاستدامة.

إدارة حرارية فائقة. يتم تحديد HBM التقليدي عند 16-20 طبقة تقريبًا بسبب الاختناقات الحرارية. ينشئ التوجيه القطري ل ZAM عمودًا حراريًا مركزيًا يوزع الحرارة عبر المكدس بأكمله، مما يتيح تكديسًا موثوقًا ل أكثر من 50 طبقة بدون نقاط ساخنة خطيرة.

ثبات ميكانيكي محسّن. تعمل الوصلات البينية القطرية على توزيع الضغط بشكل متساوٍ عبر القالب، مما يقلل من مخاطر الالتواء والفشل في المكدسات الطويلة. يعمل ذلك على تحسين الموثوقية على المدى الطويل في بيئات المؤسسات ومراكز البيانات.

التصنيع المبسط. تعمل العملية عبر واحد والتصميم الخالي من المكثفات على تبسيط الإنتاج. تشير التقديرات الأولية إلى إمكانية تصنيع ZAM بتكلفة أقل من حزم HBM المعقدة مع توفير سعة أعلى بكثير.

الخلفية التنموية والشراكات الصناعية

تعتمد هذه التقنية على تقنية Intel ربط الجيل التالي من DRAM DRAM (NGDB) الذي تم تطويره بدعم من مشروع تكنولوجيا الذاكرة المتقدمة (AMT) التابع لوزارة الطاقة الأمريكية ومختبرات سانديا الوطنية. ركز هذا البحث على كسر المفاضلات بين الطاقة والسعة وعرض النطاق الترددي التي تحد من ذاكرة DRAM التقليدية.

تأسست شركة SAIMEMEMORY في ديسمبر 2024 كشركة تابعة لـ SoftBank بمهمة واحدة: تطوير ذاكرة الجيل التالي للذكاء الاصطناعي. تم الإعلان عن الشراكة الرسمية بين إنتل وسايموري في 2 فبراير 2026وظهرت ZAM لأول مرة على مستوى العالم بعد يوم واحد في إنتل كونيكشن اليابان 2026. في إطار هذا التعاون، تساهم Intel بخبرتها المتقدمة في مجال التغليف والتعبئة والتغليف، بينما تقود شركة SAIMEMEMORY تطوير البنية وتسويقها.

حالات الاستخدام في العالم الحقيقي

تم تصميم ZAM لتلبية أعباء العمل الأكثر تطلبًا في الحوسبة الحديثة:

- تدريب نماذج الذكاء الاصطناعي على نطاق واسع. تعمل السعة الهائلة لكل مكدس على إزالة اختناقات الذاكرة لنماذج الأساس ذات التريليون معيار مما يسمح بتدريب أسرع وتصميم أبسط للمجموعات.

- استدلال الذكاء الاصطناعي السحابي على نطاق واسع. يقلل استهلاك الطاقة المنخفض من التكاليف التشغيلية لمقدمي الخدمات السحابية فائقة النطاق الذين يقومون بتشغيل أعباء عمل الاستدلال المستمر.

- الحوسبة عالية الأداء. تستفيد عمليات المحاكاة العلمية ونمذجة الطقس والنمذجة المالية من السعة العالية والوصول المستقر ومنخفض الكمون إلى الذاكرة.

- تجميع الذاكرة CXL تجميع ذاكرة CXL. يجعل تكديس ZAM الفعال وعرض النطاق الترددي العالي من ZAM مناسبًا بشكل طبيعي لتجميع الذاكرة السريعة للحوسبة (CXL)، مما يتيح موارد ذاكرة مشتركة مرنة ومرنة في مراكز البيانات الحديثة.

- الذكاء الاصطناعي المتطور والأنظمة المستقلة. تدعم كفاءة الطاقة المحسّنة عمليات نشر الذكاء الاصطناعي في البيئات الطرفية المحدودة الطاقة، بدءًا من الأتمتة الصناعية إلى المركبات ذاتية القيادة.

الوضع الحالي والجدول الزمني المستقبلي

اعتبارًا من أوائل عام 2026، لا تزال ZAM قيد التطوير النشط مع وجود خارطة طريق واضحة وعامة:

- شباط/فبراير 2026: عرض أول نموذج أولي في Intel Connection Japan، يركز على الإدارة الحرارية.

- 2027: من المتوقع إصدار عينات هندسية وشرائح اختبار لشركاء الأجهزة.

- 2030: النشر التجاري الشامل المستهدف لمراكز بيانات الذكاء الاصطناعي وأنظمة الحوسبة عالية الأداء.

لا تزال المنصة قيد التحسين، ولكن نتائج النموذج الأولي المبكرة تؤكد صحة ادعاءاتها الأساسية حول السعة والطاقة والأداء الحراري. يُنظر إلى ZAM على نطاق واسع على أنه مرشح رائد لخلافة HBM في مشهد ذاكرة الذكاء الاصطناعي لما بعد عام 2030.

تمثل ذاكرة Z-Angle Memory نقلة نوعية في تصميم ذاكرة DRAM المكدسة. من خلال استبدال TSVs العمودية بطوبولوجيا التوصيل البيني المائل على شكل حرف Z، فإنها تعالج أكثر القيود المستمرة في HBM. لكن المشهد التنافسي لذاكرة الذكاء الاصطناعي ديناميكي. وتستهدف التقنيات المنافسة، مثل تقنية zHBM التي أعلنت عنها سامسونج مؤخراً، حقبة ما بعد HBM4 مع مطالبات قوية للأداء. علاوة على ذلك، يعتمد التسويق التجاري الناجح لأي بنية ذاكرة جديدة على تحقيق إنتاجية تصنيع عالية، وهياكل تكلفة تنافسية، والأهم من ذلك - اعتمادها من قبل كبار بائعي مسرعات الذكاء الاصطناعي والأنظمة. لذلك، بينما تقدم ZAM مخططًا مقنعًا، فإن رحلتها من النموذج الأولي إلى معيار الصناعة ستتوقف على التغلب على هذه التحديات الهندسية وتحديات النظام البيئي في العالم الحقيقي.