大型语言模型、生成式人工智能和高性能计算(HPC)的快速发展已将传统内存架构推向物理极限。 高 带宽内存(HBM) 长期以来一直是人工智能加速器的黄金标准,但随着堆栈高度和密度的增加,它在容量、功耗和热管理方面面临着越来越多的瓶颈。

2026 年 2 月初、 Z 角存储器 (ZAM) 作为应对这些挑战的专用解决方案,ZAM 应运而生。ZAM 由英特尔和软银公司的全资子公司 SAIMEMORY 共同开发,是下一代堆叠式 DRAM 架构,旨在重新定义数据密集型工作负载的内存扩展。

什么是 Z 角存储器

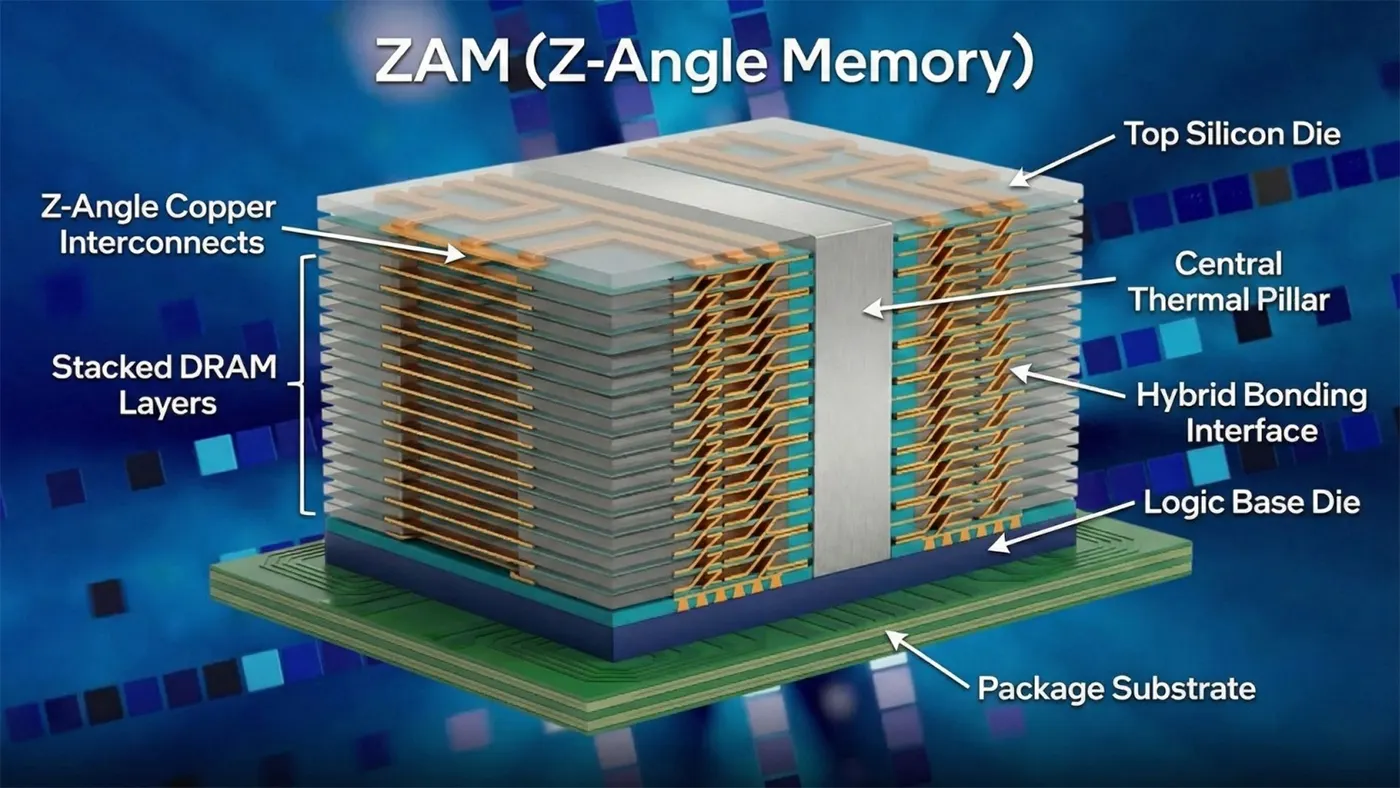

Z 角存储器 (ZAM) 是一种 3D 堆叠式 DRAM 架构,旨在克服传统 HBM 的扩展限制。它的名字来源于其决定性的创新:一个 对角线 Z 型互连拓扑结构 它取代了目前所有 HBM 设计中使用的垂直硅通孔 (TSV)。

传统的内存堆栈信号直上直下,而 ZAM 则不同,它采用交错的对角线布线方式在堆栈中移动数据。这一微小而彻底的改变解决了三个关键痛点: 大型人工智能模型容量不足、数据中心功耗过高,以及密集封装中难以控制的热量积聚。 ZAM 不是增量升级。它是对堆叠式内存的全新设计,目标是在 2030 年实现人工智能数据中心和高性能计算系统的商业部署。

核心技术创新

ZAM 的性能提升来自于五项紧密结合的技术突破,每项技术都是专为现代半导体制造规则而设计的。

对角互联拓扑。 ZAM 的基础是从垂直 TSV 转向交错的对角互连。这种结构能将机械应力和热量均匀地分散到整个堆栈中,而不是集中在狭窄的垂直列上。它还缩短了平均信号路径,减少了延迟和功率损耗。

铜-铜混合键合。 ZAM 以直接铜铜混合键合取代了传统的微凸块和焊接连接。这种原子级连接降低了电阻和电感,改善了信号完整性,并使堆栈表现得像一个单片硅块,而不是一系列分立的芯片。

一体化制造 ZAM 采用简化的一体化过孔工艺,在单一生产步骤中形成对角互连。与 HBM 所需的多步骤 TSV 工艺相比,这降低了制造复杂性,提高了产量,并减少了生产成本。

无电容设计 ZAM 完全消除了片上电容器。这就为存储单元腾出了宝贵的硅片面积,在不缩小工艺节点的情况下直接提高了存储密度。它还简化了芯片设计,提高了电气效率。

EMIB 整合。 ZAM 针对英特尔的 嵌入式多芯片互连桥接器 (EMIB) 包装。这就实现了 ZAM 堆栈和人工智能处理器之间的高速、低延迟连接,从而创建了一个具有凝聚力的高性能计算综合体。

ZAM vs. HBM

下表利用公开披露的原型和设计目标,将 ZAM 与广泛部署的 HBM3e 和即将推出的 HBM4 解决方案进行了比较。

| 公制 | ZAM | HBM3e(电流) | HBM4(即将推出) |

|---|---|---|---|

| 每个堆栈的容量 | 最高 512GB | 24-36GB | 24-48GB |

| 最大堆栈层数 | 50+ 层 | 12-16 层 | 16-20 层 |

| 耗电量 | 40-50% 低于 HBM3e | 基线 | ~20% 低于 HBM3e |

| 互联类型 | 对角 Z 角铜 | 垂直 TSV | 垂直 TSV |

| 热性能 | 中央热柱;低热点 | 高处的高热点 | 中度改善 |

| 目标用例 | 大型人工智能培训、高性能计算 | 云人工智能推理 | 中大型人工智能工作负载 |

ZAM 的主要优势

无与伦比的内存容量 ZAM 提供 容量的 2-3 倍 与当前的 HBM 堆栈相比,每个堆栈的目标容量为 512GB。这样就可以在更少的加速器上运行更大的基础模型,从而简化系统设计并降低总拥有成本。

显著的能源效率 用电量减少 40-50% 相比 HBM3e。对于大规模人工智能集群来说,这可以降低能源成本,减少冷却需求,有助于实现可持续发展目标。

卓越的热管理 由于热瓶颈,传统 HBM 的层数上限大约为 16-20 层。ZAM 的对角线布线创建了一个中央热支柱,可在整个堆栈中分配热量,从而实现可靠的堆叠。 50+ 层 无危险热点。

增强机械稳定性。 对角线互连可将压力均匀分散到整个芯片上,从而降低高堆栈中的翘曲和故障风险。这提高了企业和数据中心环境的长期可靠性。

简化制造。 一体化过孔工艺和无电容设计简化了生产流程。早期估计表明,ZAM 的制造成本低于复杂的 HBM 堆栈,但容量却高得多。

发展背景与行业伙伴关系

该技术借鉴了英特尔 下一代 DRAM 粘合(NGDB) 该项目是在美国能源部先进内存技术(AMT)项目和桑迪亚国家实验室的支持下开发的。这项研究的重点是打破限制传统 DRAM 的功率-容量-带宽权衡。

SAIMEMORY 成立于 2024 年 12 月,是软银的子公司,其使命只有一个:为人工智能开发新一代内存。英特尔与 SAIMEMORY 的正式合作于 2026 年 2 月 2 日一天后,ZAM 的全球原型首次亮相。 英特尔连接日本 2026.在这项合作中,英特尔提供先进的封装和键合技术,而 SAIMEMORY 则负责架构开发和商业化。

真实世界使用案例

ZAM 专为现代计算中要求最苛刻的工作负载而设计:

- 大规模人工智能模型训练 每个堆栈的超大容量消除了万亿参数基础模型的内存瓶颈,从而加快了训练速度,简化了集群设计。

- 大规模云人工智能推理。 更低的功耗降低了运行连续推理工作负载的超大规模云提供商的运营成本。

- 高性能计算。 科学模拟、天气建模和金融建模都受益于更大的容量和稳定、低延迟的内存访问。

- CXL 内存池 ZAM 的高效堆叠和高带宽使其成为计算快速链路 (CXL) 内存池的理想选择,从而在现代数据中心实现灵活的共享内存资源。

- 边缘人工智能与自主系统。 从工业自动化到自动驾驶汽车,更高的能效可支持在电力受限的边缘环境中部署人工智能。

现状与未来时间表

截至 2026 年初,ZAM 仍在积极开发中,并制定了明确的公开路线图:

- 2026 年 2 月:在日本英特尔连接公司进行的首次原型演示,重点是热管理。

- 2027:预计将向硬件合作伙伴发布工程样品和测试芯片。

- 2030:人工智能数据中心和高性能计算系统的大规模商业部署目标。

该平台仍在不断完善中,但早期原型结果验证了其在容量、功耗和散热性能方面的核心诉求。在 2030 年后的人工智能内存领域,ZAM 被广泛视为接替 HBM 的主要候选产品。

Z 角内存代表了堆叠式 DRAM 设计模式的转变。通过用对角线 Z 型互连拓扑取代垂直 TSV,它解决了 HBM 最顽固的制约因素。但是,人工智能内存的竞争格局是动态的。竞争对手的技术,如三星最近发布的 zHBM,也瞄准了后 HBM4 时代,提出了积极的性能要求。此外,任何新内存架构的成功商业化都取决于能否实现较高的制造良率、具有竞争力的成本结构,以及最关键的一点,即能否获得主要人工智能加速器和系统供应商的采用。因此,尽管 ZAM 提出了令人信服的蓝图,但其从原型到行业标准的过程将取决于能否克服这些现实世界中的工程和生态系统挑战。