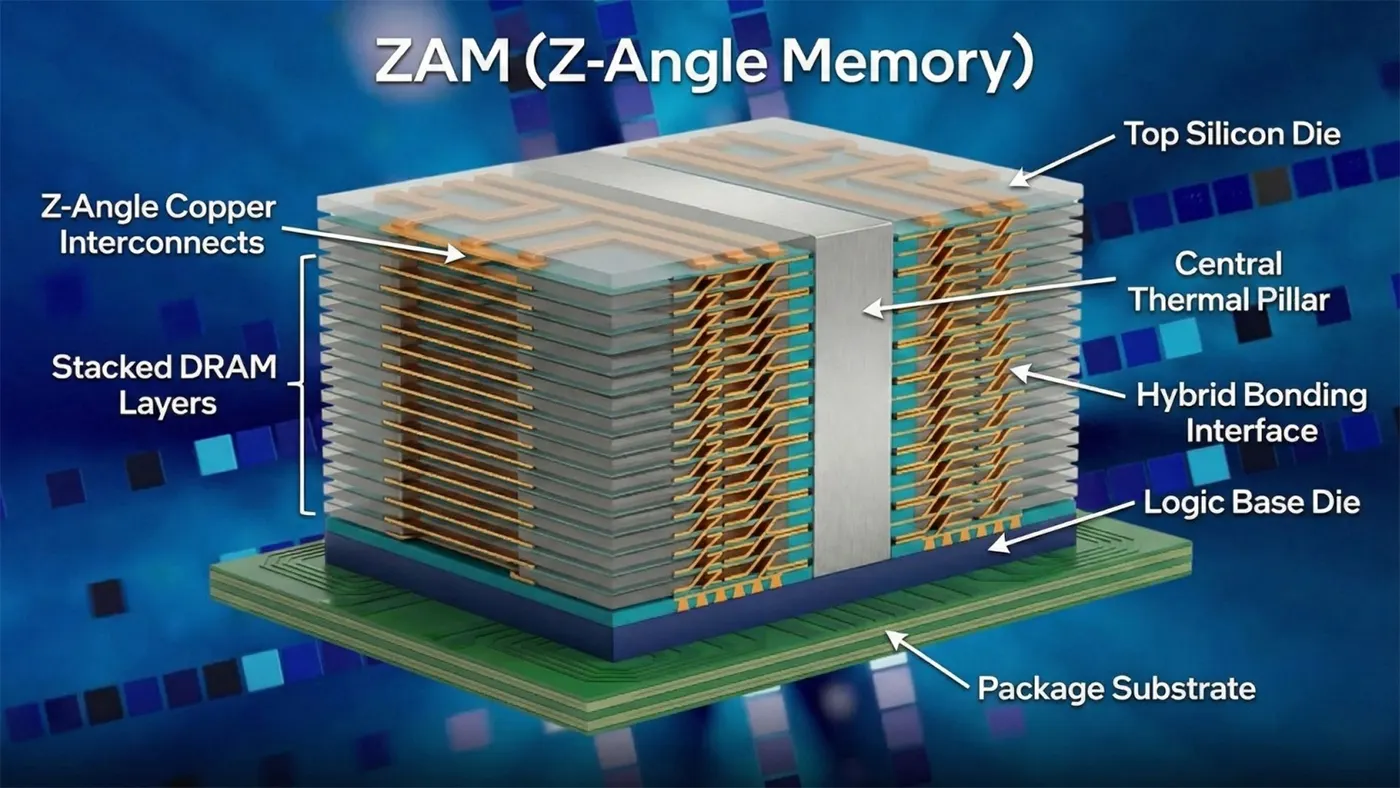

O que é a memória de ângulo Z

Inovações técnicas fundamentais

ZAM vs. HBM

| Métrica | ZAM | HBM3e (Atual) | HBM4 (em breve) |

|---|---|---|---|

| Capacidade por pilha | Até 512GB | 24-36 GB | 24-48GB |

| Máximo de camadas de empilhamento | Mais de 50 camadas | 12-16 camadas | 16-20 camadas |

| Consumo de energia | 40-50% inferior ao HBM3e | Linha de base | ~20% inferior ao HBM3e |

| Tipo de interconexão | Cobre diagonal em ângulo Z | TSVs verticais | TSVs verticais |

| Desempenho térmico | Pilar térmico central; pontos quentes baixos | Pontos quentes elevados em camadas altas | Melhoria moderada |

| Caso de utilização alvo | Grande formação em IA, HPC | Inferência de IA na nuvem | Cargas de trabalho de IA de média a grande dimensão |

Principais vantagens da ZAM

Antecedentes de desenvolvimento e parcerias industriais

Casos de utilização no mundo real

- Formação de modelos de IA em grande escala. A enorme capacidade por pilha elimina os estrangulamentos de memória para modelos de base com triliões de parâmetros, permitindo uma formação mais rápida e um design de cluster mais simples.

- Inferência de IA na nuvem à escala. O menor consumo de energia reduz os custos operacionais para os fornecedores de nuvem em hiperescala que executam cargas de trabalho de inferência contínua.

- Computação de alto desempenho. As simulações científicas, a modelação meteorológica e a modelação financeira beneficiam de uma maior capacidade e de um acesso estável e de baixa latência à memória.

- Pooling de memória CXL. O empilhamento eficiente e a alta largura de banda do ZAM fazem dele um ajuste natural para o pooling de memória do compute express link (CXL), permitindo recursos de memória flexíveis e compartilhados em centros de dados modernos.

- IA de ponta e sistemas autónomos. A eficiência energética melhorada suporta implementações de IA em ambientes de ponta com restrições de energia, desde a automação industrial até aos veículos autónomos.

Situação atual e calendário futuro

- fevereiro de 2026: Primeiro protótipo de demonstração na Intel Connection Japan, centrado na gestão térmica.

- 2027: Espera-se que as amostras de engenharia e os chips de teste sejam disponibilizados aos parceiros de hardware.

- 2030: Objetivo: implantação comercial em massa para centros de dados de IA e sistemas HPC.

A memória Z-Angle representa uma mudança de paradigma no design de DRAM empilhada. Ao substituir os TSVs verticais por uma topologia de interconexão diagonal, em forma de Z, ela enfrenta as restrições mais persistentes da HBM. Mas o cenário competitivo para a memória AI é dinâmico. Tecnologias rivais, como o zHBM recentemente anunciado pela Samsung, também estão a visar a era pós-HBM4 com reivindicações de desempenho agressivas. Além disso, a comercialização bem-sucedida de qualquer nova arquitetura de memória depende da obtenção de alto rendimento de fabricação, estruturas de custo competitivas e - criticamente - adoção pelos principais aceleradores de IA e fornecedores de sistemas. Portanto, embora a ZAM apresente um projeto atraente, sua jornada do protótipo ao padrão da indústria dependerá da superação desses desafios de engenharia e ecossistema do mundo real.