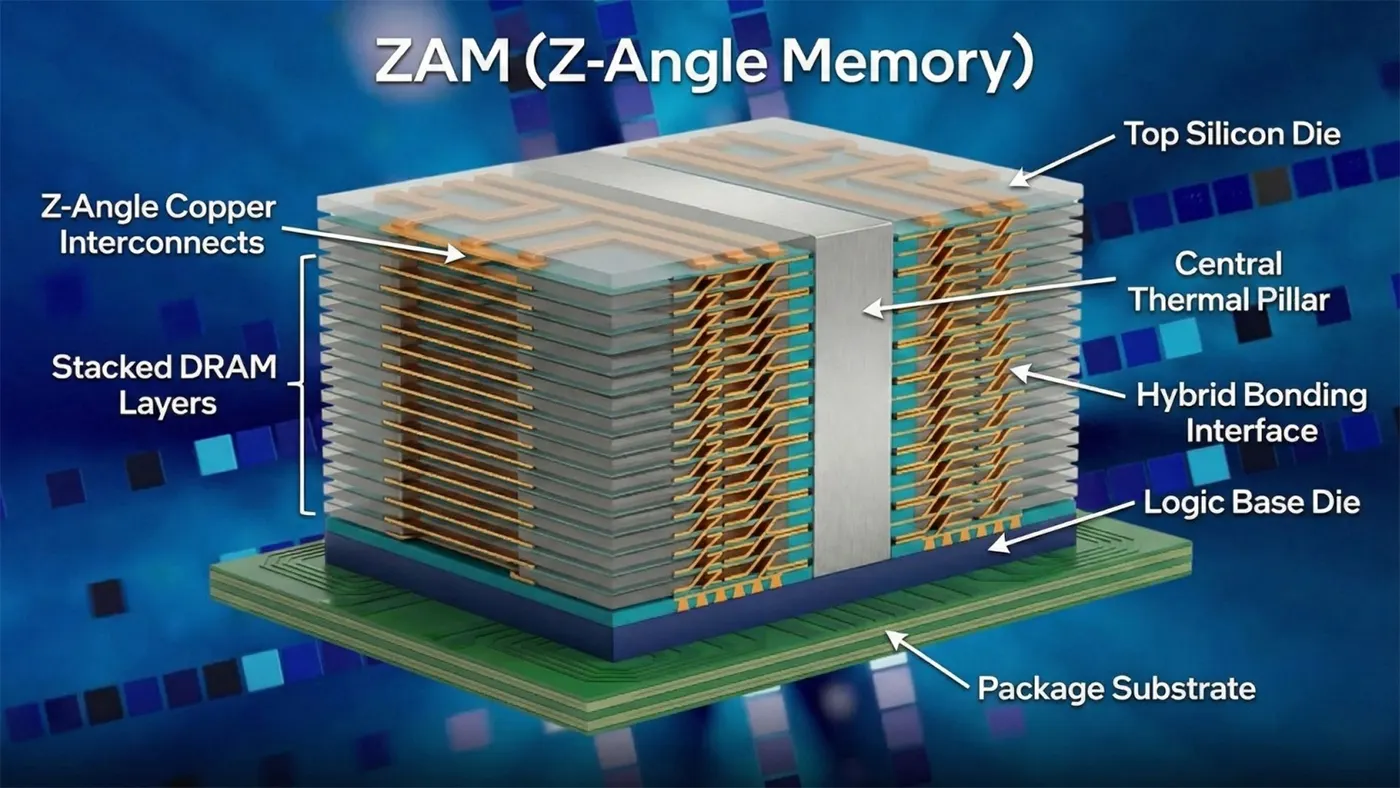

Was ist ein Z-Winkel-Speicher?

Zentrale technische Innovationen

ZAM vs. HBM

| Metrisch | ZAM | HBM3e (aktuell) | HBM4 (Demnächst) |

|---|---|---|---|

| Kapazität pro Stapel | Bis zu 512 GB | 24-36GB | 24-48GB |

| Maximale Stapelschichten | 50+ Schichten | 12-16 Schichten | 16-20 Schichten |

| Stromverbrauch | 40-50% niedriger als HBM3e | Basislinie | ~20% niedriger als HBM3e |

| Typ der Zusammenschaltung | Diagonale Z-Winkel Kupfer | Vertikale TSVs | Vertikale TSVs |

| Thermische Leistung | Zentrale thermische Säule; niedrige Hotspots | Hohe Hotspots in hohen Schichten | Mäßige Verbesserung |

| Ziel-Anwendungsfall | Großes KI-Training, HPC | Cloud AI-Inferenz | Mittlere bis große KI-Workloads |

Die wichtigsten Vorteile des ZAM

Entwicklungshintergrund & Industriepartnerschaften

Anwendungsfälle aus der realen Welt

- Großangelegtes AI-Modell-Training. Die enorme Kapazität der einzelnen Stapel beseitigt Speicherengpässe für Billionen-Parameter-Grundmodelle und ermöglicht ein schnelleres Training und ein einfacheres Cluster-Design.

- Cloud AI Inference in großem Maßstab. Der geringere Stromverbrauch senkt die Betriebskosten für Hyperscale-Cloud-Anbieter, die kontinuierliche Inferenz-Workloads ausführen.

- Hochleistungs-Computing. Wissenschaftliche Simulationen, Wettermodelle und Finanzmodelle profitieren von höherer Kapazität und stabilem Speicherzugriff mit geringer Latenz.

- CXL-Speicher-Pooling. Das effiziente Stacking und die hohe Bandbreite von ZAM eignen sich hervorragend für das Compute Express Link (CXL)-Speicher-Pooling, das flexible, gemeinsam genutzte Speicherressourcen in modernen Rechenzentren ermöglicht.

- Edge AI & Autonome Systeme. Die verbesserte Energieeffizienz unterstützt den Einsatz von KI in Umgebungen mit eingeschränktem Stromverbrauch, von der industriellen Automatisierung bis hin zu autonomen Fahrzeugen.

Aktueller Stand und zukünftiger Zeitplan

- Februar 2026: Erste Prototyp-Demonstration auf der Intel Connection Japan, mit Schwerpunkt auf Wärmemanagement.

- 2027: Technische Muster und Testchips werden voraussichtlich an Hardware-Partner weitergegeben.

- 2030: Ziel ist der kommerzielle Masseneinsatz für KI-Rechenzentren und HPC-Systeme.

Z-Angle Memory stellt einen Paradigmenwechsel im Stacked DRAM-Design dar. Durch das Ersetzen vertikaler TSVs durch eine diagonale, Z-förmige Verbindungstopologie werden die hartnäckigsten Einschränkungen von HBM angegangen. Doch die Wettbewerbslandschaft für KI-Speicher ist dynamisch. Konkurrierende Technologien, wie das kürzlich von Samsung angekündigte zHBM, zielen ebenfalls auf die Post-HBM4-Ära mit aggressiven Leistungsansprüchen. Darüber hinaus hängt die erfolgreiche Kommerzialisierung jeder neuen Speicherarchitektur davon ab, dass eine hohe Produktionsausbeute, wettbewerbsfähige Kostenstrukturen und - was besonders wichtig ist - die Übernahme durch wichtige KI-Beschleuniger- und Systemanbieter erreicht werden. Obwohl ZAM ein überzeugendes Konzept darstellt, hängt der Weg vom Prototyp zum Industriestandard von der Bewältigung dieser realen technischen und ökosystemischen Herausforderungen ab.