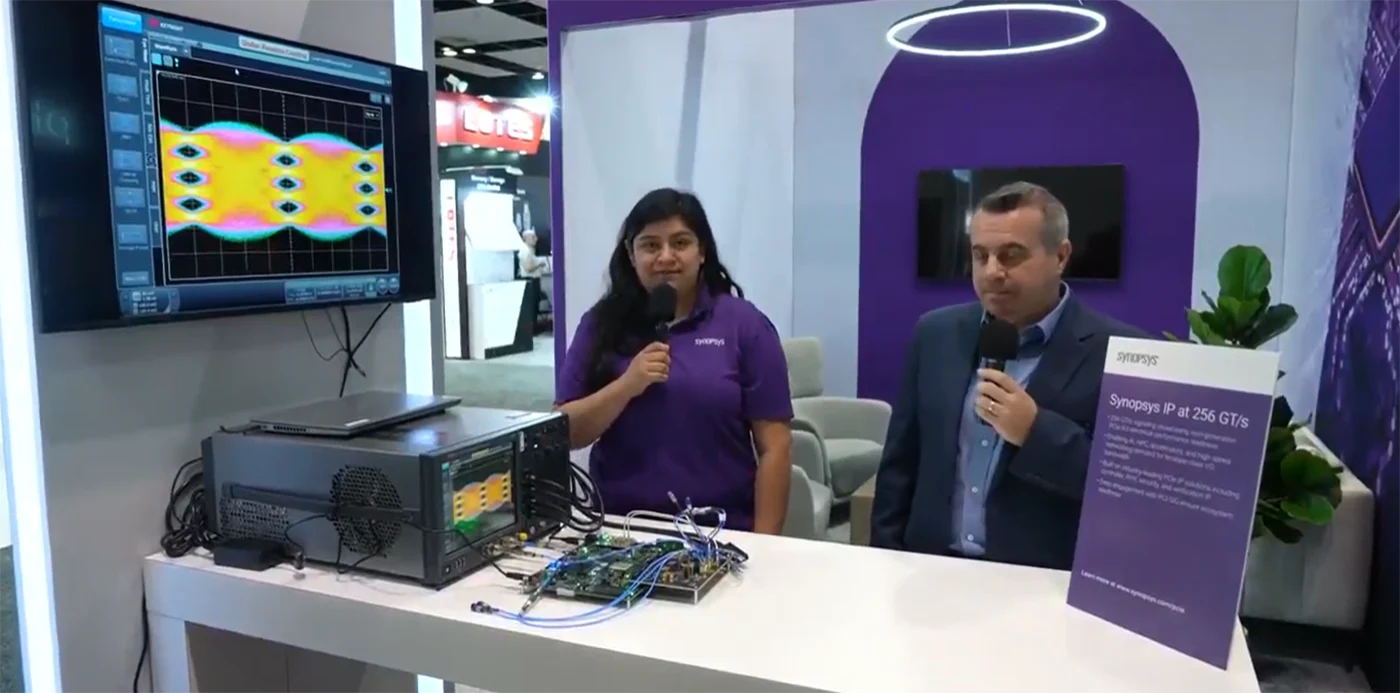

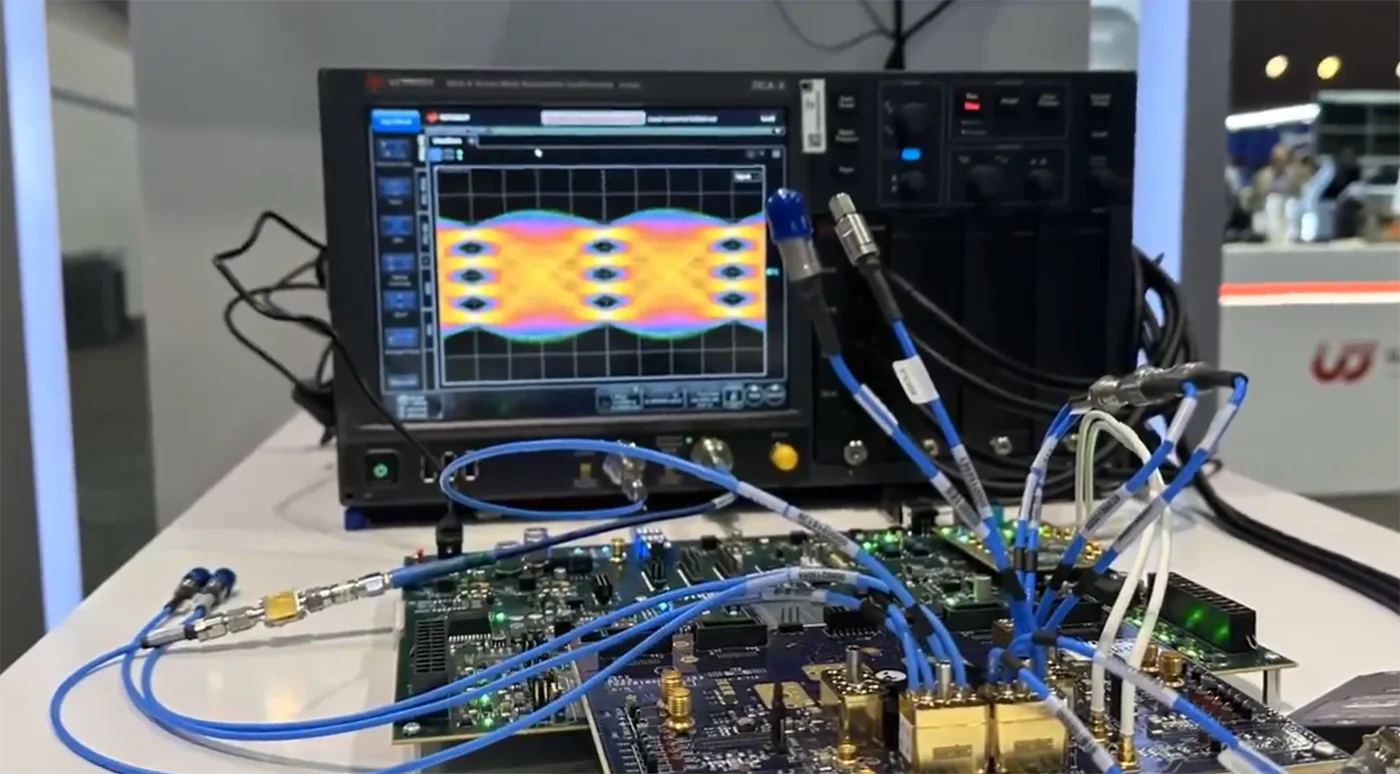

シノプシスのPCIe 8.0デモ

- アイ・ダイアグラム分析:256 GT/sレートでのシグナルインテグリティと品質の可視化

- 受信機の性能検証:高速信号を正しく検出して処理する能力を検証する

- リンクのトレーニングと同期:機器間の安定した通信の確保

PCIe帯域幅の進化

長年にわたるPCIe帯域幅の進歩は、データ転送能力がいかに急速に向上したかを物語っています。

| PCIe世代 | 導入年 | x16 帯域幅(双方向) |

|---|---|---|

| PCIe 3.0 | 2010 | 32GB/秒 |

| PCIe 4.0 | 2017 | 64GB/秒 |

| PCIe 5.0 | 2019 | 128GB/秒 |

| PCIe 6.0 | 2022 | 256GB/秒 |

| PCIe 7.0 | 2025 | 512GB/秒 |

| PCIe 8.0 | 2028年予定 | ~1TB/秒 |

現在のロードマップが維持されるなら PCIe 8.0 x16スロットは理論上、双方向合わせて毎秒約1テラバイトのデータを移動できる.これは、以前の世代と比べて劇的な飛躍を意味する。

PCIe 8.0を支えるテクノロジー

このような極端なスピードに到達するには、信号伝送とエラー管理において大きな技術革新が必要だ。最も重要な技術のひとつが PAM4(4レベルのパルス振幅変調).単純なバイナリ信号を使用していた以前のPCIe世代とは異なり、PAM4では複数の電圧レベルを使用することで、各信号サイクルがより多くの情報を伝達できるようになっている。

この方法は帯域幅を劇的に向上させるが、同時にエラー率も高くなる。信頼性を維持するために、新しいPCIe世代では 前方誤り訂正(FEC)PCIe6.0はこれらの技術を導入した。PCIe 6.0ではこれらの技術が導入され、PCIe 8.0ではさらにこれらの技術が拡張され、さらなる高速化がサポートされる予定です。

もうひとつの重要なコンセプトは フリットベースデータ伝送この方式では、情報は固定サイズのデータ単位で送信される。この方式は、非常に高速な通信リンクの効率を改善し、エラー訂正を簡素化する。

これらの技術を組み合わせることで、従来の信号方式では実用的でなかった速度でのデータ転送が可能になる。

業界がさらなる高速PCIeを必要とする理由

PCIe 8.0に向けた動きは、PCIe 8.0の急速な成長によるところが大きい。 AIコンピューティングとデータセンターのワークロード.最新のAIサーバーには、複数のGPUや専用のアクセラレーターが搭載されていることが多く、トレーニングや推論タスク中に膨大な量のデータをやり取りする必要がある。これらのシステムは、広帯域幅の内部接続に大きく依存しています。

モデルが大きくなり、データセットが拡大するにつれて、コンポーネント間の高速通信に対する要求は高まり続けている。ハイパフォーマンス・コンピューティング(HPC)、クラウドインフラ、大規模ストレージシステムも同様の課題に直面しています。

このような環境では、より高速なPCIe接続が可能になる:

CPUとより効率的に通信するGPU

AIアクセラレーターが学習データをより速く共有

より高いスループットを実現するNVMeストレージアレイ

より低遅延でデータを移動させるネットワーク・ハードウェア

インターコネクトの帯域幅が改善され続けなければ、将来のコンピューティングシステムの性能は、最終的には処理能力よりも通信のボトルネックによって制限されることになるだろう。

PCIe 8.0が利用可能になる時期

最近のデモンストレーションにもかかわらず、PCIe 8.0はまだ初期の開発段階にある。この規格は PCI-SIG最終的なスペックは以下のようになる。 2028.商用ハードウェアは通常、新しい仕様が確定してから数年後に登場する。現実的な採用スケジュールは次のようになる:

| ステージ | 予想される期間 |

|---|---|

| 仕様決定 | ~2028 |

| 初期のシリコン・プロトタイプ | 2028-2029 |

| データセンターの採用 | 2030年頃 |

| コンシューマーPC | 2030年代前半 |

今のところ、PCIe 5.0とPCIe 6.0が現在のハードウェア開発に最も関連する世代である。

PCIe 8.0技術の最初の公開デモンストレーションは、コンピューティング業界にとって早期ではあるが重要なマイルストーンとなる。これは、PCIeロードマップの次のステップが技術的に達成可能であり、チップ設計者、コネクタメーカー、システムベンダーのエコシステムがすでにその準備を進めていることを確認するものです。日常的なユーザーがPCIe 8.0デバイスを目にするようになるのは数年後ですが、今日テストされている技術は、最終的には明日のAIサービス、クラウドプラットフォーム、高性能コンピューティングシステムの背後にあるデータインフラをサポートすることになるでしょう。