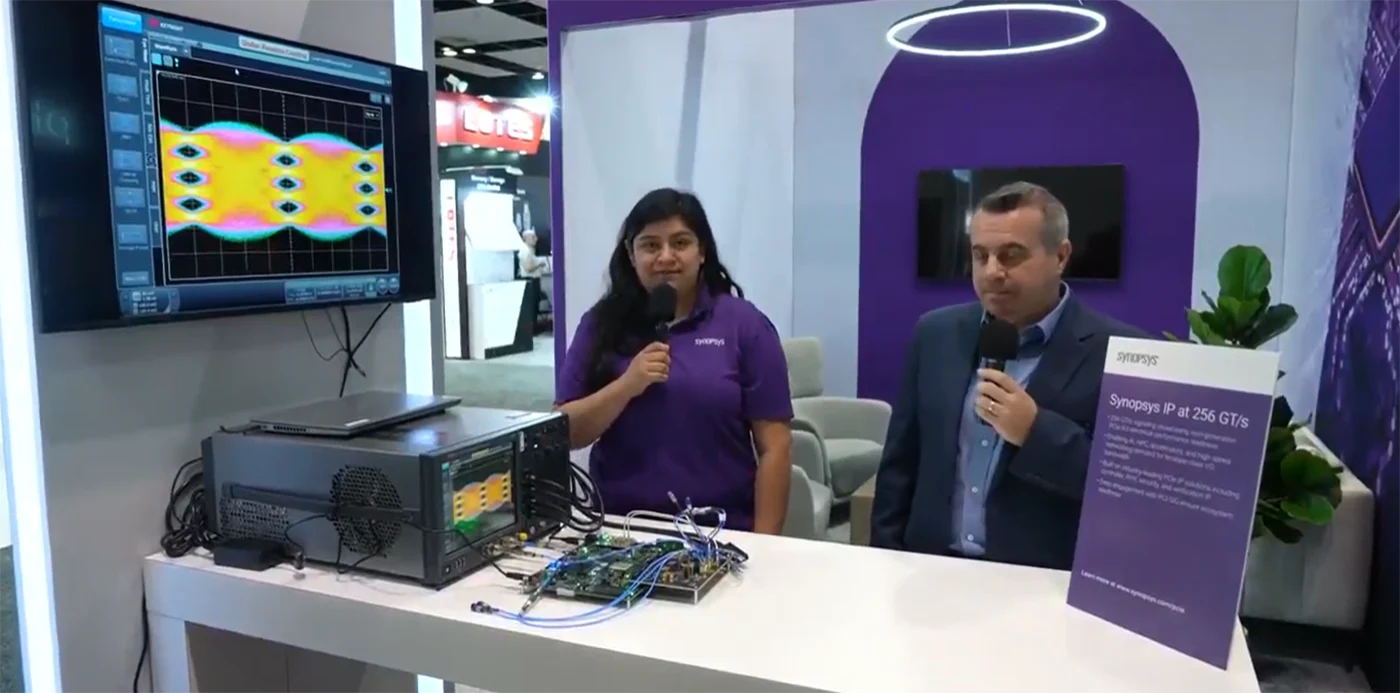

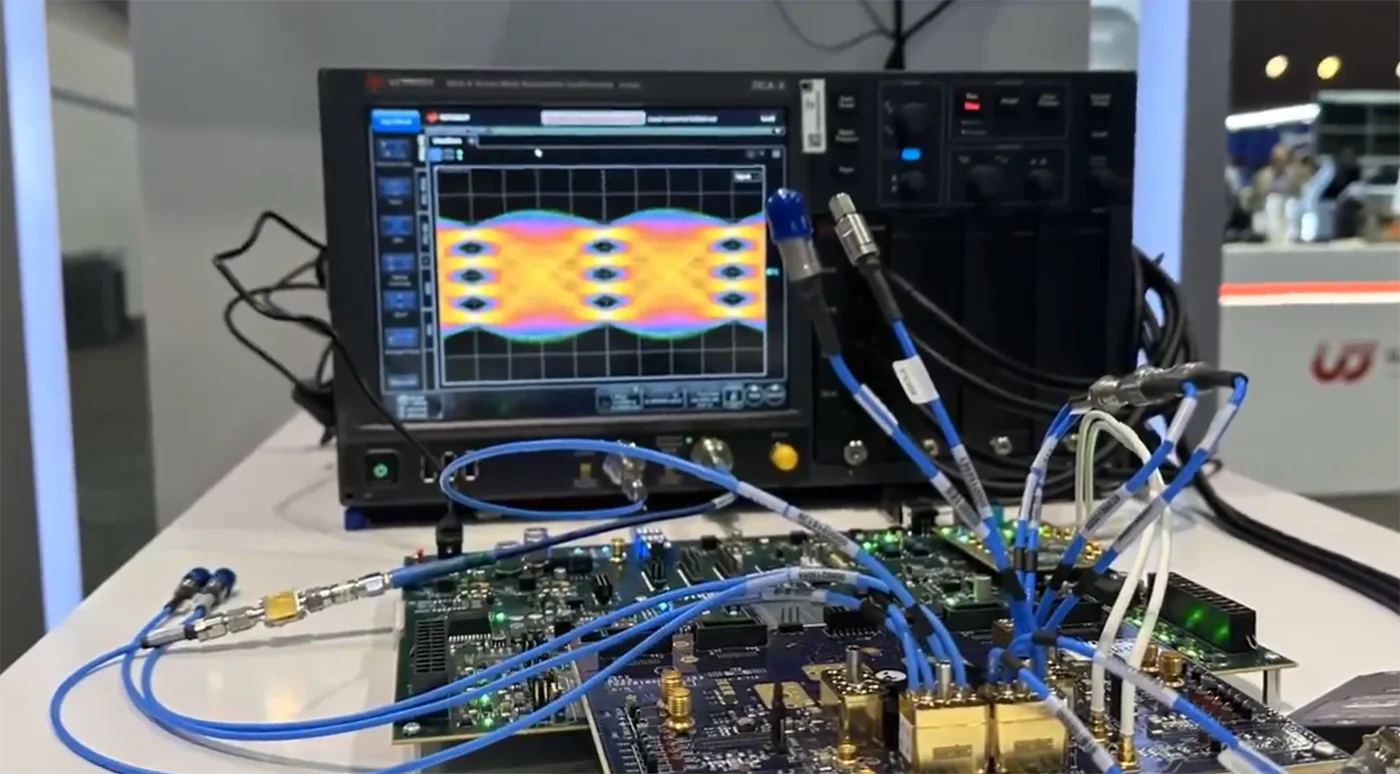

Synopsys의 PCIe 8.0 데모

- 아이 다이어그램 분석: 256 GT/s 속도로 신호 무결성 및 품질 시각화

- 수신기 성능 검증: 고속 신호를 올바르게 감지하고 처리하는 기능 검증

- 링크 교육 및 동기화: 디바이스 간 안정적인 통신 보장

PCIe 대역폭의 진화 과정

수년에 걸친 PCIe 대역폭의 발전은 데이터 전송 기능이 얼마나 빠르게 증가했는지 잘 보여줍니다.

| PCIe 세대 | 도입 연도 | x16 대역폭(양방향) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | 예상 ~2028년 | ~최대 1TB/s |

현재 로드맵이 유지된다면 PCIe 8.0 x16 슬롯은 이론적으로 양방향으로 초당 약 1테라바이트의 데이터를 이동시킬 수 있습니다.. 이는 이전 세대와 비교했을 때 비약적인 발전을 의미합니다.

PCIe 8.0의 기술

이러한 극한의 속도에 도달하려면 신호 전송 및 오류 관리에 있어 대대적인 혁신이 필요합니다. 이와 관련된 가장 중요한 기술 중 하나는 PAM4(4단계 펄스 진폭 변조). 단순한 바이너리 신호를 사용했던 이전 PCIe 세대와 달리 PAM4는 여러 전압 레벨을 사용하여 각 신호 사이클에 더 많은 정보를 전달할 수 있습니다.

이 접근 방식은 대역폭을 크게 증가시키지만 오류 발생률도 높아집니다. 안정성을 유지하기 위해 최신 PCIe 세대에서는 순방향 오류 수정(FEC)전송 중 오류를 감지하고 수정하는 기술입니다. PCIe 6.0은 이러한 기술을 도입했으며, PCIe 8.0은 더 빠른 속도를 지원하기 위해 기술을 더욱 확장할 예정입니다.

또 다른 중요한 개념은 플릿 기반 데이터 전송를 사용하여 고정된 크기의 데이터 단위로 정보를 전송합니다. 이 방법은 매우 빠른 통신 링크에서 효율성을 개선하고 오류 수정을 간소화합니다.

이러한 기술을 함께 사용하면 기존 시그널링 방식으로는 불가능했던 속도로 데이터를 전송할 수 있습니다.

업계에 더 빠른 PCIe가 필요한 이유

PCIe 8.0에 대한 추진은 주로 다음과 같은 급속한 성장에 의해 주도됩니다. AI 컴퓨팅 및 데이터센터 워크로드. 최신 AI 서버에는 훈련 및 추론 작업 중에 막대한 양의 데이터를 교환해야 하는 여러 개의 GPU 또는 특수 가속기가 포함되어 있는 경우가 많습니다. 이러한 시스템은 고대역폭 내부 연결에 크게 의존합니다.

모델이 커지고 데이터 세트가 확장됨에 따라 구성 요소 간의 빠른 통신에 대한 요구가 계속 증가하고 있습니다. 고성능 컴퓨팅(HPC), 클라우드 인프라, 대규모 스토리지 시스템도 비슷한 문제에 직면해 있습니다.

이러한 환경에서는 더 빠른 PCIe 연결이 가능합니다:

CPU와 더 효율적으로 통신하는 GPU

학습 데이터를 더 빠르게 공유하는 AI 가속기

더 높은 처리량을 제공하는 NVMe 스토리지 어레이

짧은 지연 시간으로 데이터를 이동하는 네트워킹 하드웨어

상호 연결 대역폭의 지속적인 개선이 없다면 미래 컴퓨팅 시스템의 성능은 결국 처리 능력이 아닌 통신 병목 현상에 의해 제한될 것입니다.

PCIe 8.0 출시 시기

최근의 시연에도 불구하고 PCIe 8.0은 아직 초기 개발 단계에 있습니다. 표준은 다음과 같이 정의되고 있습니다. PCI-SIG의 최종 사양은 다음과 같이 예상됩니다. 2028. 상용 하드웨어는 일반적으로 새로운 사양이 확정된 후 몇 년 후에 등장합니다. 현실적인 도입 일정은 다음과 같습니다:

| 스테이지 | 예상 기간 |

|---|---|

| 사양 확정 | ~2028 |

| 초기 실리콘 프로토타입 | 2028-2029 |

| 데이터 센터 도입 | 2030년경 |

| 소비자 PC | 2030년대 초반 |

현재로서는 PCIe 5.0과 PCIe 6.0이 현재 하드웨어 개발과 가장 관련성이 높은 세대입니다.

PCIe 8.0 기술의 첫 공개 시연은 컴퓨팅 업계에 있어 초기 단계이지만 중요한 이정표입니다. PCIe 로드맵의 다음 단계가 기술적으로 달성 가능하며 칩 설계자, 커넥터 제조업체 및 시스템 공급업체의 생태계가 이미 이를 준비하고 있다는 것을 확인시켜 줍니다. 일반 사용자들은 몇 년 동안 PCIe 8.0 장치를 보지 못하겠지만, 현재 테스트 중인 기술은 결국 미래의 AI 서비스, 클라우드 플랫폼 및 고성능 컴퓨팅 시스템의 데이터 인프라를 지원할 것입니다.