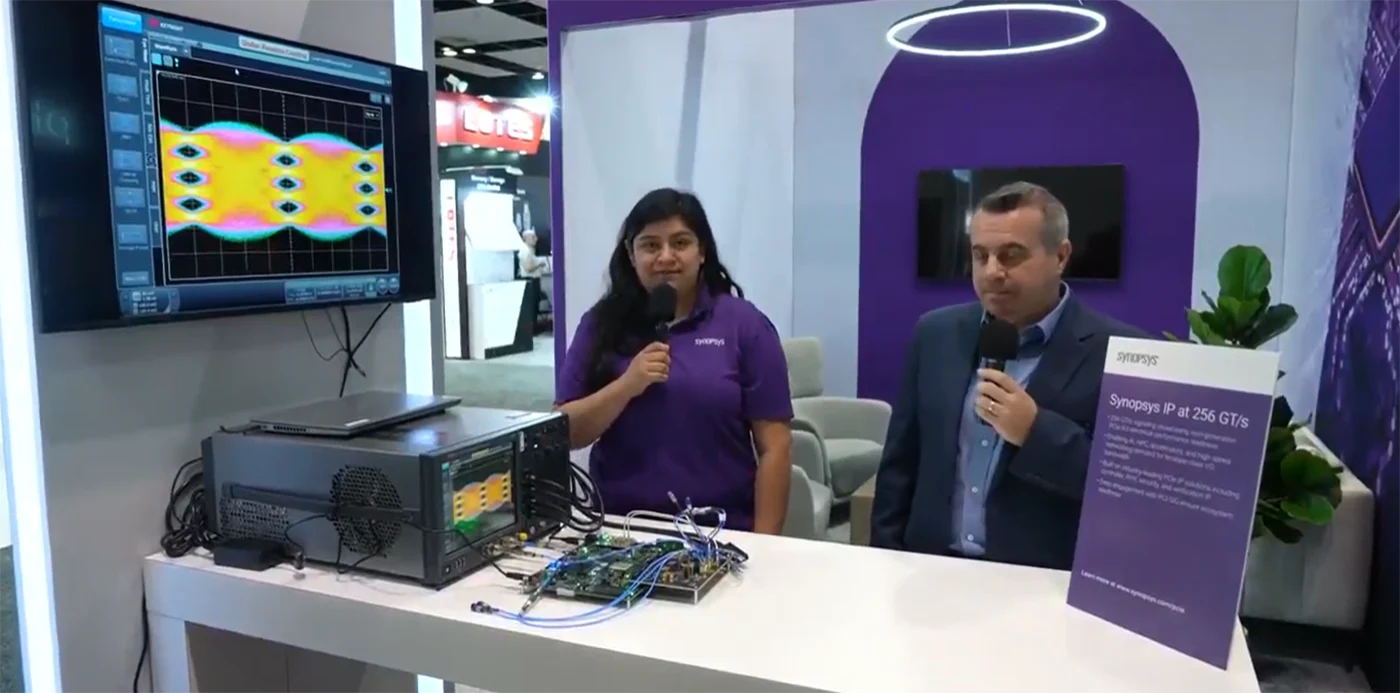

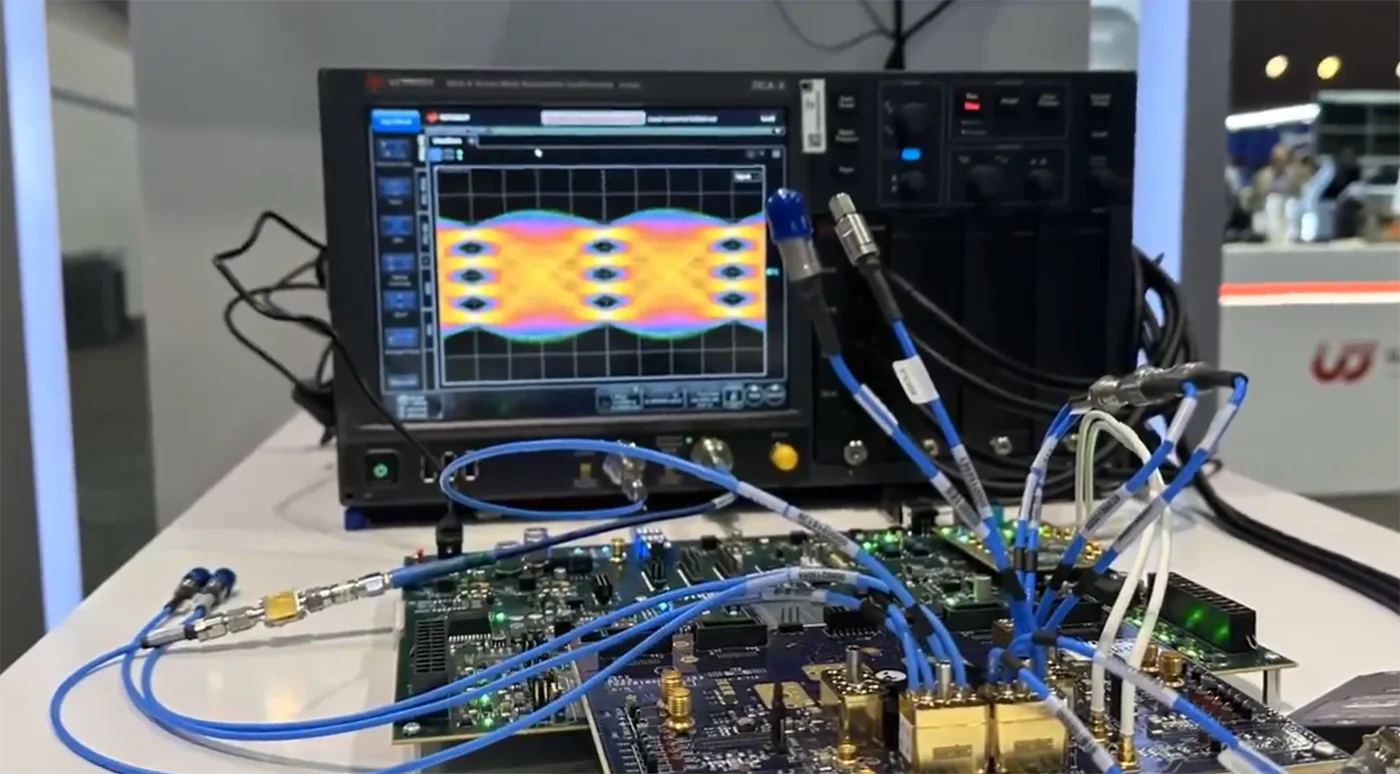

Synopsys PCIe 8.0 演示

- 眼图分析:以 256 GT/s 的速率可视化信号完整性和质量

- 接收器性能验证:验证正确检测和处理高速信号的能力

- 链路训练和同步:确保设备之间的稳定通信

PCIe 带宽如何演变

PCIe 带宽多年来的发展表明,数据传输能力的提升速度有多快。

| 新一代 PCIe | 引入年份 | x16 带宽(双向) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/秒 |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | 预计 ~2028 | ~1 TB/s |

如果目前的路线图成立,那么 理论上,PCIe 8.0 x16 插槽每秒可双向传输约 1 TB 的数据。.与前几代人相比,这是一个巨大的飞跃。

PCIe 8.0 背后的技术

要达到这样的极限速度,需要在信号传输和误差管理方面进行重大创新。其中一项最重要的技术是 PAM4(四级脉冲幅度调制).与使用简单二进制信号的前几代 PCIe 不同,PAM4 通过使用多个电压电平,允许每个信号周期携带更多信息。

虽然这种方法大大增加了带宽,但也带来了更高的错误率。为了保持可靠性,新一代 PCIe 使用 前向纠错 (FEC)在传输过程中检测并纠正错误。PCIe 6.0 引入了这些技术,PCIe 8.0 将进一步扩展这些技术,以支持更高的速度。

另一个重要概念是 基于闪烁的数据传输即以固定大小的数据单元发送信息。这种方法提高了效率,简化了极速通信链路的纠错工作。

这些技术结合在一起,使数据的传输速度成为可能,而使用传统的信号传输方式是不切实际的。

业界为何需要更快的 PCIe

推动 PCIe 8.0 发展的主要动力来自于以下方面的快速增长 人工智能计算和数据中心工作负载.现代人工智能服务器通常包含多个 GPU 或专用加速器,它们必须在训练和推理任务期间交换大量数据。这些系统在很大程度上依赖于高带宽内部连接。

随着模型的增大和数据集的扩展,对组件之间更快通信的需求也在不断增加。高性能计算(HPC)、云基础设施和大规模存储系统也面临着类似的挑战。

在这些环境中,速度更快的 PCIe 连接可以实现:

GPU 与 CPU 的通信效率更高

更快共享训练数据的人工智能加速器

提供更高吞吐量的 NVMe 存储阵列

网络硬件以更低的延迟移动数据

如果不不断提高互连带宽,未来计算系统的性能最终将受限于通信瓶颈,而不是处理能力。

PCIe 8.0 何时上市

尽管最近进行了演示,但 PCIe 8.0 仍处于早期开发阶段。该标准由 PCI-SIG,最终规格预计在 2028.商用硬件通常在新规范定稿几年后才会出现。一个现实的采用时间表可能是这样的:

| 舞台 | 预计时间框架 |

|---|---|

| 规格定稿 | ~2028 |

| 早期硅原型 | 2028-2029 |

| 采用数据中心 | 2030 年左右 |

| 消费类个人电脑 | 2030 年代初 |

目前,PCIe 5.0 和 PCIe 6.0 是与当前硬件开发最相关的两代产品。

PCIe 8.0 技术的首次公开展示是计算行业的一个早期但重要的里程碑。它证实了 PCIe 路线图的下一步在技术上是可以实现的,而且由芯片设计人员、连接器制造商和系统供应商组成的生态系统已经为此做好了准备。虽然日常用户在几年内还看不到 PCIe 8.0 设备,但今天测试的技术最终将支持未来人工智能服务、云平台和高性能计算系统背后的数据基础设施。