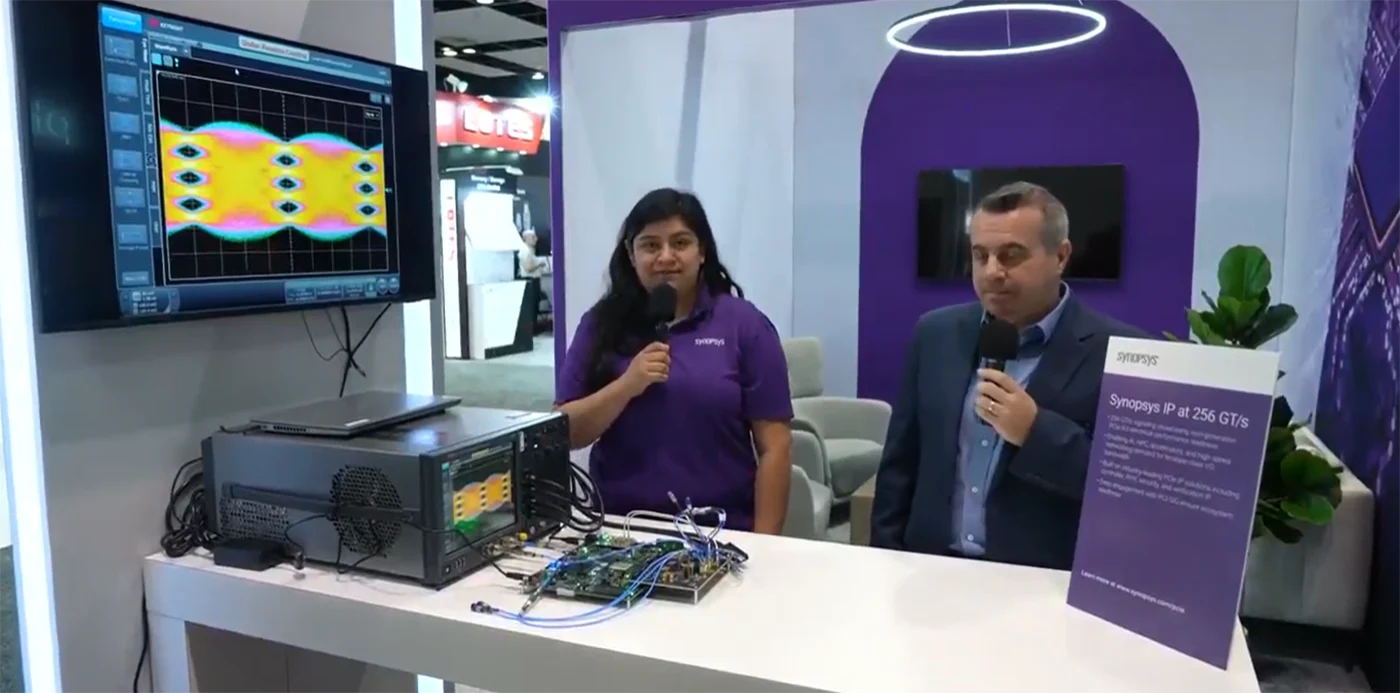

PCIe 8.0-Demonstration von Synopsys

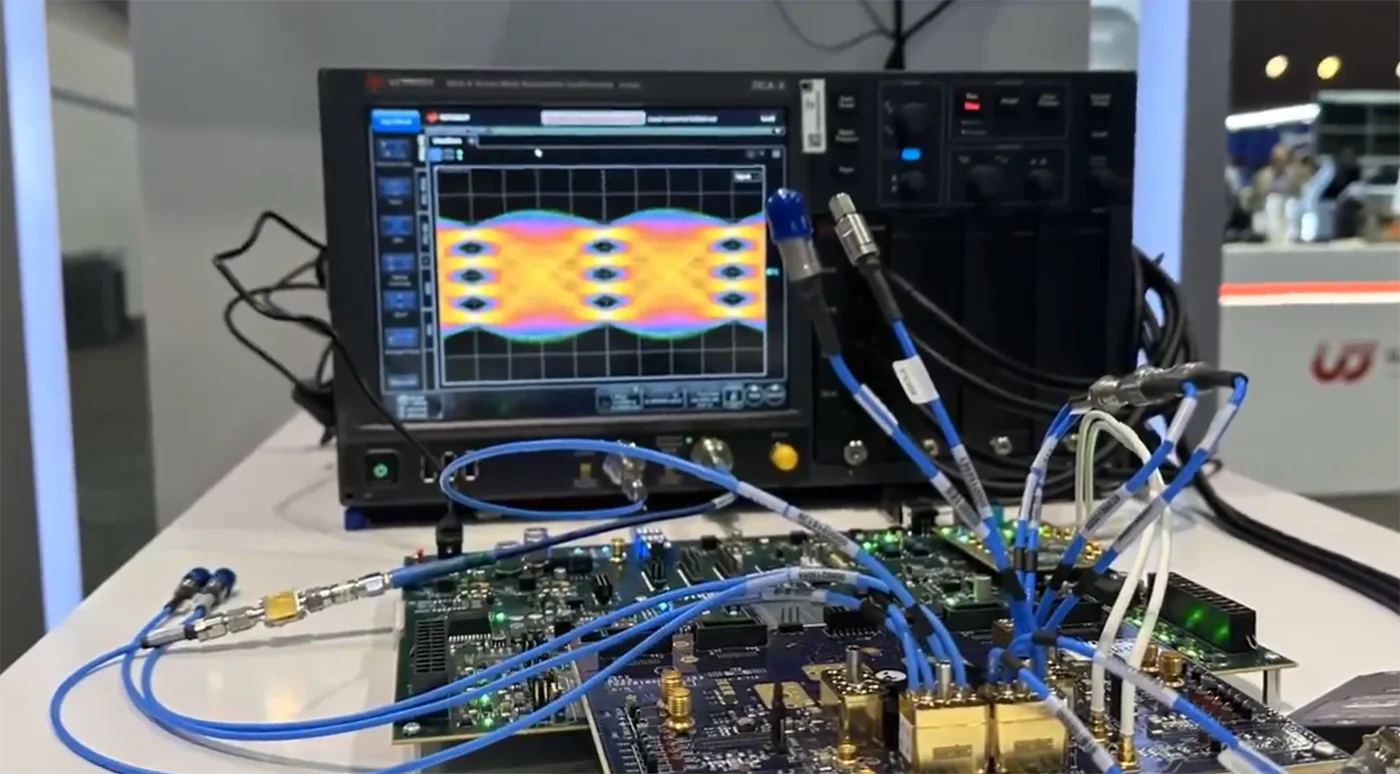

- Analyse des Augendiagramms: Visualisierung der Signalintegrität und -qualität bei 256 GT/s-Raten

- Validierung der Leistung des Empfängers: Überprüfung der Fähigkeit, Hochgeschwindigkeitssignale korrekt zu erkennen und zu verarbeiten

- Link-Training und Synchronisierung: Gewährleistung einer stabilen Kommunikation zwischen Geräten

Wie sich die PCIe-Bandbreite entwickelt hat

Die Entwicklung der PCIe-Bandbreite im Laufe der Jahre verdeutlicht, wie schnell die Datenübertragungsmöglichkeiten gestiegen sind.

| PCIe-Generation | Jahr der Einführung | x16 Bandbreite (bi-direktional) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Voraussichtlich ~2028 | ~1 TB/s |

Wenn der derzeitige Fahrplan eingehalten wird, wird eine Der PCIe 8.0 x16-Steckplatz könnte theoretisch etwa ein Terabyte an Daten pro Sekunde in beide Richtungen zusammen übertragen. Das ist ein dramatischer Sprung im Vergleich zu früheren Generationen.

Die Technologie hinter PCIe 8.0

Um solche extremen Geschwindigkeiten zu erreichen, sind große Innovationen bei der Signalübertragung und dem Fehlermanagement erforderlich. Eine der wichtigsten Technologien dabei ist PAM4 (Puls-Amplituden-Modulation mit vier Stufen). Im Gegensatz zu früheren PCIe-Generationen, die eine einfache binäre Signalisierung verwendeten, ermöglicht PAM4, dass jeder Signalzyklus durch die Verwendung mehrerer Spannungspegel mehr Informationen übertragen kann.

Dieser Ansatz erhöht zwar die Bandbreite drastisch, führt aber auch zu höheren Fehlerraten. Um die Zuverlässigkeit zu gewährleisten, verwenden neuere PCIe-Generationen Vorwärts-Fehlerkorrektur (FEC)die Fehler während der Übertragung erkennt und korrigiert. PCIe 6.0 führte diese Techniken ein, und PCIe 8.0 wird sie weiter ausbauen, um noch höhere Geschwindigkeiten zu unterstützen.

Ein weiteres wichtiges Konzept ist flitbasierte Datenübertragung, bei dem die Informationen in Dateneinheiten fester Größe übertragen werden. Diese Methode verbessert die Effizienz und vereinfacht die Fehlerkorrektur bei extrem schnellen Kommunikationsverbindungen.

Zusammen ermöglichen diese Technologien eine Datenübertragung mit Geschwindigkeiten, die mit herkömmlichen Signalisierungsmethoden nicht möglich gewesen wären.

Warum die Industrie noch schnelleres PCIe braucht

Der Vorstoß in Richtung PCIe 8.0 wird weitgehend durch das schnelle Wachstum der KI-Computing und Arbeitslasten in Rechenzentren. Moderne KI-Server enthalten oft mehrere Grafikprozessoren oder spezielle Beschleuniger, die während des Trainings und der Inferenzaufgaben enorme Datenmengen austauschen müssen. Diese Systeme sind in hohem Maße auf interne Verbindungen mit hoher Bandbreite angewiesen.

Da die Modelle immer größer und die Datensätze immer umfangreicher werden, steigt die Nachfrage nach einer schnelleren Kommunikation zwischen den Komponenten immer weiter an. High-Performance-Computing (HPC), Cloud-Infrastruktur und große Speichersysteme stehen vor ähnlichen Herausforderungen.

In diesen Umgebungen ermöglichen schnellere PCIe-Verbindungen:

GPUs können effizienter mit CPUs kommunizieren

KI-Beschleuniger zur schnelleren Freigabe von Trainingsdaten

NVMe-Speicher-Arrays für höheren Durchsatz

Netzwerkhardware zur Übertragung von Daten mit geringerer Latenzzeit

Ohne eine kontinuierliche Verbesserung der Verbindungsbandbreite würde die Leistung künftiger Computersysteme letztendlich durch Kommunikationsengpässe und nicht durch die Verarbeitungsleistung begrenzt werden.

Wann wird PCIe 8.0 verfügbar sein?

Trotz der jüngsten Demonstration befindet sich PCIe 8.0 noch in einem frühen Entwicklungsstadium. Der Standard wird derzeit definiert von PCI-SIGund die endgültige Spezifikation wird voraussichtlich um 2028. Kommerzielle Hardware erscheint in der Regel mehrere Jahre nach der Fertigstellung einer neuen Spezifikation. Ein realistischer Zeitplan für die Einführung könnte folgendermaßen aussehen:

| Bühne | Geschätzter Zeitrahmen |

|---|---|

| Spezifikation fertiggestellt | ~2028 |

| Frühe Silizium-Prototypen | 2028-2029 |

| Einführung von Rechenzentren | Um 2030 |

| Verbraucher-PCs | Anfang der 2030er Jahre |

Im Moment sind PCIe 5.0 und PCIe 6.0 die für die aktuelle Hardwareentwicklung relevantesten Generationen.

Die erste öffentliche Demonstration der PCIe 8.0-Technologie ist ein früher, aber wichtiger Meilenstein für die Computerindustrie. Sie bestätigt, dass der nächste Schritt in der PCIe-Roadmap technisch realisierbar ist und dass sich das Ökosystem aus Chipdesignern, Steckverbinderherstellern und Systemanbietern bereits darauf vorbereitet. Während alltägliche Nutzer PCIe 8.0-Geräte erst in einigen Jahren sehen werden, wird die heute getestete Technologie schließlich die Dateninfrastruktur hinter den KI-Diensten, Cloud-Plattformen und Hochleistungs-Computersystemen von morgen unterstützen.