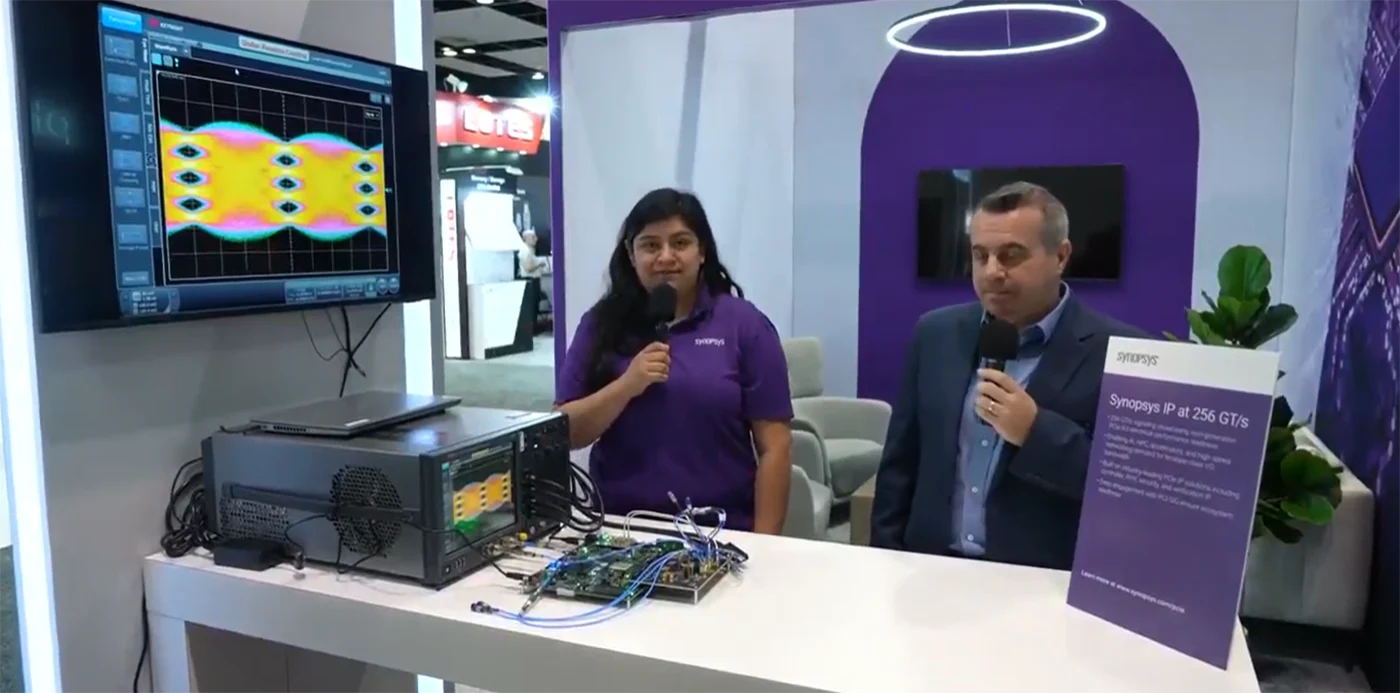

Demonstração do PCIe 8.0 da Synopsys

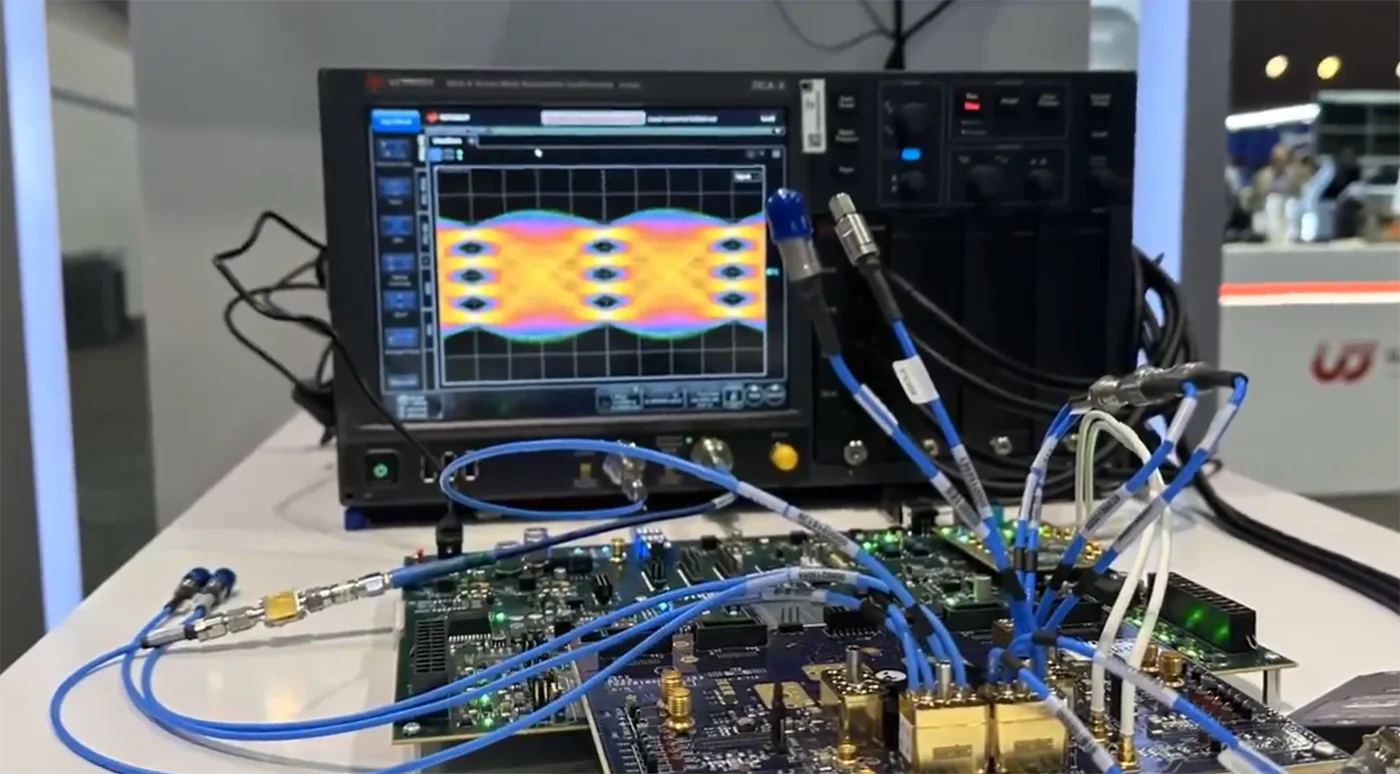

- Análise do diagrama ocular: Visualização da integridade e qualidade do sinal a taxas de 256 GT/s

- Validação do desempenho do recetor: Verificar a capacidade de detetar e processar corretamente sinais de alta velocidade

- Treino e sincronização de ligações: Garantir uma comunicação estável entre dispositivos

Como a largura de banda PCIe evoluiu

A progressão da largura de banda PCIe ao longo dos anos ilustra a rapidez com que as capacidades de transferência de dados aumentaram.

| Geração PCIe | Ano de introdução | Largura de banda x16 (bidirecional) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Previsto para ~2028 | ~1 TB/s |

Se o roteiro atual se mantiver, um A ranhura PCIe 8.0 x16 pode, teoricamente, movimentar cerca de um terabyte de dados por segundo em ambas as direcções combinadas. Isto representa um salto dramático em comparação com as gerações anteriores.

A tecnologia por trás do PCIe 8.0

Atingir velocidades tão extremas exige grandes inovações na transmissão de sinais e na gestão de erros. Uma das mais importantes tecnologias envolvidas é PAM4 (Modulação de Amplitude de Impulso com quatro níveis). Ao contrário das gerações anteriores de PCIe que utilizavam uma sinalização binária simples, o PAM4 permite que cada ciclo de sinal transporte mais informações através da utilização de vários níveis de tensão.

Embora esta abordagem aumente drasticamente a largura de banda, também introduz taxas de erro mais elevadas. Para manter a fiabilidade, as gerações mais recentes de PCIe utilizam Correção de erros de avanço (FEC)que detecta e corrige erros durante a transmissão. O PCIe 6.0 introduziu estas técnicas, e o PCIe 8.0 irá alargá-las ainda mais para suportar velocidades ainda mais elevadas.

Outro conceito importante é transmissão de dados baseada em flitsem que a informação é enviada em unidades de dados de tamanho fixo. Este método melhora a eficiência e simplifica a correção de erros em ligações de comunicação extremamente rápidas.

Em conjunto, estas tecnologias permitem mover dados a velocidades que seriam impraticáveis utilizando métodos de sinalização tradicionais.

Porque é que a indústria precisa de PCIe ainda mais rápido

O impulso para o PCIe 8.0 é largamente impulsionado pelo rápido crescimento do Computação de IA e cargas de trabalho do centro de dados. Os servidores de IA modernos contêm frequentemente várias GPUs ou aceleradores especializados que têm de trocar enormes quantidades de dados durante as tarefas de formação e inferência. Estes sistemas dependem fortemente de ligações internas de elevada largura de banda.

À medida que os modelos se tornam maiores e os conjuntos de dados se expandem, a procura de uma comunicação mais rápida entre componentes continua a aumentar. A computação de alto desempenho (HPC), a infraestrutura de nuvem e os sistemas de armazenamento em grande escala enfrentam desafios semelhantes.

Nestes ambientes, as ligações PCIe mais rápidas permitem:

GPUs para comunicar de forma mais eficiente com as CPUs

Aceleradores de IA para partilhar dados de formação mais rapidamente

Matrizes de armazenamento NVMe para oferecer maior rendimento

hardware de rede para mover dados com menor latência

Sem melhorias contínuas na largura de banda de interligação, o desempenho dos futuros sistemas de computação acabaria por ser limitado por estrangulamentos na comunicação e não pela capacidade de processamento.

Quando é que o PCIe 8.0 estará disponível

Apesar da recente demonstração, o PCIe 8.0 ainda se encontra numa fase inicial de desenvolvimento. A norma está a ser definida por PCI-SIGe a especificação final deverá ser de cerca de 2028. O hardware comercial aparece normalmente vários anos após a finalização de uma nova especificação. Um calendário de adoção realista poderia ser o seguinte:

| Estágio | Calendário estimado |

|---|---|

| Especificação finalizada | ~2028 |

| Primeiros protótipos de silício | 2028-2029 |

| Adoção de centros de dados | Por volta de 2030 |

| PCs de consumo | Início da década de 2030 |

Por enquanto, a PCIe 5.0 e a PCIe 6.0 são as gerações mais relevantes para o desenvolvimento atual de hardware.

A primeira demonstração pública da tecnologia PCIe 8.0 representa um marco inicial, mas importante, para o sector da informática. Confirma que o próximo passo no roteiro PCIe é tecnicamente possível e que o ecossistema de designers de chips, fabricantes de conectores e fornecedores de sistemas já está a preparar-se para ele. Embora os utilizadores comuns não vejam dispositivos PCIe 8.0 durante vários anos, a tecnologia que está a ser testada hoje acabará por suportar a infraestrutura de dados por detrás dos serviços de IA, plataformas de nuvem e sistemas de computação de alto desempenho de amanhã.