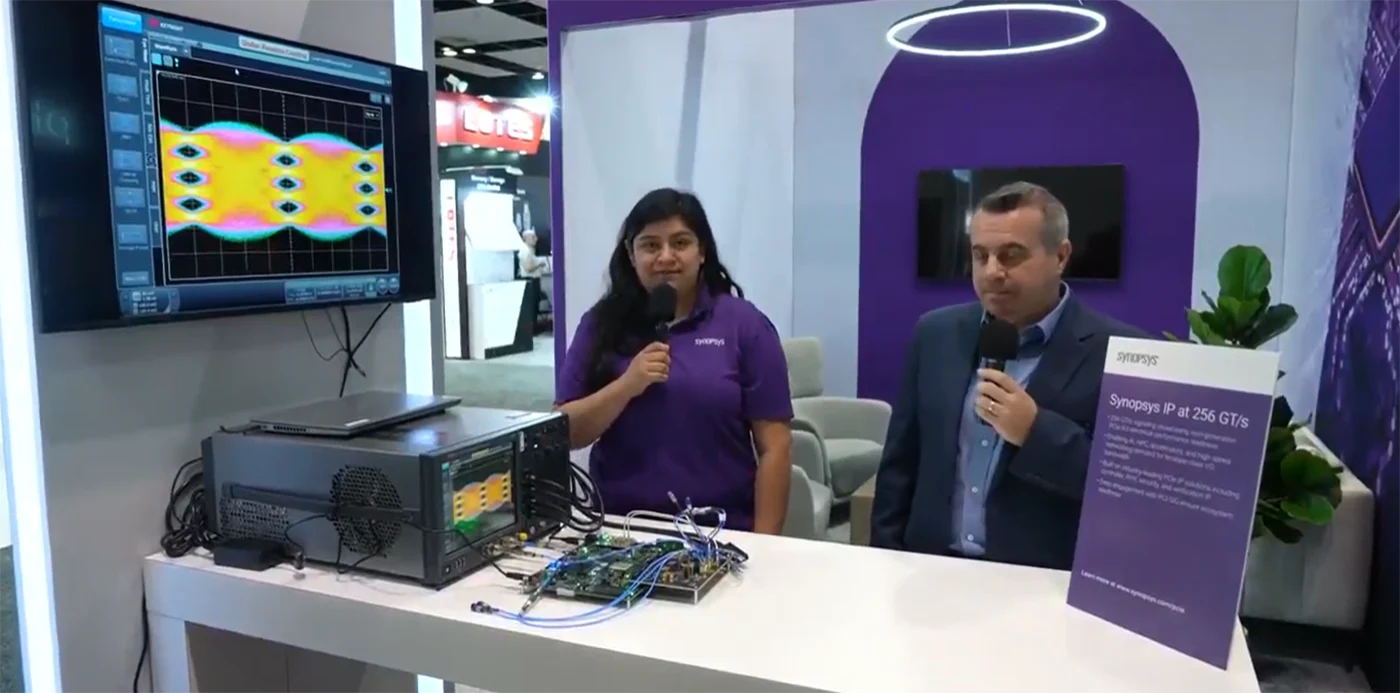

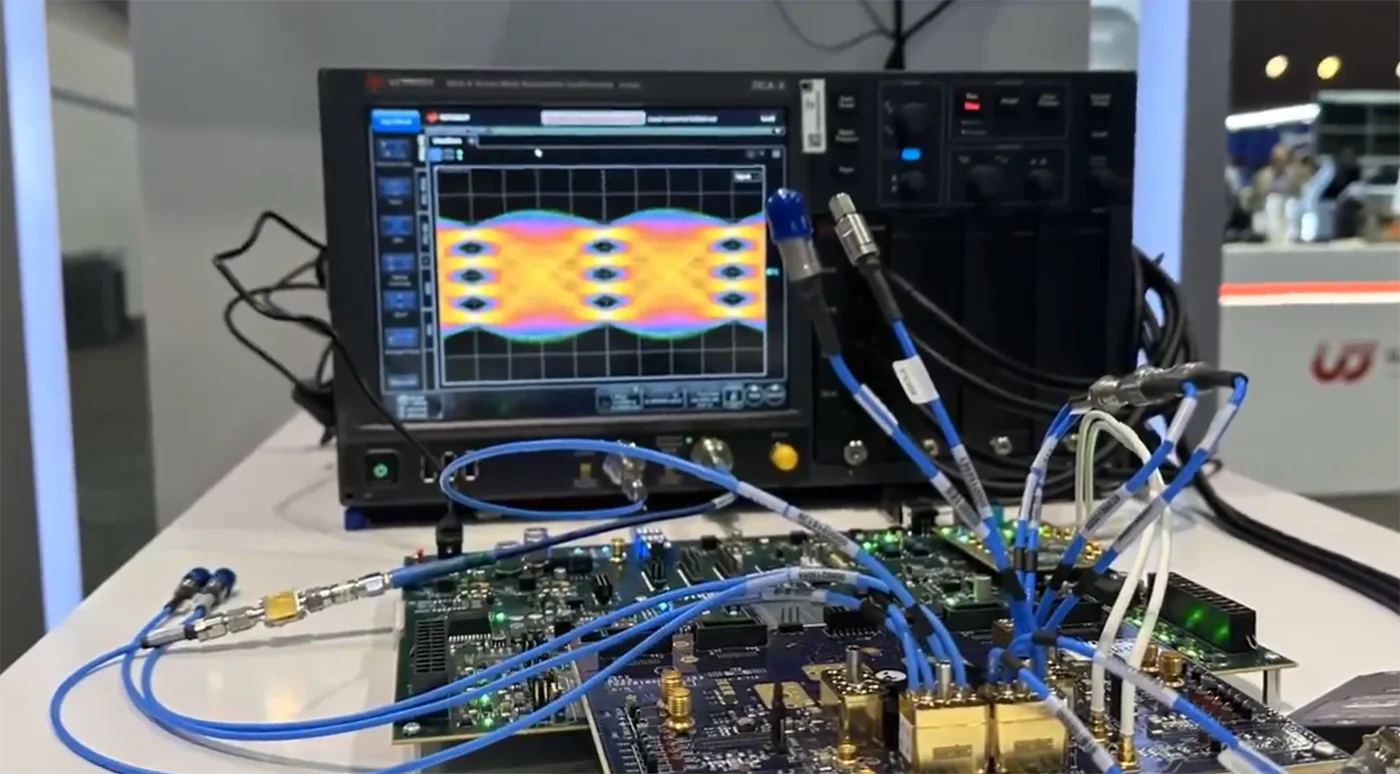

Dimostrazione di PCIe 8.0 di Synopsys

- Analisi del diagramma oculare: Visualizzazione dell'integrità e della qualità del segnale a velocità di 256 GT/s

- Convalida delle prestazioni del ricevitore: Verifica della capacità di rilevare ed elaborare correttamente i segnali ad alta velocità

- Formazione e sincronizzazione dei collegamenti: Garantire una comunicazione stabile tra i dispositivi

Come si è evoluta la larghezza di banda PCIe

La progressione della larghezza di banda PCIe nel corso degli anni illustra la rapidità con cui sono aumentate le capacità di trasferimento dei dati.

| Generazione PCIe | Anno di introduzione | Larghezza di banda x16 (bidirezionale) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Previsto ~2028 | ~1 TB/s |

Se la tabella di marcia attuale è valida, un Lo slot PCIe 8.0 x16 potrebbe teoricamente spostare circa un terabyte di dati al secondo in entrambe le direzioni combinate.. Si tratta di un balzo in avanti notevole rispetto alle generazioni precedenti.

La tecnologia alla base di PCIe 8.0

Il raggiungimento di velocità così estreme richiede importanti innovazioni nella trasmissione dei segnali e nella gestione degli errori. Una delle tecnologie più importanti è PAM4 (modulazione di ampiezza dell'impulso a quattro livelli). A differenza delle generazioni precedenti di PCIe, che utilizzavano una semplice segnalazione binaria, PAM4 consente a ciascun ciclo di segnale di trasportare più informazioni utilizzando più livelli di tensione.

Se da un lato questo approccio aumenta notevolmente la larghezza di banda, dall'altro introduce tassi di errore più elevati. Per mantenere l'affidabilità, le nuove generazioni di PCIe usano Correzione degli errori in avanti (FEC)che rileva e corregge gli errori durante la trasmissione. PCIe 6.0 ha introdotto queste tecniche e PCIe 8.0 le estenderà ulteriormente per supportare velocità ancora più elevate.

Un altro concetto importante è trasmissione dati basata su flitin cui le informazioni vengono inviate in unità di dati di dimensioni fisse. Questo metodo migliora l'efficienza e semplifica la correzione degli errori nei collegamenti di comunicazione estremamente veloci.

Insieme, queste tecnologie consentono di spostare i dati a velocità che non sarebbero state possibili con i metodi di segnalazione tradizionali.

Perché il settore ha bisogno di un PCIe ancora più veloce

La spinta verso il PCIe 8.0 è in gran parte guidata dalla rapida crescita di Calcolo dell'intelligenza artificiale e carichi di lavoro dei data center. I moderni server di intelligenza artificiale spesso contengono più GPU o acceleratori specializzati che devono scambiare enormi quantità di dati durante le attività di formazione e inferenza. Questi sistemi dipendono fortemente dalle connessioni interne ad alta larghezza di banda.

Con l'ingrandimento dei modelli e l'espansione dei set di dati, la richiesta di comunicazioni più veloci tra i componenti continua a crescere. Il calcolo ad alte prestazioni (HPC), l'infrastruttura cloud e i sistemi di archiviazione su larga scala devono affrontare sfide simili.

In questi ambienti, le connessioni PCIe più veloci consentono:

Le GPU comunicano in modo più efficiente con le CPU.

Acceleratori di IA per condividere più velocemente i dati di formazione

Gli array di archiviazione NVMe offrono un throughput più elevato

hardware di rete per spostare i dati con una latenza inferiore

Senza continui miglioramenti nella larghezza di banda delle interconnessioni, le prestazioni dei futuri sistemi di elaborazione finiranno per essere limitate dai colli di bottiglia della comunicazione piuttosto che dalla potenza di elaborazione.

Quando sarà disponibile il PCIe 8.0

Nonostante la recente dimostrazione, PCIe 8.0 è ancora in una fase iniziale di sviluppo. Lo standard è stato definito da PCI-SIGe la specifica finale è prevista intorno a 2028. L'hardware commerciale compare in genere diversi anni dopo la finalizzazione di una nuova specifica. Una tempistica di adozione realistica potrebbe essere la seguente:

| Palcoscenico | Tempi stimati |

|---|---|

| Specifiche finalizzate | ~2028 |

| I primi prototipi di silicio | 2028-2029 |

| Adozione dei data center | Intorno al 2030 |

| PC consumer | Inizio 2030 |

Per ora, PCIe 5.0 e PCIe 6.0 sono le generazioni più rilevanti per lo sviluppo attuale dell'hardware.

La prima dimostrazione pubblica della tecnologia PCIe 8.0 rappresenta una prima ma importante pietra miliare per il settore informatico. Conferma che il prossimo passo della roadmap PCIe è tecnicamente realizzabile e che l'ecosistema di progettisti di chip, produttori di connettori e fornitori di sistemi si sta già preparando. Anche se gli utenti di tutti i giorni non vedranno i dispositivi PCIe 8.0 prima di diversi anni, la tecnologia testata oggi finirà per supportare l'infrastruttura dati alla base dei servizi AI, delle piattaforme cloud e dei sistemi di elaborazione ad alte prestazioni di domani.