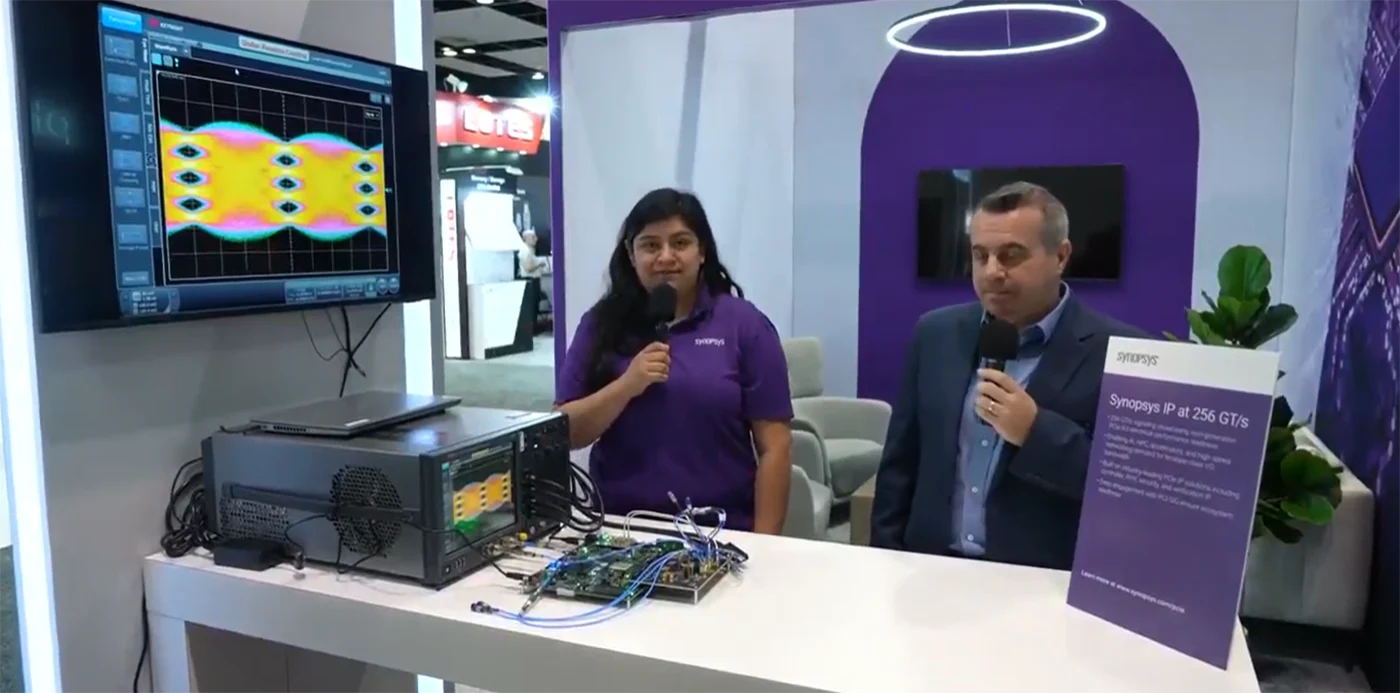

Démonstration PCIe 8.0 de Synopsys

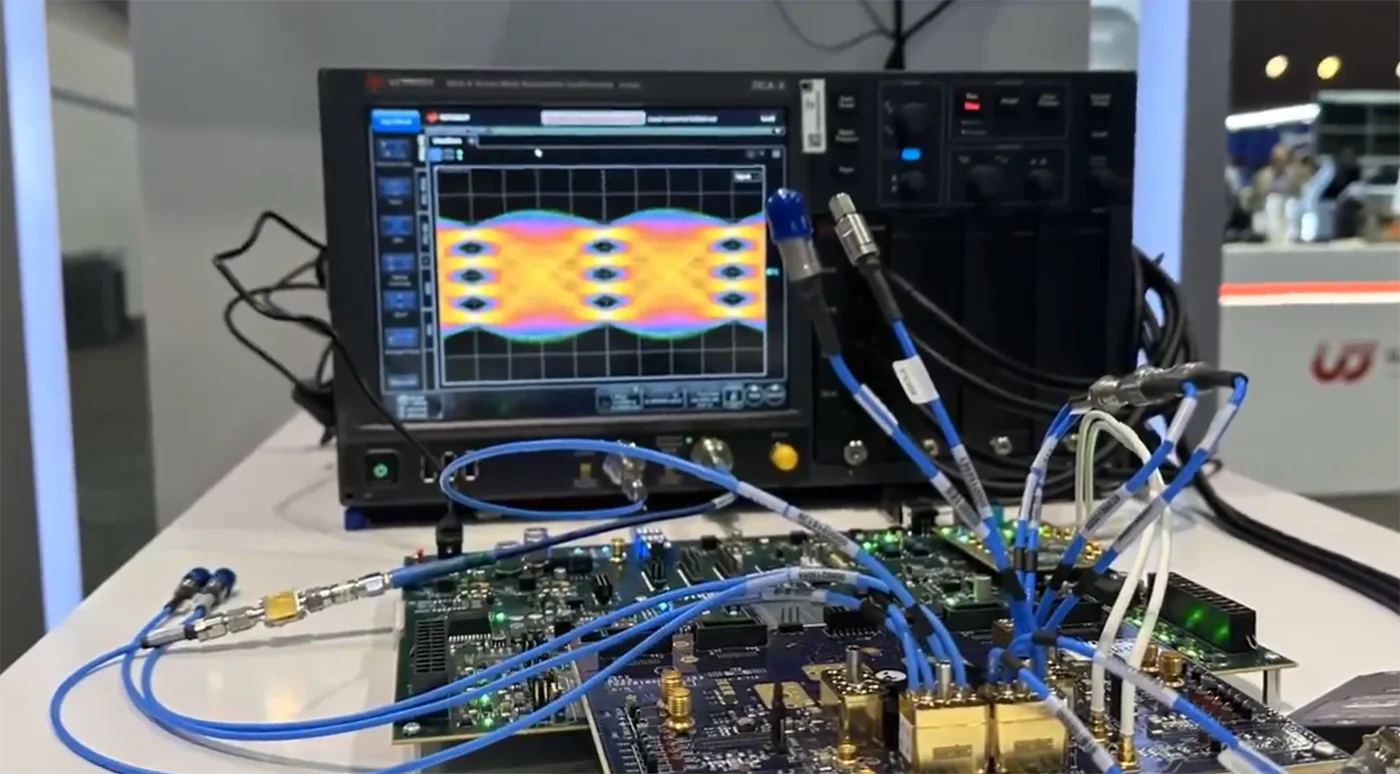

- Analyse du diagramme de l'œil: Visualisation de l'intégrité et de la qualité du signal à des taux de 256 GT/s

- Validation des performances du récepteur: Vérification de la capacité à détecter et à traiter correctement les signaux à grande vitesse

- Formation et synchronisation des liens: Assurer une communication stable entre les appareils

Évolution de la bande passante PCIe

La progression de la bande passante PCIe au fil des ans illustre la rapidité avec laquelle les capacités de transfert de données ont augmenté.

| Génération PCIe | Année d'introduction | Largeur de bande x16 (bidirectionnelle) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 Go/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Prévu pour ~2028 | ~1 TB/s |

Si la feuille de route actuelle est maintenue, un L'emplacement PCIe 8.0 x16 pourrait théoriquement déplacer environ un téraoctet de données par seconde dans les deux sens combinés.. Cela représente un bond spectaculaire par rapport aux générations précédentes.

La technologie derrière PCIe 8.0

Atteindre de telles vitesses extrêmes nécessite des innovations majeures dans la transmission des signaux et la gestion des erreurs. L'une des technologies les plus importantes est PAM4 (modulation d'amplitude d'impulsion à quatre niveaux). Contrairement aux générations précédentes de PCIe qui utilisaient une simple signalisation binaire, PAM4 permet à chaque cycle de signal de transporter plus d'informations en utilisant plusieurs niveaux de tension.

Si cette approche augmente considérablement la largeur de bande, elle introduit également des taux d'erreur plus élevés. Pour maintenir la fiabilité, les nouvelles générations de cartes PCIe utilisent des cartes Correction d'erreur directe (FEC)qui détecte et corrige les erreurs pendant la transmission. La norme PCIe 6.0 a introduit ces techniques, et la norme PCIe 8.0 les étendra encore davantage pour prendre en charge des vitesses encore plus élevées.

Un autre concept important est transmission de données par flitCette méthode améliore l'efficacité et simplifie la correction des erreurs dans les liaisons de communication extrêmement rapides. Cette méthode améliore l'efficacité et simplifie la correction des erreurs dans les liaisons de communication extrêmement rapides.

Ensemble, ces technologies permettent de transmettre des données à des vitesses qui n'auraient pas été possibles avec les méthodes de signalisation traditionnelles.

Pourquoi l'industrie a besoin d'une interface PCIe encore plus rapide

Le passage à la norme PCIe 8.0 est largement motivé par la croissance rapide de l'industrie de l'automobile. Calcul de l'IA et charges de travail des centres de données. Les serveurs d'IA modernes contiennent souvent plusieurs GPU ou accélérateurs spécialisés qui doivent échanger d'énormes quantités de données pendant les tâches d'apprentissage et d'inférence. Ces systèmes dépendent fortement de connexions internes à large bande passante.

À mesure que les modèles prennent de l'ampleur et que les ensembles de données se multiplient, la demande de communication plus rapide entre les composants ne cesse d'augmenter. Le calcul haute performance (HPC), l'infrastructure en nuage et les systèmes de stockage à grande échelle sont confrontés à des défis similaires.

Dans ces environnements, des connexions PCIe plus rapides permettent :

Les GPU communiquent plus efficacement avec les CPU

Des accélérateurs d'IA pour partager plus rapidement les données d'entraînement

Les baies de stockage NVMe offrent un débit plus élevé

le matériel de mise en réseau pour déplacer les données avec un temps de latence plus faible

Sans une amélioration continue de la largeur de bande des interconnexions, les performances des futurs systèmes informatiques seront finalement limitées par les goulets d'étranglement de la communication plutôt que par la puissance de traitement.

Quand la norme PCIe 8.0 sera-t-elle disponible ?

Malgré la récente démonstration, la norme PCIe 8.0 en est encore à un stade de développement précoce. La norme est définie par PCI-SIGet la spécification finale devrait se situer aux alentours de 2028. Le matériel commercial apparaît généralement plusieurs années après la finalisation d'une nouvelle spécification. Un calendrier d'adoption réaliste pourrait ressembler à ceci :

| Stade | Calendrier estimé |

|---|---|

| Finalisation de la spécification | ~2028 |

| Premiers prototypes en silicone | 2028-2029 |

| Adoption des centres de données | Vers 2030 |

| PC grand public | Début des années 2030 |

Pour l'instant, PCIe 5.0 et PCIe 6.0 sont les générations les plus pertinentes pour le développement actuel du matériel.

La première démonstration publique de la technologie PCIe 8.0 représente une étape précoce mais importante pour l'industrie informatique. Elle confirme que la prochaine étape de la feuille de route PCIe est techniquement réalisable et que l'écosystème des concepteurs de puces, des fabricants de connecteurs et des fournisseurs de systèmes s'y prépare déjà. Même si les utilisateurs quotidiens ne verront pas de dispositifs PCIe 8.0 avant plusieurs années, la technologie testée aujourd'hui finira par prendre en charge l'infrastructure de données derrière les services d'IA, les plateformes cloud et les systèmes de calcul à haute performance de demain.