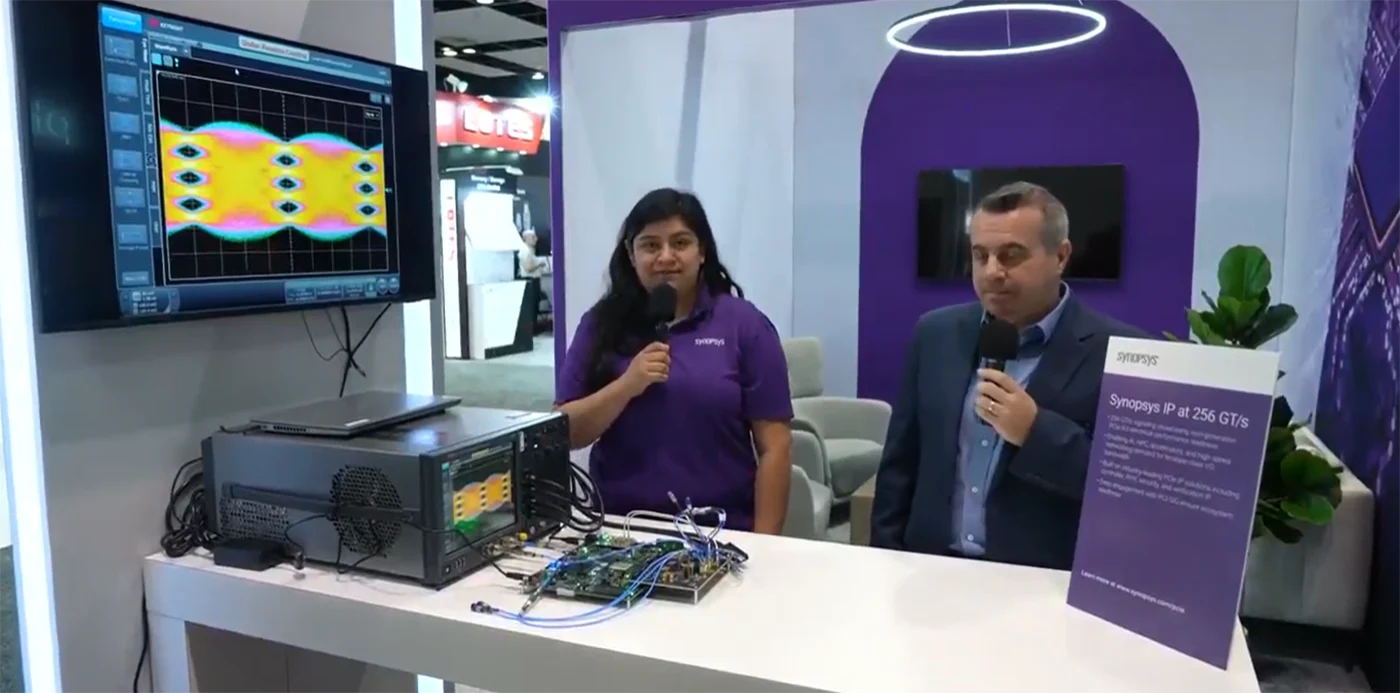

Demostración de PCIe 8.0 de Synopsys

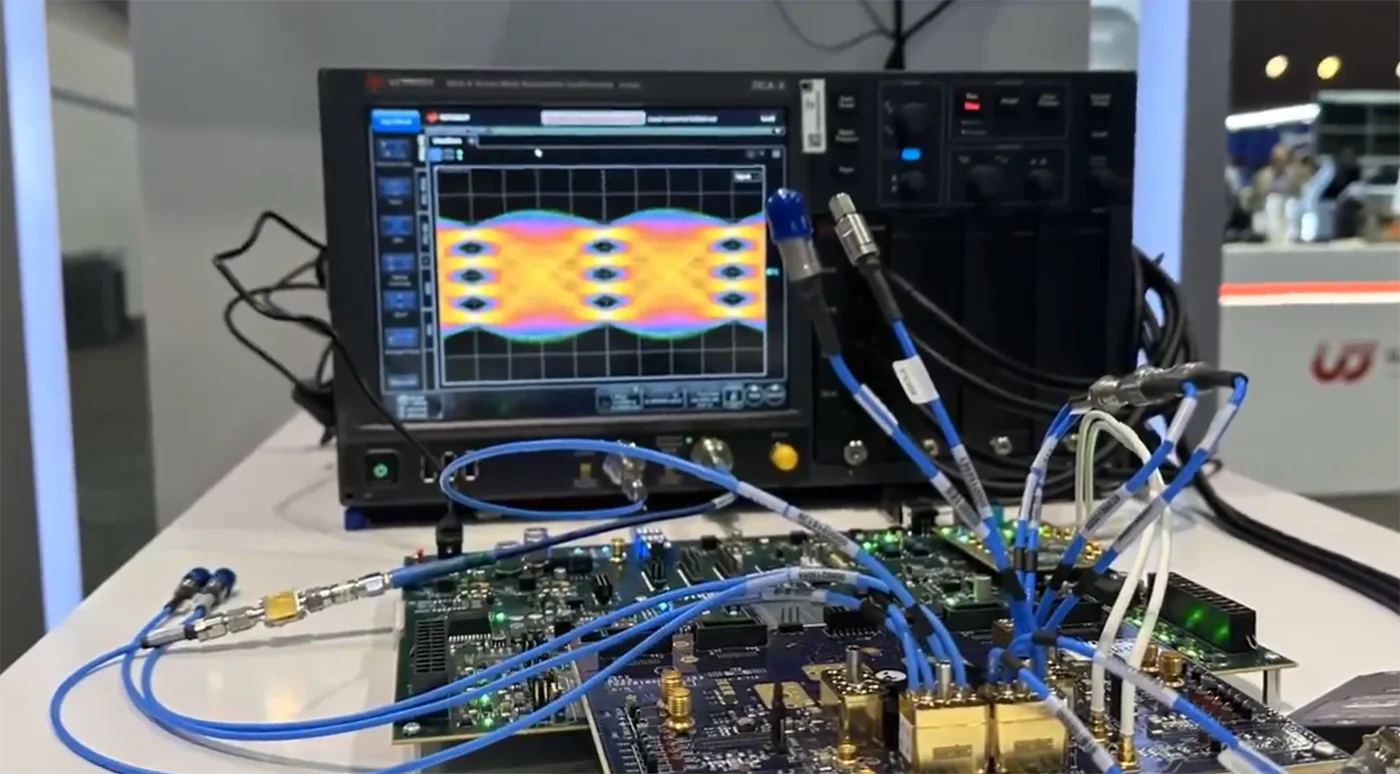

- Análisis del diagrama ocular: Visualización de la integridad y calidad de la señal a velocidades de 256 GT/s

- Validación del rendimiento del receptor: Verificación de la capacidad de detectar y procesar correctamente señales de alta velocidad

- Formación y sincronización de enlaces: Garantizar una comunicación estable entre dispositivos

Evolución del ancho de banda PCIe

La progresión del ancho de banda PCIe a lo largo de los años ilustra lo rápido que ha aumentado la capacidad de transferencia de datos.

| Generación PCIe | Año de introducción | x16 Ancho de banda (bidireccional) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 GB/s |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Previsto ~2028 | ~1 TB/s |

Si se mantiene la hoja de ruta actual, se La ranura PCIe 8.0 x16 podría mover en teoría alrededor de un terabyte de datos por segundo en ambas direcciones combinadas. Esto representa un salto espectacular en comparación con las generaciones anteriores.

La tecnología detrás de PCIe 8.0

Alcanzar velocidades tan extremas exige grandes innovaciones en la transmisión de señales y la gestión de errores. Una de las tecnologías más importantes es PAM4 (modulación de amplitud de impulsos con cuatro niveles). A diferencia de las anteriores generaciones de PCIe, que utilizaban señalización binaria simple, PAM4 permite que cada ciclo de señal transporte más información mediante el uso de múltiples niveles de tensión.

Aunque este enfoque aumenta drásticamente el ancho de banda, también introduce mayores tasas de error. Para mantener la fiabilidad, las nuevas generaciones de PCIe utilizan Corrección de errores hacia delante (FEC)que detecta y corrige errores durante la transmisión. PCIe 6.0 introdujo estas técnicas y PCIe 8.0 las ampliará para admitir velocidades aún mayores.

Otro concepto importante es transmisión de datos basada en flitsdonde la información se envía en unidades de datos de tamaño fijo. Este método mejora la eficiencia y simplifica la corrección de errores en enlaces de comunicación extremadamente rápidos.

Juntas, estas tecnologías permiten mover datos a velocidades que habrían sido impracticables con los métodos de señalización tradicionales.

Por qué la industria necesita PCIe aún más rápido

El empuje hacia PCIe 8.0 está impulsado en gran medida por el rápido crecimiento del Informática de IA y cargas de trabajo del centro de datos. Los servidores de IA modernos suelen contener varias GPU o aceleradores especializados que deben intercambiar enormes cantidades de datos durante las tareas de entrenamiento e inferencia. Estos sistemas dependen en gran medida de conexiones internas de gran ancho de banda.

A medida que los modelos crecen y los conjuntos de datos se amplían, aumenta la demanda de una comunicación más rápida entre los componentes. La informática de alto rendimiento (HPC), la infraestructura en la nube y los sistemas de almacenamiento a gran escala se enfrentan a retos similares.

En estos entornos, las conexiones PCIe más rápidas permiten:

Las GPU se comunican mejor con las CPU

Aceleradores de IA para compartir más rápido los datos de entrenamiento

Matrices de almacenamiento NVMe para ofrecer mayor rendimiento

hardware de red para mover datos con menor latencia

Sin mejoras continuas en el ancho de banda de interconexión, el rendimiento de los futuros sistemas informáticos acabará viéndose limitado por los cuellos de botella de las comunicaciones y no por la potencia de procesamiento.

Cuándo estará disponible PCIe 8.0

A pesar de la reciente demostración, PCIe 8.0 aún se encuentra en una fase temprana de desarrollo. La norma está siendo definida por PCI-SIGy la especificación final se espera en torno a 2028. El hardware comercial suele aparecer varios años después de que se finalice una nueva especificación. Un calendario de adopción realista podría ser el siguiente:

| Escenario | Calendario estimado |

|---|---|

| Especificación finalizada | ~2028 |

| Primeros prototipos de silicio | 2028-2029 |

| Adopción de centros de datos | Hacia 2030 |

| PC de consumo | Principios de 2030 |

Por ahora, PCIe 5.0 y PCIe 6.0 son las generaciones más relevantes para el desarrollo actual de hardware.

La primera demostración pública de la tecnología PCIe 8.0 representa un hito temprano pero importante para la industria informática. Confirma que el siguiente paso en la hoja de ruta de PCIe es técnicamente factible y que el ecosistema de diseñadores de chips, fabricantes de conectores y vendedores de sistemas ya se está preparando para ello. Aunque los usuarios cotidianos no verán dispositivos PCIe 8.0 hasta dentro de varios años, la tecnología que se está probando hoy acabará soportando la infraestructura de datos que subyace a los servicios de inteligencia artificial, las plataformas en la nube y los sistemas informáticos de alto rendimiento del mañana.