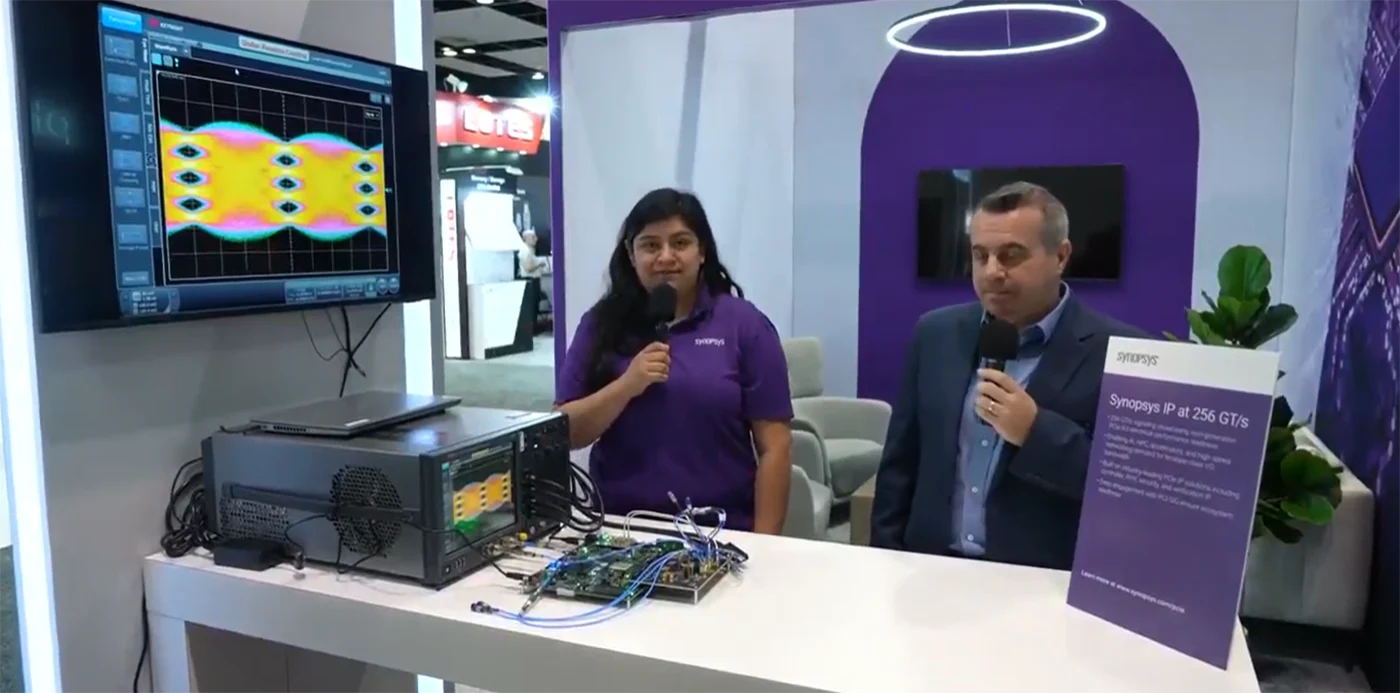

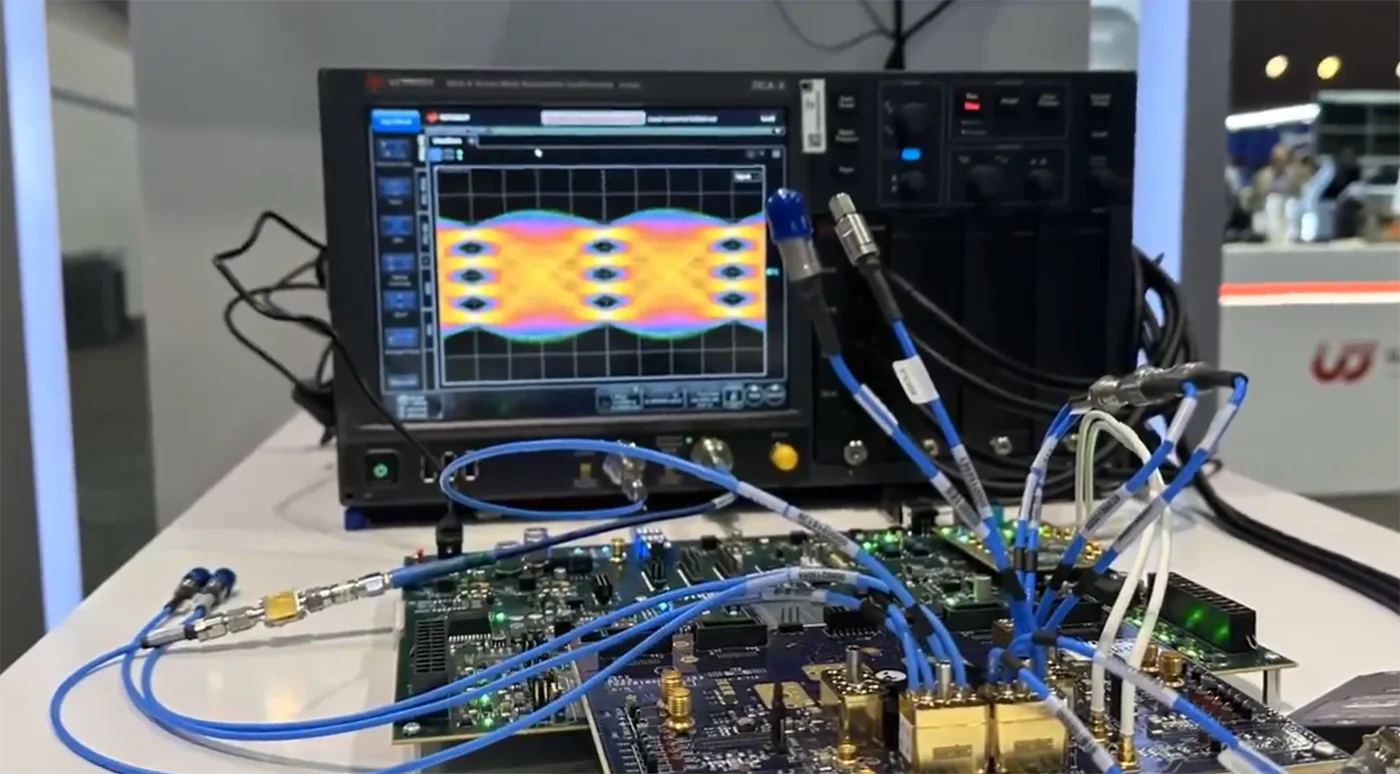

Synopsys' PCIe 8.0 Demonstration

- Eye diagram analysis: Visualizing signal integrity and quality at 256 GT/s rates

- Receiver performance validation: Verifying the ability to correctly detect and process high-speed signals

- Link training and synchronization: Ensuring stable communication between devices

How PCIe Bandwidth Has Evolved

The progression of PCIe bandwidth over the years illustrates just how rapidly data transfer capabilities have increased.

| توليد PCIe | Year Introduced | x16 Bandwidth (Bi-Directional) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 جيجابايت/ثانية |

| PCIe 4.0 | 2017 | 64 GB/s |

| PCIe 5.0 | 2019 | 128 GB/s |

| PCIe 6.0 | 2022 | 256 GB/s |

| PCIe 7.0 | 2025 | 512 GB/s |

| PCIe 8.0 | Expected ~2028 | ~1 TB/s |

If the current roadmap holds, a PCIe 8.0 x16 slot could theoretically move about one terabyte of data per second in both directions combined. That represents a dramatic leap compared with earlier generations.

The Technology Behind PCIe 8.0

Reaching such extreme speeds requires major innovations in signal transmission and error management. One of the most important technologies involved is PAM4 (Pulse Amplitude Modulation with four levels). Unlike earlier PCIe generations that used simple binary signaling, PAM4 allows each signal cycle to carry more information by using multiple voltage levels.

While this approach dramatically increases bandwidth, it also introduces higher error rates. To maintain reliability, newer PCIe generations use Forward Error Correction (FEC), which detects and corrects errors during transmission. PCIe 6.0 introduced these techniques, and PCIe 8.0 will extend them further to support even higher speeds.

Another important concept is flit-based data transmission, where information is sent in fixed-size data units. This method improves efficiency and simplifies error correction in extremely fast communication links.

Together, these technologies make it possible to move data at speeds that would have been impractical using traditional signaling methods.

Why the Industry Needs Even Faster PCIe

The push toward PCIe 8.0 is largely driven by the rapid growth of AI computing and data-center workloads. Modern AI servers often contain multiple GPUs or specialized accelerators that must exchange enormous amounts of data during training and inference tasks. These systems depend heavily on high-bandwidth internal connections.

As models grow larger and datasets expand, the demand for faster communication between components continues to rise. High-performance computing (HPC), cloud infrastructure, and large-scale storage systems face similar challenges.

In these environments, faster PCIe connections allow:

GPUs to communicate more efficiently with CPUs

AI accelerators to share training data faster

NVMe storage arrays to deliver higher throughput

networking hardware to move data with lower latency

Without continued improvements in interconnect bandwidth, the performance of future computing systems would eventually be limited by communication bottlenecks rather than processing power.

When PCIe 8.0 Will Become Available

Despite the recent demonstration, PCIe 8.0 is still in an early development stage. The standard is being defined by PCI‑SIG, and the final specification is expected around 2028. Commercial hardware typically appears several years after a new specification is finalized. A realistic adoption timeline might look like this:

| Stage | Estimated Timeframe |

|---|---|

| Specification finalized | ~2028 |

| Early silicon prototypes | 2028–2029 |

| Data-center adoption | Around 2030 |

| Consumer PCs | Early 2030s |

For now, PCIe 5.0 and PCIe 6.0 are the generations most relevant to current hardware development.

The first public demonstration of PCIe 8.0 technology represents an early but important milestone for the computing industry. It confirms that the next step in the PCIe roadmap is technically achievable and that the ecosystem of chip designers, connector manufacturers, and system vendors is already preparing for it. While everyday users will not see PCIe 8.0 devices for several years, the technology being tested today will eventually support the data infrastructure behind tomorrow’s AI services, cloud platforms, and high-performance computing systems..