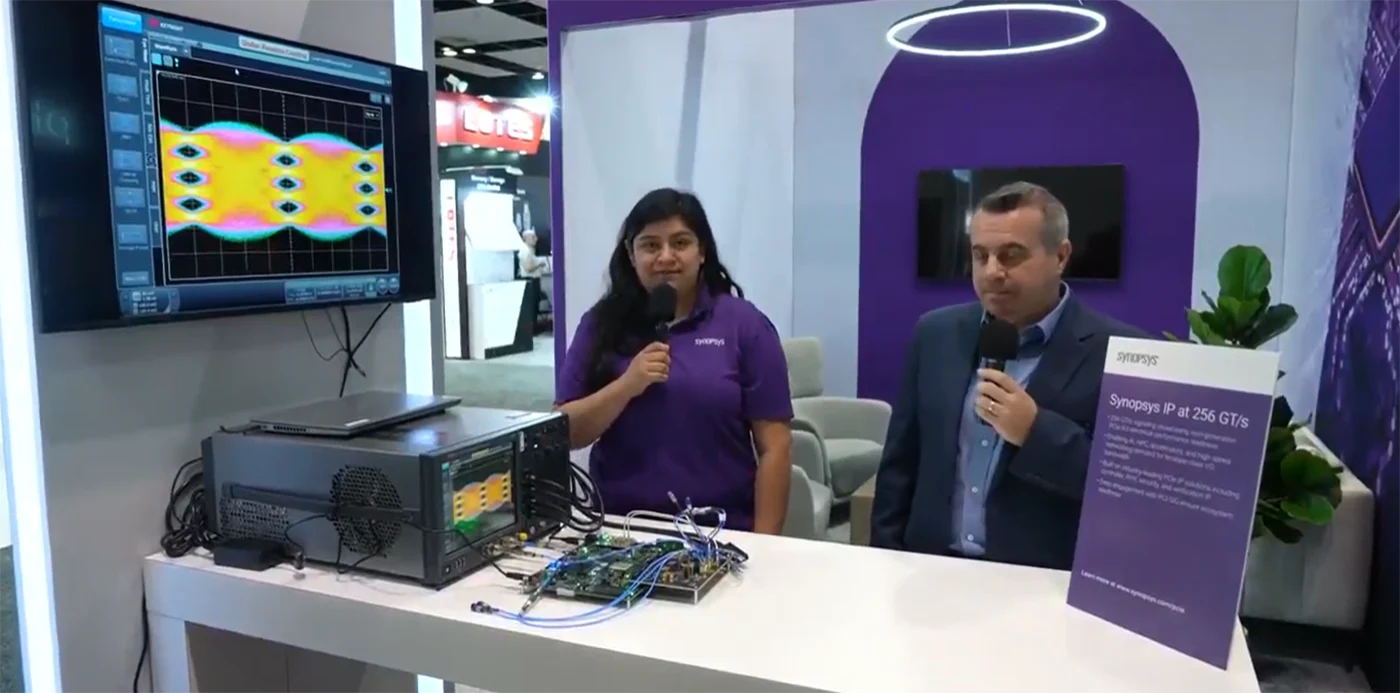

عرض Synopsys 'PCIe 8.0 PCIe 8.0

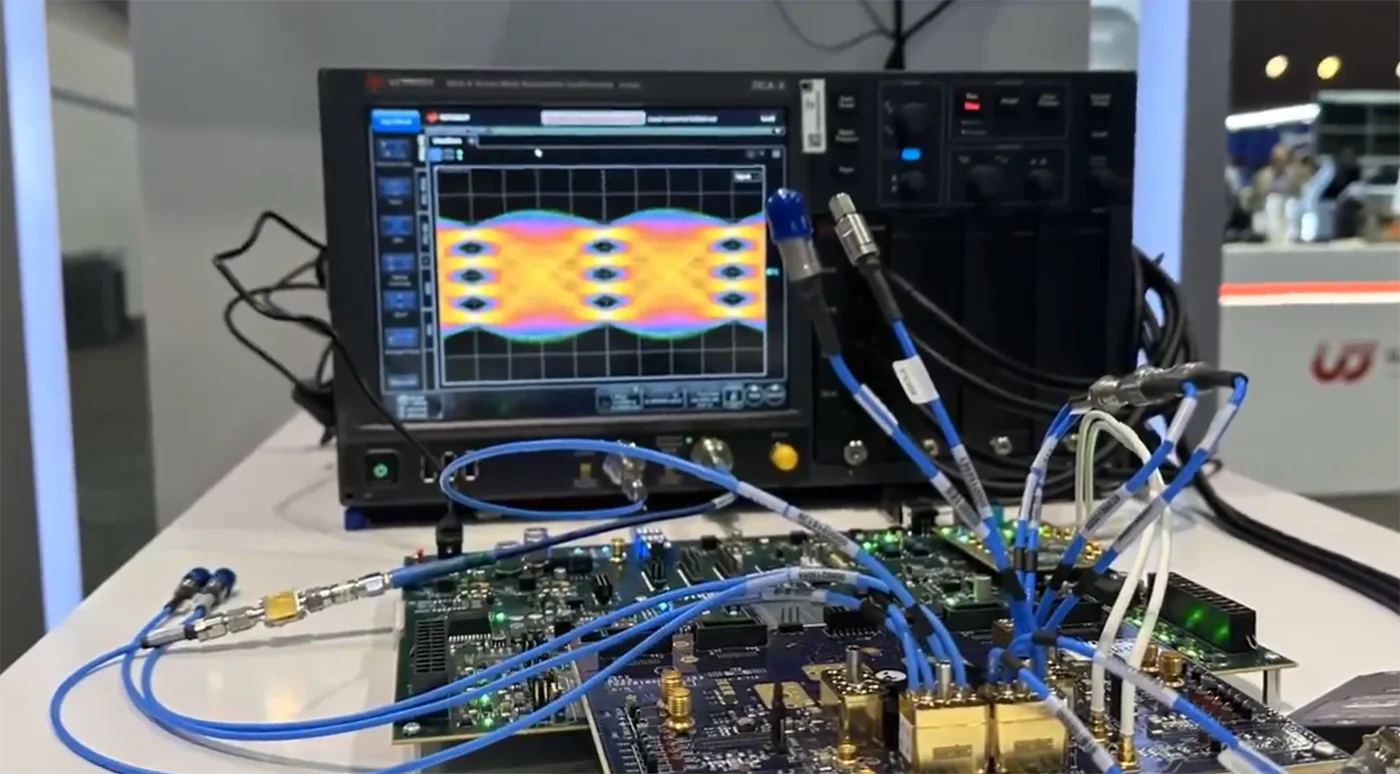

- تحليل الرسم البياني للعين: تصور سلامة الإشارة وجودتها بمعدلات 256 جيجا بايت/ثانية

- التحقق من أداء جهاز الاستقبال: التحقق من القدرة على اكتشاف الإشارات عالية السرعة ومعالجتها بشكل صحيح

- تدريب الروابط والمزامنة: ضمان اتصال مستقر بين الأجهزة

كيف تطور عرض النطاق الترددي PCIe

يوضح تطور عرض النطاق الترددي PCIe على مر السنين مدى سرعة زيادة قدرات نقل البيانات.

| توليد PCIe | سنة التقديم | عرض النطاق الترددي x16 (ثنائي الاتجاه) |

|---|---|---|

| PCIe 3.0 | 2010 | 32 جيجابايت/ثانية |

| PCIe 4.0 | 2017 | 64 جيجابايت/ثانية |

| PCIe 5.0 | 2019 | 128 جيجابايت/ثانية |

| PCIe 6.0 | 2022 | 256 جيجابايت/ثانية |

| PCIe 7.0 | 2025 | 512 جيجابايت/ثانية |

| PCIe 8.0 | متوقع ~ 2028 | ~حوالي 1 تيرابايت/ثانية |

إذا استمرت خارطة الطريق الحالية، فإن يمكن أن تنقل فتحة PCIe 8.0 x16 نظرياً حوالي تيرابايت واحد من البيانات في الثانية في كلا الاتجاهين معاً. ويمثل ذلك قفزة كبيرة مقارنة بالأجيال السابقة.

التقنية التي تقف وراء PCIe 8.0

يتطلب الوصول إلى مثل هذه السرعات القصوى ابتكارات كبيرة في نقل الإشارات وإدارة الأخطاء. إحدى أهم التقنيات المستخدمة هي PAM4 (تعديل سعة النبض بأربعة مستويات). على عكس أجيال PCIe السابقة التي كانت تستخدم إشارات ثنائية بسيطة، تسمح PAM4 لكل دورة إشارة بحمل المزيد من المعلومات باستخدام مستويات جهد متعددة.

في حين أن هذا النهج يزيد من عرض النطاق الترددي بشكل كبير، إلا أنه يقدم أيضًا معدلات خطأ أعلى. وللحفاظ على الموثوقية، تستخدم الأجيال الأحدث من PCIe تصحيح الخطأ الأمامي (FEC)التي تكتشف الأخطاء وتصححها أثناء الإرسال. قدم PCIe 6.0 هذه التقنيات، وسيعمل PCIe 8.0 على توسيع نطاقها لدعم سرعات أعلى.

مفهوم آخر مهم آخر هو نقل البيانات المستند إلى البث المتقطعحيث يتم إرسال المعلومات في وحدات بيانات ذات حجم ثابت. تعمل هذه الطريقة على تحسين الكفاءة وتبسيط تصحيح الأخطاء في وصلات الاتصال السريعة للغاية.

تتيح هذه التقنيات مجتمعةً إمكانية نقل البيانات بسرعات لم يكن من الممكن تحقيقها باستخدام طرق الإشارات التقليدية.

لماذا تحتاج الصناعة إلى PCIe أسرع من ذي قبل

إن الدفع نحو PCIe 8.0 مدفوع إلى حد كبير بالنمو السريع ل حوسبة الذكاء الاصطناعي وأعباء عمل مركز البيانات. غالبًا ما تحتوي خوادم الذكاء الاصطناعي الحديثة على وحدات معالجة رسومات متعددة أو مسرعات متخصصة يجب أن تتبادل كميات هائلة من البيانات أثناء مهام التدريب والاستدلال. تعتمد هذه الأنظمة بشكل كبير على الاتصالات الداخلية ذات النطاق الترددي العالي.

مع نمو النماذج بشكل أكبر وتوسع مجموعات البيانات، يستمر الطلب على الاتصال الأسرع بين المكونات في الارتفاع. تواجه الحوسبة عالية الأداء (HPC) والبنية التحتية السحابية وأنظمة التخزين واسعة النطاق تحديات مماثلة.

في هذه البيئات، تتيح توصيلات PCIe الأسرع:

وحدات معالجة الرسومات للتواصل بكفاءة أكبر مع وحدات المعالجة المركزية

مسرعات الذكاء الاصطناعي لمشاركة بيانات التدريب بشكل أسرع

مصفوفات التخزين NVMe لتوفير إنتاجية أعلى

أجهزة الشبكات لنقل البيانات بوقت استجابة أقل

وبدون التحسينات المستمرة في عرض النطاق الترددي للوصلات البينية، فإن أداء أنظمة الحوسبة المستقبلية سيكون محدوداً في نهاية المطاف بسبب اختناقات الاتصالات بدلاً من قوة المعالجة.

موعد توفر PCIe 8.0 PCIe 8.0

على الرغم من العرض التوضيحي الأخير، لا يزال معيار PCIe 8.0 في مرحلة التطوير المبكرة. يتم تعريف المعيار من قبل PCI-SIGومن المتوقع أن تكون المواصفات النهائية حول 2028. تظهر الأجهزة التجارية عادةً بعد عدة سنوات من الانتهاء من وضع المواصفات الجديدة. وقد يبدو الجدول الزمني الواقعي لاعتمادها على النحو التالي:

| المرحلة | الإطار الزمني المقدر |

|---|---|

| تم الانتهاء من المواصفات | ~2028 |

| نماذج السيليكون الأولية المبكرة | 2028-2029 |

| اعتماد مركز البيانات | حوالي عام 2030 |

| الحواسيب الشخصية الاستهلاكية | أوائل ثلاثينيات القرن العشرين |

في الوقت الحالي، يعد PCIe 5.0 و PCIe 6.0 الجيلين الأكثر صلة بتطوير الأجهزة الحالية.

يمثل العرض التوضيحي العام الأول لتقنية PCIe 8.0 علامة فارقة مبكرة ولكنها مهمة لصناعة الحوسبة. وهو يؤكد أن الخطوة التالية في خارطة طريق PCIe قابلة للتحقيق من الناحية التقنية وأن النظام البيئي لمصممي الرقائق ومصنعي الموصلات وبائعي الأنظمة يستعدون بالفعل لذلك. في حين أن المستخدمين العاديين لن يروا أجهزة PCIe 8.0 لعدة سنوات، فإن التكنولوجيا التي يتم اختبارها اليوم ستدعم في نهاية المطاف البنية التحتية للبيانات التي ستدعم خدمات الذكاء الاصطناعي المستقبلية والمنصات السحابية وأنظمة الحوسبة عالية الأداء.