DDR5メモリがコンシューマー市場への初期浸透を終え、サーバー分野での採用が着実に増え続ける中、DDR6に関する議論が業界内外で静かに熱を帯び始めている。これは技術分野における「時期尚早の誇大宣伝」ではなく、市場の需要と技術進化の必然的な結果である。現在、ジェネレーティブ人工知能、ハイパフォーマンス・コンピューティング、クラウド・コンピューティングなどの分野が爆発的な成長を遂げており、メモリの帯域幅、容量、エネルギー効率にかつてないほど厳しい要件が課せられている。TrendForce社の予測によると、2024年から2026年にかけて、AIおよびサーバー関連アプリケーションがDRAM総容量需要のそれぞれ46%、56%、66%を占め、この数字は2027年には70%を超えると予想されています。現在最も高性能なDDR5メモリでさえ、AIトレーニングや大規模データ処理シナリオの膨大なデータスループット要件を満たすには徐々に不十分になってきている。

同時に、コンシューマー市場では、ハイエンドのゲーミング・ノートPCやモバイル・ワークステーションがより高いメモリ周波数と大容量を追求し続ける一方で、薄型軽量デバイスはメモリの消費電力と物理的スペースに厳しい制限を課している。これらすべての要因が、新世代のメモリ規格の開発を加速させている。サムスン、SKハイニックス、マイクロンといった世界の主要メモリメーカーは、すでにDDR6仕様の初期プロトタイプ開発を完了し、インテル、AMD、NVIDIAなどのチップベンダーと協力してプラットフォームの検証を進めています。

DDRメモリの進化

DDRメモリとは何か、なぜ「帯域幅」が重要なのか

DDRメモリとは、Double Data Rate Synchronous Dynamic Random Access Memoryの略で、データを一時的に保存するコンピュータシステムの中核部品である。また、CPUとハードディスク・ドライブなどのストレージ・デバイス間のデータ転送ブリッジの役割も果たす。その基本的な動作原理は、各クロック・サイクルの立ち上がりエッジと立ち下がりエッジの両方でデータ転送を可能にする同期クロック信号に基づいている。その結果、同じクロック周波数でデータ転送効率は2倍になり、これが「ダブル・データ・レート」という言葉の由来となっている。

DDRメモリの性能指標の中で、帯域幅が最も重要であることは間違いない。メモリ帯域幅とは、メモリが単位時間当たりに転送できるデータ量のことである。帯域幅 = メモリ周波数 × バス幅 × チャネル数 ÷ 8 という式で計算されます。帯域幅は、CPUがデータにアクセスできる速度を直接決定する。これはデータ転送の「高速道路」に例えることができ、高速道路が広ければ広いほど、データ転送効率は高くなる。大規模なAAAゲームの実行、ビデオ編集やレンダリングの実行、AIモデルのトレーニングなど、複雑なアプリケーションシナリオでは、CPUは大量のデータを高速で継続的に読み書きする必要がある。メモリ帯域幅が不十分な場合、「データの混雑」が発生し、CPUは長時間データを待つことになる。このような場合、非常に強力なCPUでも性能を十分に発揮できず、システム性能のボトルネックとなる。そのため、メモリ帯域幅の改善は、各世代のDDRメモリ技術の進化において、常に中心的な目標の1つでした。

DDR1からDDR5へ:各世代が解決した問題とは?

DDR1 から DDR5 に至るまで、各世代のメモリは当時業界が直面していた重要な課題に直接対処するよう設計され、技術革新によって大幅な性能向上を達成しました。DDRメモリの第一世代であるDDR1は、2000年頃に登場しました。その中心的なブレークスルーはダブルデータレート転送の実装であり、従来のSDRAMに取って代わり、初期のコンピュータシステムにおける不十分なメモリ転送速度の問題を最初に解決した。Pentium 4のような初期のプロセッサに対応する互換メモリを提供し、データ転送速度は200~400MT/sだった。

DDR2 メモリは 2004 年頃に導入され、主に DDR1 の最大速度の低さや比較的高い消費電力などの制限に対処した。メモリチップの製造プロセスと信号処理技術を改善することで、DDR2はデータ転送速度を533~800MT/秒に向上させる一方、動作電圧をDDR1の2.5Vから1.8Vに引き下げました。これにより消費電力と発熱が大幅に低下し、当時のマルチコア・プロセッサの開発に適していました。

2007年に登場したDDR3メモリは、速度の限界をさらに打ち破り、最大データレートを1600 MT/秒に引き上げ、動作電圧を1.5 Vに下げることで、エネルギー効率を大幅に改善した。さらに重要なことに、DDR3はメモリ・コントローラの設計を最適化することで、メモリの安定性と互換性を向上させた。ノートパソコン、デスクトップパソコン、サーバーに広く採用され、最も長持ちするメモリ規格のひとつとなりました。

2014年に発売されたDDR4メモリは、ビッグデータ時代のメモリ容量と帯域幅に対する二重の要求を満たすために設計された。データ転送速度が2133~3200MT/秒に向上し、動作電圧が1.2Vに低下した一方で、1モジュールあたりの最大容量が128GBと、はるかに大きなシングルモジュール容量もサポートしました。バンク・グループ技術の導入により、DDR4は同時メモリ・アクセス能力を向上させ、マルチタスク・シナリオにおける帯域幅の圧力を効果的に軽減し、過去10年間にわたりコンピュータ・システムの主流メモリ構成となりました。

2021年末に正式に製品化されたDDR5メモリは、早期のAIと高性能コンピューティングの要件を満たすため、速度とエネルギー効率で再び大きな飛躍を達成した。最大データ・レートは8000MT/sに達し、動作電圧は1.1Vにさらに低下し、並列処理能力を高めるために2×32ビットのチャネル構造を採用している。DDR5はまた、コンシューマー向けメモリで初めてオンダイECCエラー訂正を導入し、データ伝送の安定性を向上させ、単一モジュールの容量は最大256GBに達しました。しかし、AIアプリケーションの爆発的な成長が続く中、DDR5の性能限界が徐々に明らかになりつつあり、DDR6開発の基礎が築かれつつある。

DDR6とは

DDR6は、JEDEC(Joint Electron Device Engineering Council)が主導する次世代ダブルデータレート同期ダイナミック・ランダム・アクセス・メモリ規格です。DDR6は、人工知能、ハイパフォーマンス・コンピューティング、クラウド・コンピューティングといった新たな分野が推進する、メモリ帯域幅、容量、エネルギー効率に対する極端な要求に対応するよう設計されている。DDR6の標準化プロセスは2024年に正式に開始され、DDR5の物理的性能限界を突破し、高帯域幅、大容量、高エネルギー効率、高信頼性を提供するメモリ・プラットフォームを構築することを主な目的としています。

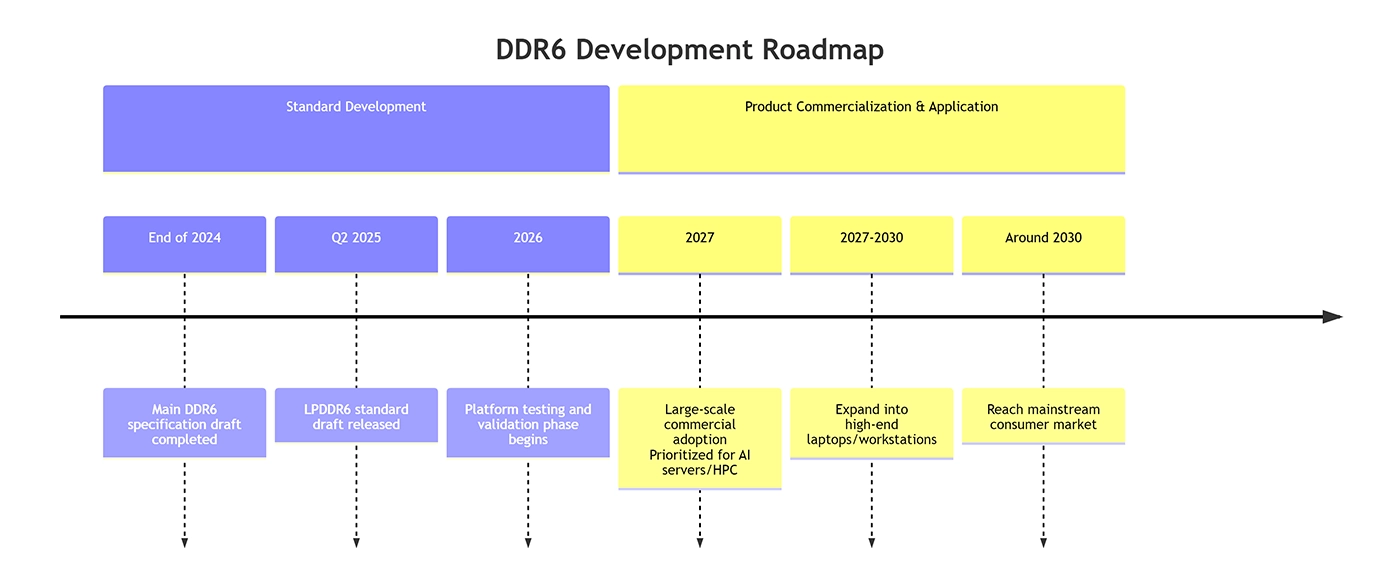

2024年末までに、JEDECはDDR6の主要な仕様草案を完成させ、その後の技術開発と製品実装の基礎を築いた。同時に、低消費電力版である LPDDR6 のドラフト仕様も 2025 年第 2 四半期に発表された。これまでのメモリ規格開発プロセスと同様、DDR6 の策定には、世界の主要メモリメーカー、チップ設計者、エンドデバイスベンダーが結集しました。これにより、業界エコシステム全体で協調した開発を推進しながら、規格がさまざまなアプリケーションシナリオやハードウェアプラットフォームをサポートできるようになります。

DDR6が解決しようとする3つの核心問題

DDR6の開発は、業界が現在直面している3つの中核的課題への対応に重点を置いている: 不十分な帯域幅、低いエネルギー効率、アーキテクチャ上の制限.

最初の問題は帯域幅の不足である。 AIトレーニングや大規模データ処理からの需要が急速に高まる中、現在のDDR5の最大速度である8000MT/秒では、大量のデータの高速伝送の要件を満たすことがますます難しくなっており、システム全体のパフォーマンスを制限する重要なボトルネックとなっています。DDR6は、チャネルアーキテクチャと伝送技術を改善し、初期データレートを8800MT/秒に引き上げ、後期には17600MT/秒まで引き上げる計画で、高負荷シナリオにおける帯域幅のボトルネックを根本的に解消することを目指しています。

つ目の問題はエネルギー効率だ。 AIサーバーやデータセンター環境では、メモリーモジュールの高密度実装が進み、消費電力と発熱が大幅に増加している。これにより、運用コストが上昇するだけでなく、冷却システムへの要求も高まります。動作電圧を下げ、電力管理メカニズムを最適化することで、DDR6は消費電力を下げながら性能を向上させます。一般的な消費電力は DDR5 と比較して 15-20% 低減すると予想され、DDR6 は高密度展開シナリオにより適しています。

3つ目の問題は、アーキテクチャー上の制限である。 DDR5 が採用している 2×32 ビットのチャネル構造は、高周波数ではシグナルインテグリティの問題が発生しやすい。さらに、従来の DIMM および SO-DIMM フォーム・ファクターは、2DPC 構成では大きなスペース要件と周波数の制限に悩まされます。DDR6 は、革新的な 4 × 24 ビットサブチャネルアーキテクチャを導入し、CAMM2 インターフェース規格を採用しています。これは、並列処理能力を向上させるだけでなく、従来のメモリ・パッケージのスペースと周波数の制約に対処し、高性能および高密度メモリ展開のアーキテクチャ・サポートを提供します。

DDR6の主な技術的変更点

データ転送速度の大きな飛躍

データ転送速度の大幅な向上は、DDR6の最も重要な技術的ブレークスルーの1つである。現在の業界ロードマップによると、DDR6 の初期データ転送速度は 8800 MT/s で開始され、現在の DDR5 の最大値である 8000 MT/s をすでに上回っている。製品ライフサイクル全体を通じて、DDR6の速度はさらに向上し、17600MT/秒になると予想され、一部のオーバークロック版では21000MT/秒を超える可能性もある。全体的な性能はDDR5の約2~3倍になると予想される。

このような大幅なスピードアップは、単にクロック周波数を上げることで達成されるものではない。むしろ、複数の技術が複合的に作用した結果である。一方では、DDR6 はメモリ・チップの製造プロセスを最適化し、電気的性能を向上させ、高周波数動作のためのハードウェア基盤を提供します。一方、DDR6 は、改良されたパッケージング技術、より微細な配線ルール、より厳格なタイミング制御など、より高度なシグナルインテグリティ最適化設計を導入しています。これらの対策により、高周波での信号干渉や減衰が効果的に低減されます。さらに DDR6 では、DDR5 で使用されていた 8n プリフェッチと比較して、16n プリフェッチ・メカニズムが採用されています。これにより、データ転送効率がさらに向上し、同じクロック周波数でより多くのデータを転送できるようになり、全体的な転送速度が大幅に飛躍しました。

サブチャンネル・アーキテクチャの変更

DDR6 は、DDR5 で使用されていた 2 × 32 ビットのチャネル設計に代わり、4 × 24 ビットのサブチャネル構造を採用することで、チャネル・アーキテクチャに破壊的な革新を導入しています。このアーキテクチャ変更の中心的な目標は、高い動作周波数でシグナル・インテグリティを維持しながら帯域幅を向上させることです。従来のワイド・バス設計では、周波数が一定以上高くなると信号のクロストークに悩まされ、伝送の安定性が低下する傾向がありました。チャネル数を増やし、各チャネルのビット幅を縮小することで、DDR6ではバスの総幅をDDR5の64ビットから96ビットに拡大しました。このアプローチは、並列処理能力を高めると同時に、各チャネルでの信号伝送圧力を低減します。

4×24ビットのサブチャネル・アーキテクチャは、より効率的な並列データ転送を可能にし、各サブチャネルが独立して読み出しと書き込みを実行できる。これにより、メモリの同時実行性と帯域幅の利用率が大幅に向上します。AIのトレーニングや大規模なデータ処理など、複数のデータストリームを同時に処理する必要があるシナリオでは、このアーキテクチャの利点が特に明らかになります。同時に、サブチャネル・アーキテクチャは、容量拡張とエネルギー効率の最適化に対してより大きな柔軟性を提供します。アプリケーションの要件に応じて各サブチャネルの動作状態を動的に調整できるため、性能と消費電力のバランスがより良くなります。

モジュールとインターフェースのフォームファクタの変更(CAMM2)

DDR6 は CAMM2 インターフェース規格を完全に採用し、長年使用されてきた従来の DIMM および SO-DIMM インターフェースに取って代わる。これは、メモリ・モジュールのフォーム・ファクターにおける大きな変革を意味する。CAMM2はCompression Attached Memory Moduleの略。当初はデルが導入し、後にJEDECが改訂、2023年末に正式にJEDEC標準となった。CAMM2は、底面のエッジコネクタを介してスロットに接続する従来のメモリモジュールとは異なり、マザーボード上の薄いアダプタボードを介して接続し、ネジで固定する圧縮コネクタを使用する。この新しいインターフェース形式は、いくつかの大きな利点をもたらします:

CAMM2は、従来の2DPC構成に見られる周波数の制限を効果的に解決します。従来の2DPC設計では、各チャンネルに2つのメモリモジュールを搭載することで、電気的な複雑さが増し、メモリ周波数が制限されます。CAMM2は、複雑なトポロジーをモジュール自体に移動させ、複雑さを内部で処理し、システムが最大性能と最大容量の両方を同時に達成できるようにします。

CAMM2は、Z軸方向の高さを大幅に削減し、マザーボード全体のスペース使用量を削減します。SO-DIMMと比較して、CAMM2は厚さを57%削減し、薄型軽量ノートパソコンやタブレットコンピュータなど、厚さ要件が厳しいデバイスに適しています。

CAMM2コネクターはLGAピン設計を採用しており、マザーボードとメモリーモジュールの両方にコンタクトパッドがあります。これにより、インターフェイスが損傷するリスクが低減され、コネクタ自体も独立して交換できるため、メンテナンスがより便利になります。

エネルギー効率と電力管理のさらなる進化

エネルギー効率の最適化という点では、DDR6 は DDR5 の低消費電力の利点を基礎とし、さらなるブレークスルーを達成しています。DDR5の標準動作電圧は1.1Vですが、DDR6は動作電圧を1.0Vまたはそれ以下に下げます。電圧の低下は消費電力の削減に直結し、一般的な DDR6 の消費電力は DDR5 より 15~20% 低くなると予想されます。この改善は、システムのエネルギー効率を向上させながら、全体的なエネルギー消費と冷却コストを削減できるため、データセンターやAIサーバーなどの高密度展開シナリオにとって特に重要です。

動作電圧の低下に加え、DDR6 はより高度な電力管理メカニズムを導入しています。メモリ・コントローラの電力管理ロジックを最適化することで、DDR6 はシステムの負荷に応じてメモリ・モジュールの動作状態を動的に調整することができます。低負荷状態では、メモリの周波数と電圧が自動的に低下し、システムが低電力モードに入ることができます。高負荷条件下では、性能が急速に向上し、データ転送要件が満たされるようになります。このダイナミック・パワー・マネージメント・アプローチにより、DDR6は、さまざまなアプリケーション・シナリオにおいて性能と消費電力の最適なバランスを実現し、エネルギーを効果的に節約しながら高い性能を発揮します。

容量拡大とスタッキングの可能性

DDR6は容量拡張の可能性が大きく、AIやハイパフォーマンス・コンピューティングのワークロードの大容量メモリ要件を満たすのに適しています。積層技術の革新は、DDR6 の容量拡張を可能にする重要な要素です。DDR6は、より高度な3Dスタッキング・パッケージング技術を採用し、より多くのメモリ・ダイを垂直方向に積層することで、チップあたりの容量密度を大幅に向上させます。同時に、CAMM2 インターフェイスのモジュール設計は、スタック・モジュール構成をサポートすることで容量拡張を容易にし、システム・メモリの総容量を増加させます。

例えば、2つのシングル・チャンネルDタイプCAMM2モジュールを理論的にはZ軸に沿って積み重ねることができ、システム・メモリの総容量は512GBに達する。技術が成熟すれば、さらに大容量のブレークスルーが達成されるかもしれない。現在計画されている DDR5 CAMM2 モジュールの最大容量は 256 GB です。より高密度のメモリチップとスタッキング技術により、DDR6 CAMM2モジュールはこの限界を超えると予想される。

DDR6とDDR5の包括的比較

| カテゴリー | DDR5 | DDR6 |

|---|---|---|

| データ・レート | 最大約8000MT/秒 | 初期8800MT/秒、17600MT/秒まで向上予定、オーバークロック版は21000MT/秒を超える可能性あり |

| チャンネル・アーキテクチャ | 2×32ビット(合計バス幅64ビット) | 4×24ビット(合計バス幅96ビット) |

| インターフェイス フォームファクター | 主にDIMM、SO-DIMM | CAMM2 / LPCAMM2を完全採用 |

| 動作電圧 | 1.1 V | 1.0V以下 |

| 標準的な消費電力 | ベースライン・レベル | DDR5より低い15-20% |

| モジュールあたりの最大容量 | 256GB(ディム)、128GB(ソディム) | 256GBを超えると予想され、デュアル・モジュールのスタッキングで512GBを達成する可能性もある。 |

| プリフェッチのメカニズム | 8nプリフェッチ | 16nプリフェッチ |

| 2DPC周波数制限 | 周波数の大幅な制限 | モジュール内で処理される複雑さ、明らかな周波数制限なし |

| 主なアプリケーション・シナリオ | ミドル~ハイエンドPC、サーバー、ワークステーション(移行期) | AIサーバー、ハイパフォーマンス・コンピューティング、ハイエンド・ワークステーション、フラッグシップPC |

DDR6の互換性

DDR6とDDR5の間には後方互換性がありません。つまり、DDR5用に設計されたマザーボードではDDR6メモリを直接使用できず、その逆も同様です。その主な理由は、アーキテクチャ、インターフェース・フォーム・ファクター、電気仕様の根本的な違いにあります。

まず、インターフェイスのフォームファクターに違いがある。DDR6はCAMM2インターフェイスを完全に採用しているが、DDR5は主に従来のDIMMとSO-DIMMインターフェイスを使用している。物理的な寸法や接続方法がまったく異なるため、互いに互換性がない。

第二に、電気的仕様に違いがある。DDR5の動作電圧が1.1Vであるのに対し、DDR6は1.0Vまたはそれ以下に低下する。さらに、両者の信号定義とタイミング・パラメータはまったく異なる。メモリ・コントローラは、回路を駆動し信号を正しく処理するために、特定の電気仕様を念頭に置いて設計する必要があります。DDR5メモリ・コントローラはDDR6の電気的要件を満たすことができず、無理に使用するとデバイスが損傷したり、正しく動作しなくなったりする。

最後に、チャネル・アーキテクチャにも違いがある。DDR6は4×24ビットのサブチャネル・アーキテクチャを採用しており、DDR5が採用している2×32ビット・アーキテクチャとは根本的に異なる。メモリ・コントローラの設計ロジックはそれぞれまったく異なるため、最終的に2つの規格には互換性がないことになる。そのため、DDR6 の展開には、CPU、マザーボード、および業界全体のエコシステムが協調してサポートし、完全なハードウェア・サポート・システムを形成する必要があります。現在、Samsung、SK hynix、Micronなどのメモリメーカーは、Intel、AMD、NVIDIAなどのチップベンダーと緊密に協力し、DDR6プラットフォームの検証を共同で進め、エコシステムの開発を加速させています。

DDR6のアプリケーション・シナリオ分析

データセンターとクラウド・コンピューティング

データセンターとクラウド・コンピューティングは、DDR6にとって最も重要なアプリケーション・シナリオのひとつです。現在、クラウド・コンピューティング・サービスは、大規模、高並行性、低レイテンシへと進化しています。データ・センターでは、膨大な数のユーザー・リクエストとデータ転送タスクを処理する必要があり、メモリ帯域幅と容量に対する要求が非常に高くなっています。DDR6は、データセンター・サーバーのメモリ帯域幅を大幅に拡大し、データ処理とデータ転送を高速化すると同時に、ユーザー・リクエストに対する応答待ち時間を短縮します。

同時に、DDR6 の高いエネルギー効率は、データセンターの要件にも適しています。データ・センターはサーバー密度が高く、メモリ・モジュールがシステム全体の消費電力のかなりの部分を占めています。DDR5と比較して、DDR6は消費電力を15-20%削減し、運用効率を向上させながら、データセンターの全体的なエネルギー使用量と冷却コストを効果的に削減することができます。さらに、DDR6は大容量拡張をサポートし、クラウド・コンピューティング環境における大規模なデータ・キャッシングや並列処理のニーズに応えます。これにより、クラウド・データベース、クラウド・ストレージ、クラウド・レンダリングなどのサービスに対するメモリ・サポートが強化されます。DDR6の商用化により、データセンターのコンピューティングとデータ処理能力は質的な飛躍を遂げることが期待されます。

AIと高性能コンピューティング(HPC)

AIとハイパフォーマンス・コンピューティングは、DDR6の開発と採用の中心的な原動力であり、DDR6が最大の利点を提供できるアプリケーション・シナリオでもあります。AIのトレーニング・シナリオでは、モデルのパラメータ・サイズが増大し続け、膨大な量のトレーニング・データを処理する必要があります。このため、メモリの帯域幅と容量に対する要求が非常に高くなります。DDR6の高帯域幅特性は、CPUとGPUがトレーニング・プロセス中にトレーニング・データを迅速に読み書きできることを保証し、データ転送のボトルネックを回避してトレーニング効率を大幅に改善します。

気象予報、天体物理学シミュレーション、製薬研究などのハイパフォーマンス・コンピューティングの分野では、システムは大量の複雑な計算やデータ処理を実行しなければならない。これらのワークロードでは、メモリに極めて高いレベルの並列処理能力と安定性が求められます。DDR6の4×24ビット・サブチャネル・アーキテクチャは並列データ処理を強化し、16nプリフェッチ・メカニズムと高度なエラー訂正メカニズムはデータ転送の効率性と安定性の両方を保証します。さらに、DDR6の低消費電力という利点は、ハイパフォーマンス・コンピューティング・クラスターのエネルギー消費を削減し、長期間にわたって継続的に動作する能力を向上させます。AIとハイパフォーマンス・コンピューティングが拡大を続ける中、DDR6はこれらの分野における中核的なメモリ構成となるでしょう。

コンシューマーPCとハイエンド・ワークステーション

DDR6はまずサーバーやAI関連分野で商業的に展開されるが、エコシステムが成熟しコストが低下するにつれて、コンシューマーPCやハイエンド・ワークステーション市場にも徐々に浸透していくと予想される。ハイエンドのゲーミング・ノートPCやフラッグシップ・デスクトップPCでは、DDR6の高周波数と広帯域幅により、ゲームのロード時間と全体的なスムーズさが向上します。これは、大規模なAAAゲームを実行する場合に特に顕著で、DDR6はスタッタリングやフレーム低下を効果的に低減することができます。同時に、CAMM2インターフェイスによって可能になる薄型設計は、メーカーが高性能を備えたより薄型で軽量なゲーミング・ノートPCを開発するのに役立ちます。

ハイエンドのワークステーションも、DDR6 を採用する最初のコンシューマー・セグメン トのひとつとなるでしょう。モバイルワークステーションやグラフィックスワークステーションは、主にビデオ編集、3D モデリング、アニメーションレンダリングなどのプロフェッショナルなワークロードに使用され、メモリの周波数、容量、安定性に対する要求が非常に高くなっています。従来のSO-DIMMメモリは、2DPC構成での周波数制限に苦しみ、ハイエンドワークステーションの性能要件を満たすことができませんでした。CAMM2インターフェイスと組み合わせたDDR6は、この問題に対処すると同時に、より大容量をサポートします。

標準化の進展と商業化のタイムライン

メモリ技術の標準化を主導する組織であるJEDECは、2024年末にDDR6の主要仕様のドラフトを完成させた。モバイル機器をターゲットとするLPDDR6の規格草案も2025年第2四半期に発表された。次の段階は、重要なプラットフォームのテストと検証の段階で、2026年に実施される見込みである。インテルやAMDなどのチップメーカーが参加し、DDR6と将来のプロセッサー・プラットフォーム間の互換性を確保する。

業界の予測によると、DDR6は2027年頃に大規模な商業展開に入ると予想されている。その採用経路は、ハイエンドからメインストリームへのパターンをたどると予想される。DDR6はまず、AIサーバー、高性能コンピューティング・システム、データセンターなど、性能に極めて敏感だがコストにはそれほど敏感でない分野で使用される。その後、ハイエンドのノートPCやワークステーション市場に徐々に拡大していくだろう。主流のデスクトップPCや一般的なラップトップユーザーがDDR6を広く目にするようになるのは、2030年頃になるかもしれない。

DDR6 は単純な反復ではなく、根本的な課題に対処するために設計されたアーキテクチャの進化です。その中心的な目標は、メモリ帯域幅とエネルギー効率における現在のボトルネックを打破し、人工知能、ハイパフォーマンス・コンピューティング、将来の大規模データ処理に不可欠なインフラを提供することです。DDR1 から DDR5 までの歩みは、メモリ技術がコンピューティングの需要に合わせて継続的に進化するという一貫したパターンを示しています。DDR6 は、この進歩における次の章を象徴しています。DDR6は、コンピューティングの境界を拡大するという使命を担っており、その最終形態と普及は、今後10年間の技術開発の軌跡に大きな影響を与えるでしょう。