Da der DDR5-Speicher gerade seine anfängliche Durchdringung auf dem Verbrauchermarkt abgeschlossen hat und seine Akzeptanz im Serverbereich stetig zunimmt, haben die Diskussionen über DDR6 sowohl innerhalb als auch außerhalb der Branche leise begonnen, sich zu erhitzen. Dabei handelt es sich nicht um einen "verfrühten Hype" im Technologiebereich, sondern um ein unvermeidliches Ergebnis der Marktnachfrage und der technologischen Entwicklung. Derzeit erleben Bereiche wie generative künstliche Intelligenz, High-Performance-Computing und Cloud Computing ein explosives Wachstum, das beispiellos hohe Anforderungen an Speicherbandbreite, -kapazität und -effizienz stellt. Laut Prognosen von TrendForce werden von 2024 bis 2026 46%, 56% bzw. 66% der gesamten DRAM-Kapazitätsnachfrage auf KI- und Serveranwendungen entfallen, und im Jahr 2027 wird diese Zahl voraussichtlich 70% übersteigen. Selbst der derzeit leistungsstärkste DDR5-Speicher reicht allmählich nicht mehr aus, um die massiven Datendurchsatzanforderungen von KI-Training und groß angelegten Datenverarbeitungsszenarien zu erfüllen.

Gleichzeitig streben auf dem Verbrauchermarkt High-End-Gaming-Laptops und mobile Workstations weiterhin nach höheren Speicherfrequenzen und größeren Kapazitäten, während dünne und leichte Geräte strenge Beschränkungen hinsichtlich des Stromverbrauchs und des Platzbedarfs auferlegen. All diese Faktoren beschleunigen die Entwicklung einer neuen Generation von Speicherstandards. Weltweit führende Speicherhersteller wie Samsung, SK hynix und Micron haben bereits erste Prototypen der DDR6-Spezifikationen entwickelt und arbeiten mit Chip-Anbietern wie Intel, AMD und NVIDIA zusammen, um die Plattformvalidierung voranzutreiben.

Wie sich DDR-Speicher entwickelt hat

Was ist DDR-Speicher und warum ist "Bandbreite" so wichtig?

DDR-Speicher, kurz für Double Data Rate Synchronous Dynamic Random Access Memory, ist die Kernkomponente in Computersystemen, die für die vorübergehende Speicherung von Daten zuständig ist. Er dient auch als Brücke für die Datenübertragung zwischen der CPU und Speichergeräten wie Festplatten. Sein Funktionsprinzip basiert auf einem synchronen Taktsignal, das die Datenübertragung sowohl bei der steigenden als auch bei der fallenden Flanke eines jeden Taktzyklus ermöglicht. Dadurch wird die Effizienz der Datenübertragung bei gleicher Taktfrequenz verdoppelt, daher auch der Begriff "doppelte Datenrate".

Von allen Leistungsmetriken des DDR-Speichers ist die Bandbreite zweifellos die wichtigste. Die Speicherbandbreite bezieht sich auf die Datenmenge, die der Speicher pro Zeiteinheit übertragen kann. Sie wird nach der folgenden Formel berechnet: Bandbreite = Speicherfrequenz × Busbreite × Anzahl der Kanäle ÷ 8. Die Bandbreite bestimmt direkt, wie schnell die CPU auf Daten zugreifen kann. Sie kann mit einer "Autobahn" für die Datenübertragung verglichen werden: je breiter die Autobahn, desto höher die Effizienz der Datenübertragung. In komplexen Anwendungsszenarien, z. B. beim Ausführen großer AAA-Spiele, beim Bearbeiten und Rendern von Videos oder beim Trainieren von KI-Modellen, muss die CPU kontinuierlich große Datenmengen mit hoher Geschwindigkeit lesen und schreiben. Wenn die Speicherbandbreite nicht ausreicht, kommt es zu einem "Datenstau", wodurch die CPU längere Zeit auf Daten warten muss. In solchen Fällen kann selbst eine sehr leistungsstarke CPU nicht die volle Leistung erbringen, was zu einem Engpass in der Systemleistung führt. Daher war die Verbesserung der Speicherbandbreite schon immer eines der Hauptziele bei der Entwicklung jeder Generation der DDR-Speichertechnologie.

Von DDR1 bis DDR5: Welche Probleme jede Generation löste

Von DDR1 bis DDR5 war jede Speichergeneration darauf ausgerichtet, die wichtigsten Herausforderungen der Branche zu bewältigen und durch technologische Innovationen erhebliche Leistungssteigerungen zu erzielen. DDR1, die erste Generation von DDR-Speicher, kam um das Jahr 2000 auf den Markt. Ihr zentraler Durchbruch war die Implementierung der doppelten Datenübertragungsrate, die den traditionellen SDRAM ersetzte und zunächst das Problem der unzureichenden Speicherübertragungsgeschwindigkeiten in frühen Computersystemen löste. Sie bot kompatible Speicherunterstützung für frühe Prozessoren wie den Pentium 4 mit Datenraten von 200 bis 400 MT/s.

DDR2-Speicher wurde um 2004 eingeführt und befasste sich in erster Linie mit den Einschränkungen von DDR1, einschließlich der niedrigen Höchstgeschwindigkeit und des relativ hohen Stromverbrauchs. Durch die Verbesserung der Herstellungsverfahren für Speicherchips und der Signalverarbeitungstechnologien erhöhte DDR2 die Datenübertragungsraten auf 533-800 MT/s und senkte gleichzeitig die Betriebsspannung von 2,5 V bei DDR1 auf 1,8 V. Dadurch wurden der Stromverbrauch und die Wärmeentwicklung erheblich gesenkt, so dass sich DDR2 besser für die damalige Entwicklung von Mehrkernprozessoren eignete.

DDR3-Speicher, der 2007 auf den Markt kam, durchbrach weitere Geschwindigkeitsbegrenzungen, erhöhte die maximale Datenrate auf 1600 MT/s und senkte die Betriebsspannung auf 1,5 V, was zu einer erheblichen Verbesserung der Energieeffizienz führte. Noch wichtiger ist, dass DDR3 die Speicherstabilität und Kompatibilität durch ein optimiertes Design des Speicher-Controllers verbesserte. Es unterstützte die breite Einführung in Laptops, Desktops und Servern und wurde zu einem der langlebigsten Speicherstandards.

Der 2014 eingeführte DDR4-Speicher wurde entwickelt, um die doppelten Anforderungen an Speicherkapazität und Bandbreite im Zeitalter von Big Data zu erfüllen. Die Datenübertragungsraten wurden auf 2133-3200 MT/s erhöht und die Betriebsspannung auf 1,2 V gesenkt, während gleichzeitig viel größere Einzelmodul-Kapazitäten mit bis zu 128 GB pro Modul unterstützt wurden. Durch die Einführung der Bank-Group-Technologie verbesserte DDR4 die Möglichkeiten des gleichzeitigen Speicherzugriffs und verringerte effektiv den Bandbreitendruck in Multitasking-Szenarien, wodurch es in den letzten zehn Jahren zur wichtigsten Speicherkonfiguration für Computersysteme wurde.

Der DDR5-Speicher, der Ende 2021 offiziell auf den Markt kommt, hat einen weiteren großen Sprung bei der Geschwindigkeit und Energieeffizienz gemacht, um die Anforderungen der frühen KI und des Hochleistungscomputers zu erfüllen. Die maximale Datenrate erreicht bis zu 8000 MT/s, die Betriebsspannung wurde weiter auf 1,1 V gesenkt, und es wird eine 2 × 32-Bit-Kanalstruktur verwendet, um die Parallelverarbeitungsfähigkeiten zu verbessern. Mit DDR5 wurde außerdem zum ersten Mal eine On-Die-ECC-Fehlerkorrektur für Consumer-Speicher eingeführt, die die Stabilität der Datenübertragung verbessert und die Kapazität eines einzelnen Moduls auf bis zu 256 GB erhöht. Da die Zahl der KI-Anwendungen jedoch weiterhin explosionsartig ansteigt, werden die Leistungsgrenzen von DDR5 allmählich deutlich, so dass die Entwicklung von DDR6 vorbereitet wird.

Was ist DDR6?

DDR6 ist der Double Data Rate Synchronous Dynamic Random Access Memory-Standard der nächsten Generation, der von JEDEC (Joint Electron Device Engineering Council) geleitet wird. Er wurde entwickelt, um den extremen Anforderungen an Speicherbandbreite, Kapazität und Energieeffizienz gerecht zu werden, die durch aufkommende Bereiche wie künstliche Intelligenz, Hochleistungscomputer und Cloud Computing entstehen. Der DDR6-Standardisierungsprozess begann offiziell im Jahr 2024 mit dem Hauptziel, die physikalischen Leistungsgrenzen von DDR5 zu durchbrechen und eine Speicherplattform zu schaffen, die hohe Bandbreite, große Kapazität, hohe Energieeffizienz und hohe Zuverlässigkeit bietet.

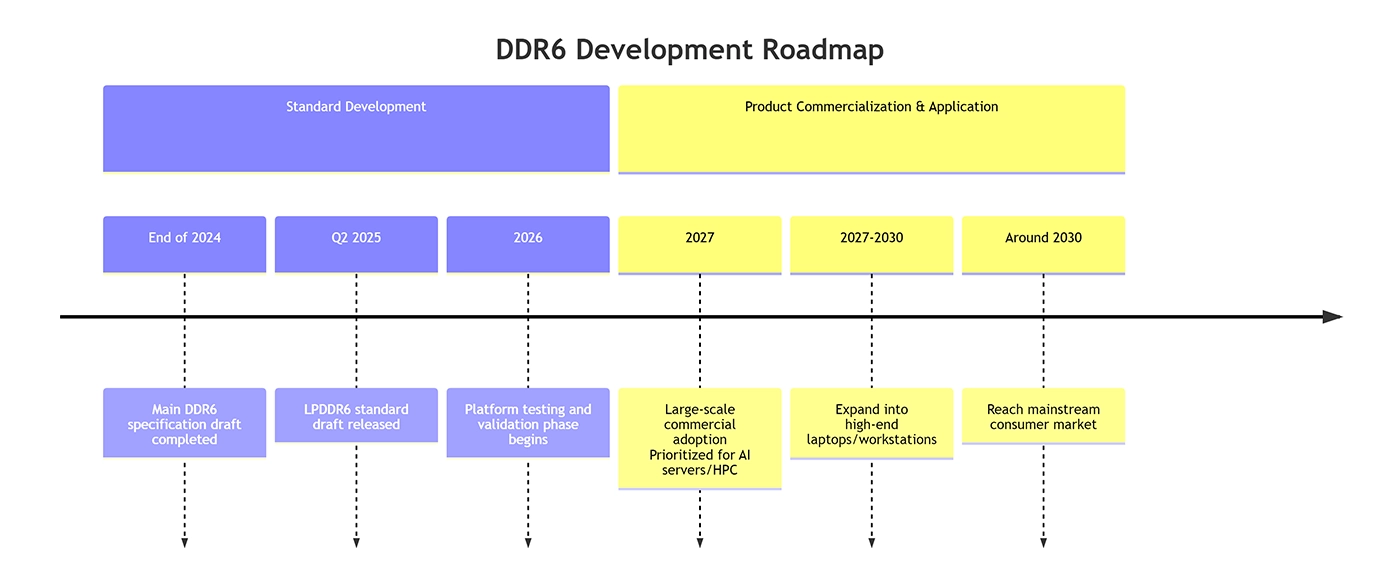

Ende 2024 hat die JEDEC den Hauptentwurf der DDR6-Spezifikation fertiggestellt und damit die Grundlage für die nachfolgende Technologieentwicklung und Produktimplementierung gelegt. Gleichzeitig wurde im zweiten Quartal 2025 der Entwurf der Spezifikation für die Low-Power-Version, LPDDR6, veröffentlicht. Ähnlich wie bei früheren Prozessen zur Entwicklung von Speicherstandards kommen bei der Formulierung von DDR6 die wichtigsten globalen Speicherhersteller, Chipdesigner und Anbieter von Endgeräten zusammen. Dadurch wird sichergestellt, dass der Standard verschiedene Anwendungsszenarien und Hardware-Plattformen unterstützen kann, und gleichzeitig eine koordinierte Entwicklung im gesamten Ökosystem der Branche gefördert.

Die drei Kernprobleme, die DDR6 zu lösen versucht

Die Entwicklung von DDR6 konzentriert sich auf die Bewältigung von drei zentralen Herausforderungen, denen sich die Branche derzeit gegenübersieht: unzureichende Bandbreite, geringe Energieeffizienz und architektonische Einschränkungen.

Das erste Problem ist die unzureichende Bandbreite. Angesichts der schnell wachsenden Nachfrage nach KI-Training und umfangreicher Datenverarbeitung kann die derzeitige Höchstgeschwindigkeit von DDR5 von 8000 MT/s die Anforderungen an die Hochgeschwindigkeitsübertragung großer Datenmengen zunehmend nicht mehr erfüllen und wird zu einem zentralen Engpass, der die Gesamtsystemleistung einschränkt. DDR6 verbessert die Kanalarchitektur und die Übertragungstechnologien, um die anfängliche Datenrate auf 8800 MT/s zu erhöhen. In späteren Phasen ist eine Steigerung auf 17.600 MT/s geplant, um Bandbreitenengpässe in Hochlastszenarien grundlegend zu beseitigen.

Das zweite Thema ist die Energieeffizienz. In KI-Servern und Rechenzentrumsumgebungen werden Speichermodule in immer höherer Dichte eingesetzt, was den Stromverbrauch und die Wärmeentwicklung deutlich erhöht. Dies führt nicht nur zu höheren Betriebskosten, sondern stellt auch höhere Anforderungen an die Kühlsysteme. Durch die Senkung der Betriebsspannung und die Optimierung der Energieverwaltungsmechanismen verbessert DDR6 die Leistung und senkt gleichzeitig den Stromverbrauch. Es wird erwartet, dass der typische Stromverbrauch im Vergleich zu DDR5 um 15-20% gesenkt werden kann, wodurch sich DDR6 besser für Einsatzszenarien mit hoher Speicherdichte eignet.

Der dritte Punkt sind die architektonischen Einschränkungen. Die von DDR5 verwendete 2 × 32-Bit-Kanalstruktur ist anfällig für Signalintegritätsprobleme bei hohen Frequenzen. Darüber hinaus leiden die traditionellen DIMM- und SO-DIMM-Formfaktoren unter großem Platzbedarf und Frequenzbeschränkungen bei 2DPC-Konfigurationen. DDR6 führt eine innovative 4 × 24-Bit-Sub-Channel-Architektur ein und übernimmt den CAMM2-Schnittstellenstandard. Dadurch wird nicht nur die Parallelverarbeitungsfähigkeit verbessert, sondern es werden auch die Platz- und Frequenzbeschränkungen herkömmlicher Speicherpakete beseitigt, was eine architektonische Unterstützung für den Einsatz von Hochleistungsspeichern mit hoher Dichte bietet.

Wichtige technische Änderungen bei DDR6

Ein großer Sprung in der Datenübertragungsgeschwindigkeit

Eine erhebliche Steigerung der Datenübertragungsgeschwindigkeit ist einer der wichtigsten technologischen Durchbrüche von DDR6. Nach den aktuellen Plänen der Industrie wird DDR6 mit einer anfänglichen Datenrate von 8800 MT/s starten und damit bereits den derzeitigen Höchstwert von DDR5 mit 8000 MT/s übertreffen. Es wird erwartet, dass die DDR6-Geschwindigkeiten während des gesamten Produktlebenszyklus weiter auf 17.600 MT/s steigen werden, wobei einige übertaktete Versionen möglicherweise 21.000 MT/s überschreiten werden. Es wird erwartet, dass die Gesamtleistung etwa zwei- bis dreimal so hoch sein wird wie bei DDR5.

Eine solch erhebliche Geschwindigkeitssteigerung wird nicht einfach durch eine Erhöhung der Taktfrequenz erreicht. Vielmehr ist sie das Ergebnis der kombinierten Wirkung mehrerer Technologien. Einerseits optimiert DDR6 die Herstellungsprozesse von Speicherchips, verbessert die elektrische Leistung und schafft eine Hardwaregrundlage für den Hochfrequenzbetrieb. Andererseits führt DDR6 fortschrittlichere Designs zur Optimierung der Signalintegrität ein, einschließlich verbesserter Verpackungstechnologien, feinerer Routing-Regeln und strengerer Timing-Kontrolle. Durch diese Maßnahmen werden Signalstörungen und -abschwächungen bei hohen Frequenzen wirksam reduziert. Darüber hinaus verwendet DDR6 einen 16n-Prefetch-Mechanismus im Vergleich zu dem in DDR5 verwendeten 8n-Prefetch. Dadurch wird die Datenübertragungseffizienz weiter verbessert, so dass mehr Daten mit der gleichen Taktfrequenz übertragen werden können, was zu einem erheblichen Anstieg der Gesamtübertragungsgeschwindigkeit führt.

Änderungen in der Sub-Channel-Architektur

DDR6 führt eine bahnbrechende Innovation in der Kanalarchitektur ein, indem es eine 4 × 24-Bit-Subkanalstruktur einführt, die das 2 × 32-Bit-Kanaldesign von DDR5 ersetzt. Das Hauptziel dieser architektonischen Änderung ist die Verbesserung der Bandbreite bei gleichzeitiger Wahrung der Signalintegrität bei hohen Betriebsfrequenzen. Herkömmliche Wide-Bus-Designs neigen zu Signalübersprechen, wenn die Frequenzen über einen bestimmten Punkt hinaus steigen, was zu einer geringeren Übertragungsstabilität führt. Durch die Erhöhung der Anzahl der Kanäle und die Verringerung der Bitbreite jedes Kanals vergrößert DDR6 die Gesamtbusbreite von 64 Bit in DDR5 auf 96 Bit. Dieser Ansatz verbessert die Fähigkeit zur Parallelverarbeitung und verringert gleichzeitig den Druck auf die Signalübertragung in jedem einzelnen Kanal.

Die 4 × 24-Bit-Subkanal-Architektur ermöglicht eine effizientere parallele Datenübertragung, so dass jeder Subkanal unabhängig voneinander Lese- und Schreibvorgänge durchführen kann. Dies verbessert die Gleichzeitigkeit der Speicher und die Bandbreitennutzung erheblich. In Szenarien wie dem KI-Training und der Verarbeitung großer Datenmengen, bei denen mehrere Datenströme gleichzeitig verarbeitet werden müssen, werden die Vorteile dieser Architektur besonders deutlich. Gleichzeitig bietet die Sub-Channel-Architektur eine größere Flexibilität bei der Kapazitätserweiterung und der Optimierung der Energieeffizienz. Sie ermöglicht es, den Betriebszustand jedes Unterkanals dynamisch an die Anforderungen der Anwendung anzupassen und so ein besseres Gleichgewicht zwischen Leistung und Stromverbrauch zu erreichen.

Änderungen der Modul- und Schnittstellenformfaktoren (CAMM2)

DDR6 wird den CAMM2-Schnittstellenstandard vollständig übernehmen und die traditionellen DIMM- und SO-DIMM-Schnittstellen, die seit vielen Jahren verwendet wurden, ersetzen. Dies stellt einen bedeutenden Wandel bei den Formfaktoren für Speichermodule dar. CAMM2 steht für Compression Attached Memory Module. Es wurde ursprünglich von Dell eingeführt, später von JEDEC überarbeitet und Ende 2023 offiziell zum JEDEC-Standard erklärt. Im Gegensatz zu herkömmlichen Speichermodulen, die über Randstecker an der Unterseite mit den Steckplätzen verbunden werden, verwendet CAMM2 einen Kompressionsstecker, der über eine dünne Adapterplatte auf der Hauptplatine angeschlossen und mit Schrauben befestigt wird. Diese neue Schnittstellenform bringt mehrere bedeutende Vorteile mit sich:

CAMM2 löst die Frequenzbeschränkungen, die bei herkömmlichen 2DPC-Konfigurationen auftreten, wirksam auf. Bei herkömmlichen 2DPC-Designs erhöht die Installation von zwei Speichermodulen pro Kanal die elektrische Komplexität und begrenzt die Speicherfrequenz. Mit CAMM2 wird die komplexe Topologie in das Modul selbst verlagert, wodurch die Komplexität intern gehandhabt wird und ein System gleichzeitig maximale Leistung und maximale Kapazität erreichen kann.

CAMM2 reduziert die Höhe der Z-Achse und den Platzbedarf auf dem Motherboard erheblich. Im Vergleich zu SO-DIMM reduziert CAMM2 die Dicke um 57% und eignet sich daher besser für Geräte mit strengen Anforderungen an die Dicke, wie z. B. dünne und leichte Laptops und Tablet-Computer.

Der CAMM2-Anschluss verwendet ein LGA-Pin-Design mit Kontaktflächen sowohl auf der Hauptplatine als auch auf dem Speichermodul. Dadurch wird das Risiko einer Beschädigung der Schnittstelle verringert, und der Steckverbinder selbst kann unabhängig ausgetauscht werden, was die Wartung erleichtert.

Weiterentwicklung von Energieeffizienz und Energiemanagement

In Bezug auf die Optimierung der Energieeffizienz baut DDR6 auf den stromsparenden Vorteilen von DDR5 auf und erzielt weitere Durchbrüche. Die Standardbetriebsspannung von DDR5 liegt bei 1,1 V, während DDR6 die Betriebsspannung auf 1,0 V oder sogar noch niedriger senken wird. Eine niedrigere Spannung führt direkt zu einem geringeren Stromverbrauch, wobei der typische DDR6-Stromverbrauch voraussichtlich 15-20% niedriger sein wird als bei DDR5. Diese Verbesserung ist besonders wichtig für Einsatzszenarien mit hoher Speicherdichte, wie z. B. Rechenzentren und KI-Server, da sie dazu beiträgt, den Gesamtenergieverbrauch und die Kühlungskosten zu senken und gleichzeitig die Energieeffizienz des Systems zu verbessern.

Zusätzlich zur Senkung der Betriebsspannung führt DDR6 fortschrittlichere Energieverwaltungsmechanismen ein. Durch die Optimierung der Energieverwaltungslogik des Speichercontrollers kann DDR6 den Betriebszustand der Speichermodule dynamisch an die Systemlast anpassen. Bei geringer Last werden die Speicherfrequenz und -spannung automatisch reduziert, so dass das System in den Energiesparmodus übergehen kann. Bei hoher Auslastung wird die Leistung schnell erhöht, um die Anforderungen an die Datenübertragung zu erfüllen. Dank dieses dynamischen Energieverwaltungsansatzes kann DDR6 in verschiedenen Anwendungsszenarien ein optimales Gleichgewicht zwischen Leistung und Stromverbrauch herstellen und so hohe Leistung bei gleichzeitiger Energieeinsparung bieten.

Kapazitätserweiterung und Stapelungspotenzial

DDR6 bietet ein größeres Potenzial zur Kapazitätserweiterung und ist damit besser geeignet, die hohen Anforderungen an die Speicherkapazität von KI- und Hochleistungs-Computing-Workloads zu erfüllen. Innovationen in der Stacking-Technologie sind eine wichtige Voraussetzung für die Skalierung der DDR6-Kapazität. DDR6 wird fortschrittlichere 3D-Stacking-Packaging-Technologien einsetzen, bei denen mehr Speicherchips vertikal gestapelt werden, um die Kapazitätsdichte pro Chip deutlich zu erhöhen. Gleichzeitig erleichtert das modulare Design der CAMM2-Schnittstelle die Kapazitätserweiterung durch die Unterstützung gestapelter Modulkonfigurationen, um die Gesamtspeicherkapazität des Systems zu erhöhen.

So können beispielsweise zwei einkanalige CAMM2-Module des Typs D theoretisch entlang der Z-Achse gestapelt werden, wodurch der Gesamtsystemspeicher 512 GB erreichen kann. Wenn die Technologie weiter ausgereift ist, können sogar noch höhere Kapazitäten erreicht werden. Derzeit geplante DDR5-CAMM2-Module können eine maximale Kapazität von 256 GB erreichen. Mit Speicherchips höherer Dichte und Stacking-Technologien werden DDR6-CAMM2-Module diese Grenze voraussichtlich überschreiten.

Ein umfassender Vergleich zwischen DDR6 und DDR5

| Kategorie | DDR5 | DDR6 |

|---|---|---|

| Datenrate | Bis zu etwa 8000 MT/s | Ursprünglich 8800 MT/s, geplant ist eine Steigerung auf 17.600 MT/s, übertaktete Versionen können 21.000 MT/s überschreiten |

| Kanal-Architektur | 2 × 32-Bit (Gesamtbusbreite 64-Bit) | 4 × 24 Bit (Busbreite insgesamt 96 Bit) |

| Schnittstelle Formfaktor | Hauptsächlich DIMM, SO-DIMM | Vollständige Übernahme von CAMM2 / LPCAMM2 |

| Betriebsspannung | 1.1 V | 1,0 V oder niedriger |

| Typischer Stromverbrauch | Grundlegendes Niveau | 15-20% niedriger als DDR5 |

| Maximale Kapazität pro Modul | 256 GB (DIMM), 128 GB (SO-DIMM) | Erwartet werden mehr als 256 GB, durch Stapeln von zwei Modulen können 512 GB erreicht werden |

| Prefetch-Mechanismus | 8n Vorabruf | 16n Vorabruf |

| 2DPC Frequenzbegrenzung | Erhebliche Frequenzbeschränkungen | Komplexität wird innerhalb des Moduls gehandhabt, keine offensichtliche Frequenzbegrenzung |

| Wichtigste Anwendungsszenarien | Mittel- bis High-End-PCs, Server, Workstations (Übergangszeit) | KI-Server, Hochleistungscomputer, High-End-Workstations, Flaggschiff-PCs |

Kompatibilität von DDR6

Es gibt keine Abwärtskompatibilität zwischen DDR6 und DDR5. Das bedeutet, dass Motherboards, die für DDR5 entwickelt wurden, nicht direkt DDR6-Speicher verwenden können und umgekehrt. Der Hauptgrund liegt in den grundlegenden Unterschieden in der Architektur, den Schnittstellenformfaktoren und den elektrischen Spezifikationen.

Erstens gibt es einen Unterschied im Schnittstellenformfaktor. DDR6 verwendet vollständig die CAMM2-Schnittstelle, während DDR5 hauptsächlich traditionelle DIMM- und SO-DIMM-Schnittstellen verwendet. Ihre physischen Abmessungen und Anschlussmethoden sind völlig unterschiedlich, so dass sie nicht miteinander kompatibel sind.

Zweitens gibt es Unterschiede bei den elektrischen Spezifikationen. DDR6 senkt die Betriebsspannung auf 1,0 V oder noch niedriger, während sie bei DDR5 1,1 V beträgt. Außerdem sind ihre Signaldefinitionen und Zeitparameter völlig unterschiedlich. Speicher-Controller müssen unter Berücksichtigung spezifischer elektrischer Spezifikationen entwickelt werden, um Schaltungen anzusteuern und Signale korrekt zu verarbeiten. Ein DDR5-Speichercontroller kann die elektrischen Anforderungen von DDR6 nicht erfüllen, und eine erzwungene Verwendung würde zu einer Beschädigung des Geräts oder zu einem Ausfall des ordnungsgemäßen Betriebs führen.

Schließlich gibt es auch Unterschiede in der Kanalarchitektur. DDR6 verwendet eine 4 × 24-Bit-Unterkanalarchitektur, die sich grundlegend von der 2 × 32-Bit-Architektur von DDR5 unterscheidet. Die Entwurfslogik des Speicher-Controllers ist in beiden Fällen völlig unterschiedlich, was letztlich dazu führt, dass die beiden Standards nicht kompatibel sind. Daher erfordert die Einführung von DDR6 eine koordinierte Unterstützung durch CPUs, Hauptplatinen und das gesamte Ökosystem der Industrie, um ein vollständiges Hardware-Unterstützungssystem zu bilden. Gegenwärtig arbeiten Speicherhersteller wie Samsung, SK hynix und Micron eng mit Chip-Anbietern wie Intel, AMD und NVIDIA zusammen, um gemeinsam die Validierung der DDR6-Plattform voranzutreiben und die Entwicklung des Ökosystems zu beschleunigen.

Analyse des Anwendungsszenarios von DDR6

Rechenzentren und Cloud Computing

Rechenzentren und Cloud Computing gehören zu den wichtigsten Anwendungsszenarien für DDR6. Derzeit entwickeln sich Cloud-Computing-Dienste hin zu großem Umfang, hoher Gleichzeitigkeit und geringer Latenz. Rechenzentren müssen eine große Anzahl von Benutzeranfragen und Datenübertragungsaufgaben bewältigen, was extrem hohe Anforderungen an die Speicherbandbreite und -kapazität stellt. DDR6 kann die Speicherbandbreite in Rechenzentrumsservern deutlich erhöhen, die Datenverarbeitung und -übertragung beschleunigen und gleichzeitig die Antwortlatenz bei Benutzeranfragen verringern.

Gleichzeitig ist die hohe Energieeffizienz von DDR6 gut für die Anforderungen von Rechenzentren geeignet. Rechenzentren arbeiten mit einer hohen Serverdichte, und die Speichermodule machen einen erheblichen Teil des gesamten Systemstromverbrauchs aus. Im Vergleich zu DDR5 reduziert DDR6 den Stromverbrauch um 15-20%, was den Gesamtenergieverbrauch und die Kühlungskosten in Rechenzentren effektiv senken und gleichzeitig die Betriebseffizienz verbessern kann. Darüber hinaus unterstützt DDR6 die Erweiterung der Speicherkapazität und erfüllt damit die Anforderungen an das Caching großer Datenmengen und die Parallelverarbeitung in Cloud-Computing-Umgebungen. Dies bietet eine bessere Speicherunterstützung für Dienste wie Cloud-Datenbanken, Cloud-Speicher und Cloud-Rendering. Mit der kommerziellen Einführung von DDR6 werden die Rechen- und Datenverarbeitungsfähigkeiten von Rechenzentren voraussichtlich einen Qualitätssprung machen.

KI und Hochleistungsrechnen (HPC)

KI und High-Performance-Computing sind die treibenden Kräfte hinter der Entwicklung und Einführung von DDR6, und sie sind auch die Anwendungsszenarien, in denen DDR6 die größten Vorteile bieten kann. In KI-Trainingsszenarien werden die Modellparameter immer größer, was die Verarbeitung großer Mengen von Trainingsdaten erfordert. Dies stellt extreme Anforderungen an die Speicherbandbreite und -kapazität. Die hohen Bandbreiteneigenschaften von DDR6 sorgen dafür, dass CPUs und GPUs Trainingsdaten während des Trainingsprozesses schnell lesen und schreiben können, wodurch Engpässe bei der Datenübertragung vermieden und die Trainingseffizienz erheblich verbessert werden.

Im Bereich des Hochleistungsrechnens, z. B. bei der Wettervorhersage, bei astrophysikalischen Simulationen und in der pharmazeutischen Forschung, müssen die Systeme große Mengen komplexer Berechnungen und Datenverarbeitung durchführen. Diese Arbeitslasten erfordern ein extrem hohes Maß an Parallelverarbeitungsfähigkeit und Stabilität des Speichers. Die 4 × 24-Bit-Subkanal-Architektur von DDR6 verbessert die parallele Datenverarbeitung, während der 16n-Prefetch-Mechanismus und fortschrittliche Fehlerkorrekturmechanismen sowohl Effizienz als auch Stabilität bei der Datenübertragung gewährleisten. Darüber hinaus tragen die stromsparenden Vorteile von DDR6 zur Senkung des Energieverbrauchs in Hochleistungs-Computing-Clustern bei und verbessern deren Fähigkeit zum kontinuierlichen Betrieb über lange Zeiträume. Da KI und High-Performance-Computing weiter zunehmen, wird DDR6 zu einer zentralen Speicherkonfiguration in diesen Bereichen werden.

Consumer-PCs und High-End-Workstations

Obwohl DDR6 zunächst in Servern und KI-bezogenen Bereichen kommerziell eingesetzt wird, wird erwartet, dass es allmählich in die Märkte für Consumer-PCs und High-End-Workstations vordringt, wenn das Ökosystem reift und die Kosten sinken. Bei High-End-Gaming-Laptops und Flaggschiff-Desktop-PCs können die hohe Frequenz und die hohe Bandbreite von DDR6 die Ladezeiten von Spielen und die allgemeine Laufruhe verbessern. Dies macht sich vor allem bei großen AAA-Spielen bemerkbar, bei denen DDR6 Ruckler und Bildeinbrüche wirksam reduzieren kann. Gleichzeitig hilft das schlanke Design, das durch die CAMM2-Schnittstelle ermöglicht wird, den Herstellern, dünnere und leichtere Gaming-Laptops mit hoher Leistung zu entwickeln.

High-End-Workstations werden ebenfalls zu den ersten Verbrauchersegmenten gehören, die DDR6 einsetzen. Mobile Workstations und Grafik-Workstations werden in erster Linie für professionelle Arbeitsaufgaben wie Videobearbeitung, 3D-Modellierung und Animationsrendering eingesetzt, die sehr hohe Anforderungen an die Speicherfrequenz, Kapazität und Stabilität stellen. Herkömmlicher SO-DIMM-Speicher leidet unter Frequenzbeschränkungen bei 2DPC-Konfigurationen und kann die Leistungsanforderungen von High-End-Workstations nicht erfüllen. DDR6 in Kombination mit der CAMM2-Schnittstelle behebt dieses Problem und bietet gleichzeitig eine höhere Kapazität.

Normungsfortschritt und Zeitplan für die Kommerzialisierung

Die für führende Speichertechnologienormen zuständige Organisation JEDEC hat Ende 2024 den Entwurf der Hauptspezifikation für DDR6 fertiggestellt. Der Entwurf der Norm für LPDDR6, die auf mobile Geräte abzielt, wurde ebenfalls im zweiten Quartal 2025 veröffentlicht. Die nächste Phase wird die kritische Plattformtest- und Validierungsphase sein, die voraussichtlich 2026 stattfinden wird. Chip-Hersteller wie Intel und AMD werden daran teilnehmen, um die Kompatibilität zwischen DDR6 und künftigen Prozessorplattformen zu gewährleisten.

Branchenprognosen zufolge wird DDR6 voraussichtlich um 2027 in großem Umfang kommerziell eingesetzt werden. Es wird erwartet, dass seine Einführung einem Muster folgt, das vom High-End zum Mainstream führt. Sie wird zunächst in Bereichen eingesetzt, die extrem leistungsempfindlich, aber weniger kostenempfindlich sind, wie KI-Server, Hochleistungscomputersysteme und Rechenzentren. Danach wird sie sich allmählich auf den Markt für High-End-Laptops und Workstations ausweiten. Bei normalen Desktop-PCs und Laptops wird DDR6 erst gegen 2030 weit verbreitet sein.

DDR6 ist keine einfache Iteration, sondern eine architektonische Weiterentwicklung, mit der grundlegende Herausforderungen angegangen werden sollen. Sein Hauptziel ist es, die derzeitigen Engpässe bei der Speicherbandbreite und der Energieeffizienz zu überwinden und eine wesentliche Infrastrukturunterstützung für künstliche Intelligenz, Hochleistungscomputer und künftige groß angelegte Datenverarbeitung zu bieten. Der Weg von DDR1 zu DDR5 zeigt ein konsistentes Muster, bei dem sich die Speichertechnologie kontinuierlich weiterentwickelt, um den Anforderungen der Computertechnik gerecht zu werden. DDR6 stellt das nächste Kapitel in dieser Entwicklung dar. Es hat die Aufgabe, die Grenzen der Datenverarbeitung zu erweitern, und seine endgültige Form und weit verbreitete Einführung wird einen tiefgreifenden Einfluss auf die technologische Entwicklung des nächsten Jahrzehnts haben.