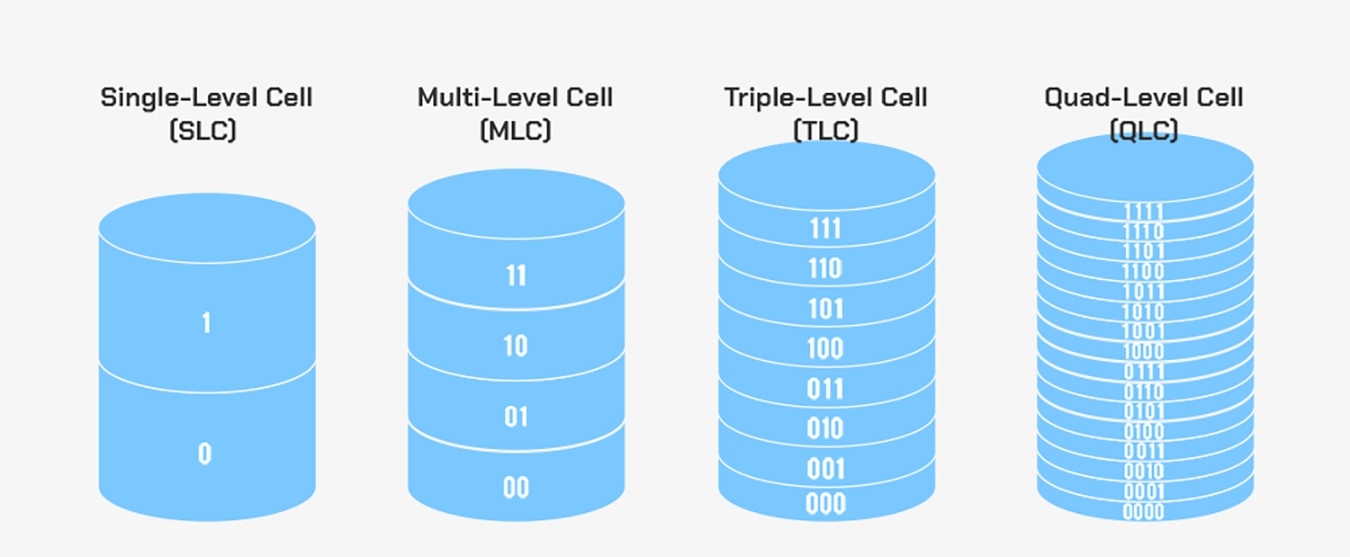

Wir befinden uns in einer Ära explodierender Datenmengen. KI-Training, der Betrieb von Cloud-Diensten, die Archivierung von hochauflösenden Videos und die Notwendigkeit, herkömmliche mechanische Festplatten zu ersetzen, führen zu einem fast grenzenlosen Bedarf an Speicherkapazität. Die Miniaturisierung der Halbleiterfertigungsprozesse stößt jedoch allmählich an physikalische Grenzen, so dass es entscheidend ist, die Kosten pro GB durch eine höhere Speicherdichte zu senken. Auf dem Weg der technologischen Entwicklung von SLC, das 1 Bit pro Zelle speichert, zu MLC mit 2 Bits, TLC mit 3 Bits und QLC mit 4 Bits stellt jeder Schritt eine neue Balance zwischen Kosten und Zuverlässigkeit dar. Heute gilt die PLC-Technologie (Penta-Level Cell), die 5 Bit Daten pro Zelle speichert, als eine der wichtigsten Entwicklungsrichtungen für die nächste Generation von Speichern mit hoher Dichte.

NAND-Flash-Grundlagen: Wie Charge Daten speichert

NAND-Flash ist eine Art nichtflüchtiger Speicher, d. h. er kann Daten auch nach dem Abschalten der Stromversorgung noch lange Zeit speichern. Seine Kernfunktionalität beruht auf der präzisen Steuerung der Ladungsmenge in jeder Speicherzelle. Die grundlegendste Speicherzelle kann als ein spezieller Transistor mit einer Isolierschicht, dem so genannten "Floating Gate", oder einer ähnlichen funktionellen "Ladungsfallenschicht" verstanden werden. Das Besondere an dieser Schicht ist, dass die injizierten Elektronen effektiv isoliert werden, so dass sie über einen langen Zeitraum gespeichert werden können, was eine dauerhafte Datenspeicherung ermöglicht.

Prinzip der DatenaufzeichnungDie spezifische Methode der Datenaufzeichnung ist durch die "Schwellenspannung" gekennzeichnet. Die Schwellenspannung ist die Mindestspannung, die zum Einschalten des Transistors erforderlich ist. Durch Injektion unterschiedlicher Mengen von Elektronen in das schwebende Gate werden die elektrischen Eigenschaften des Transistors verändert, wodurch sich seine Schwellenspannung ändert. Das Steuergerät legt eine Referenzspannung an und erkennt, ob sich der Transistor einschaltet, wodurch der aktuelle Schwellenspannungszustand der Zelle bestimmt wird. Jeder spezifische Spannungszustand entspricht einer eindeutigen Datenkodierung. Das Wesen der "Multi-Level-Cell"-Technologie besteht darin, mehr als zwei Schwellenspannungszustände innerhalb einer einzigen Zelle genau zu definieren und zu unterscheiden und dadurch mehr als ein Datenbit zu speichern.

Schreiben, Lesen und LöschenBasierend auf den oben genannten Prinzipien werden die Operationen auf NAND-Flash hauptsächlich in drei Arten unterteilt: Schreiben, Lesen und Löschen. Der Schreibvorgang, auch Programmierung genannt, wird durch die Injektion von Ladung in das Floating Gate der Zelle erreicht. Der Löschvorgang entfernt die Ladung aus dem Floating Gate und versetzt die Zelle in ihren Ausgangszustand zurück. Es ist besonders wichtig zu beachten, dass die kleinste Löscheinheit für NAND-Flash der "Block" ist, während Programmierung und Lesen auf der kleineren "Page"-Einheit durchgeführt werden können. Während eines Lesevorgangs legt der Controller eine Reihe von präzisen Referenzspannungen an die Zelle an. Indem er feststellt, ob sich der Transistor bei verschiedenen Spannungen einschaltet, bestimmt er die Schwellenspannung, die der aktuell gespeicherten Ladung entspricht, und dekodiert schließlich die gespeicherten Daten.

Der Aufstieg von 3D-NANDDa die Herstellungsprozesse weiter schrumpfen, stößt planarer NAND-Flash bei weiterer Verkleinerung auf physikalische Engpässe und Zuverlässigkeitsprobleme. Um die Kapazität weiter zu erhöhen, wandte sich die Branche der dreidimensionalen Stapelungstechnologie zu, die als 3D-NAND bekannt ist. Bei 3D-NAND werden die Speicherzellen vertikal gestapelt, wie beim Bau eines Wolkenkratzers, wodurch eine Vervielfachung der Speicherdichte auf derselben Fläche erreicht wird. Neben der dreidimensionalen Stapelung bleibt jedoch die Erhöhung der Anzahl der pro Speicherzelle gespeicherten Bits ein weiterer grundlegender technologischer Weg, um die Speicherdichte weiter zu erhöhen und die Kosten zu senken.

Entwicklung der Speichertechnologie: Von SLC zu QLC

Das Hauptziel der Entwicklung der Speichertechnologie ist die kontinuierliche Erhöhung der Speicherdichte, um die Kosten pro GB zu senken. Dieses Ziel wird in erster Linie durch die Erhöhung der Anzahl der pro Speicherzelle gespeicherten Bits erreicht. Im Folgenden wird der technologische Entwicklungspfad von SLC zu QLC skizziert.

SLC: Der Maßstab für Leistung und Verlässlichkeit

SLC steht für Single-Level Cell und speichert 1 Bit Daten pro Zelle. Dieses eine Datenbit entspricht zwei Ladezuständen, die in der Regel als 0 und 1 dargestellt werden. Da nur zwei Zustände unterschieden werden müssen, bietet SLC extrem hohe Lese-/Schreibgeschwindigkeiten, die längste Lebensdauer und die größte Datensicherheit. Sein Nachteil ist die geringste Speicherdichte, was zu den höchsten Kosten pro GB führt. Daher wird SLC hauptsächlich in Unternehmensservern und in der Industrie eingesetzt, wo Leistung und Zuverlässigkeit an erster Stelle stehen.

MLC: Das Gleichgewicht zwischen Leistung und Kosten

MLC steht für Multi-Level Cell und speichert 2 Bit Daten pro Zelle, was vier Ladezuständen entspricht. Durch die Speicherung von mehr Daten in jeder Zelle erreicht MLC die doppelte Speicherkapazität von SLC auf der gleichen Chipfläche und senkt die Kosten erheblich. Obwohl die Leistung, Lebensdauer und Zuverlässigkeit nicht so hoch sind wie bei SLC, erreichen sie ein gutes Gleichgewicht. MLC war lange Zeit die bevorzugte Wahl für High-End-Solid-State-Laufwerke für Verbraucher und Unternehmensspeicher.

TLC: Die erste Wahl für den Verbrauchermarkt

TLC steht für Triple-Level Cell und speichert 3 Bit Daten pro Zelle, was acht Ladezuständen entspricht. TLC baut die Vorteile der Speicherdichte und Kostenreduzierung weiter aus und wird zum absoluten Mainstream auf dem aktuellen SSD-Markt für Verbraucher. Mit fortschrittlichen Controller-Algorithmen und Fehlerkorrekturtechnologien entspricht die Ausdauer bereits den Anforderungen der meisten täglichen Anwendungen.

QLC: Die Praxis der hochdichten Lagerung

QLC steht für Quad-Level Cell und speichert 4 Bit Daten pro Zelle, was sechzehn Ladezuständen entspricht. Der Vorteil von QLC liegt in der hohen Speicherdichte und den geringeren Kosten, wodurch es sich sehr gut für den Bau von Solid-State-Laufwerken mit großer Kapazität eignet. Allerdings sind auch seine Nachteile deutlicher zu erkennen, darunter langsamere Schreibgeschwindigkeiten und eine weiter verkürzte Lebensdauer im Vergleich zu TLC. Derzeit wird QLC vor allem in Szenarien mit geringen Anforderungen an die Schreibleistung eingesetzt, z. B. bei der externen Speicherung großer Kapazitäten und der Speicherung kalter Daten in Rechenzentren.

Kernherausforderungen der Entwicklung

Die Entwicklung von SLC zu QLC ist keine einfache lineare Addition. Mit zunehmender Anzahl von Bits pro Zelle steigt die Anzahl der Spannungszustände, die präzise unterschieden werden müssen, exponentiell von 2 auf 16. Das bedeutet, dass das Spannungsfenster, das zur Unterscheidung der verschiedenen Zustände verwendet wird, extrem eng komprimiert ist, was die Anforderungen an die Präzision der Ladungssteuerung, die Fähigkeit zur Signalentstörung und die Fehlerkorrekturtechnologie extrem hoch werden lässt. Die Entwicklung der SPS-Technologie ist der nächste Schritt, der sich dieser zentralen Herausforderung direkt stellt.

Die PLC-Technologie

PLC, oder Penta-Level Cell, ist die nächste Stufe in der Entwicklung der NAND-Flash-Technologie. Ihr Hauptmerkmal ist die Steigerung der Speicherdichte in neue Höhen, aber sie steht auch vor noch nie dagewesenen technischen Herausforderungen.

Technische Definition von PLC

PLC steht für Penta-Level Cell, was bedeutet, dass jede Speicherzelle 5 Bits an Daten speichert. Diese 5 Bits entsprechen 32 verschiedenen Schwellenspannungszuständen. Im Vergleich zu den 16 Zuständen von QLC muss PLC die doppelte Anzahl von Spannungsebenen innerhalb desselben physikalischen Spannungsfensters genau definieren. Derzeit befindet sich diese Technologie noch in der Entwicklungs- und Verifizierungsphase, wobei führende Hersteller wie Solidigm erste Prototypprodukte vorführen, die die künftige Richtung der Speicherung mit hoher Dichte aufzeigen.

Primäre Herausforderung: Enges Spannungsfenster

Die grundlegende Herausforderung für die SPS-Technologie liegt auf der physikalischen Ebene. Um 32 Spannungszustände unterscheiden zu können, muss die Spannungsdifferenz zwischen jedem benachbarten Zustand auf einen sehr kleinen Wert komprimiert werden. Dadurch wird das Spannungsfenster extrem eng, und die Fehlertoleranz sinkt drastisch. Jede winzige Ladungsschwankung, eine Änderung der Transistoreigenschaften oder elektronisches Rauschen beim Auslesen könnte dazu führen, dass der Controller den Spannungszustand falsch einschätzt, was zu Datenfehlern führt. Man kann sagen, dass die Machbarkeitsgrenze der SPS direkt davon abhängt, ob dieses Problem des Signal-Rausch-Verhältnisses wirksam gelöst werden kann.

Technischer Durchbruch

Angesichts der extrem hohen nativen Bitfehlerraten hängt die Praxistauglichkeit von PLC in hohem Maße von bedeutenden Fortschritten bei den Speicher-Controllern und der Fehlerkorrekturtechnologie ab. Herkömmliche Fehlerkorrekturcodes können die Anforderungen nicht mehr erfüllen; es müssen leistungsfähigere Low-Density-Parity-Check-Codes in Kombination mit Soft-Decision-Decodierungstechnologie eingesetzt werden. Bei der Soft-Decision-Decodierung wird das Signal nicht einfach als 0 oder 1 bewertet, sondern durch Wahrscheinlichkeitsberechnungen auf den wahrscheinlichsten Datenwert geschlossen, was die Fehlerkorrekturfähigkeit erheblich verbessert. Außerdem muss das Steuergerät über intelligente Mechanismen zur Wiederholung des Lesevorgangs verfügen. Wenn der erste Lesevorgang fehlschlägt, kann er die Referenzspannung für mehrere Lesevorgänge dynamisch anpassen, um den richtigen Signalpunkt zu finden. Diese komplexen Algorithmusprozesse stellen sehr hohe Anforderungen an die Rechenleistung des Controllers.

Auswirkung auf Leistung und Lebenserwartung

Die Merkmale der PLC-Technologie wirken sich auch direkt auf ihre Leistung und Zuverlässigkeit aus. Da eine feinere Steuerung der Ladungsinjektion erforderlich ist, um 32 Spannungszustände zu erreichen, erfordert der Schreibvorgang mehr Programmverifizierungszyklen, was im Vergleich zu QLC und TLC zu deutlich langsameren Schreibgeschwindigkeiten führt. Was die Lebensdauer betrifft, so beschleunigen häufigere und präzisere Ladevorgänge die Alterung der Speicherzellen. Daher dürfte die native Lebensdauer von PLC-Flash niedriger sein als die von QLC. Um diese Schwäche in praktischen Anwendungen zu kompensieren, sind weitere Kompensationsmaßnahmen auf Systemebene erforderlich, wie z. B. die Konfiguration eines höheren Over-Provisioning, die Einführung aggressiverer Algorithmen zum Ausgleich der Datenabnutzung und der Einsatz von SLC-Caching, um Burst-Schreiblasten aufzufangen.

Unterschiede zwischen den fünf Speicherzellentechnologien

Die folgende Tabelle zeigt deutlich die Unterschiede zwischen den fünf NAND-Flash-Speicherzellentechnologien von SLC bis PLC in Bezug auf die wichtigsten Kennzahlen.

| Technologie Typ | Bits pro Zelle | Anzahl der Staaten | Relative Kosten | Relative Ausdauer | Hauptvorteil | Typische Anwendungsszenarien |

|---|---|---|---|---|---|---|

| SLC | 1 Bit | 2 | Höchste | Höchste | Ultrahohe Geschwindigkeit, sehr lange Lebensdauer, hohe Zuverlässigkeit | Unternehmensrelevanter Hochgeschwindigkeits-Cache |

| MLC | 2 Bits | 4 | Hoch | Hoch | Ausgezeichnetes Verhältnis zwischen Leistung und Kosten | Unternehmens-SSD, High-End-Verbraucher-SSD |

| TLC | 3 Bits | 8 | Mittel | Mittel | Mainstream-Wahl für Kosten und Kapazität | Mainstream-Verbraucher-SSD, mobile Geräte |

| QLC | 4 Bits | 16 | Niedrig | Relativ niedrig | Hohe Speicherdichte, niedrige Kosten | Verbraucher-SSD mit großer Kapazität, Cold Storage für Rechenzentren |

| PLC | 5 Bits | 32 | Erwartungsgemäß niedrig | Erwartungsgemäß niedrig | Höchste Speicherdichte, niedrigste Kosten | Archivierung kalter Daten im Ultra-Großformat |

Aus der Tabelle lässt sich ein klarer Trend ablesen: Mit zunehmender Anzahl der pro Zelle gespeicherten Bits verbessern sich die Speicherdichte und die Kosteneffizienz kontinuierlich, was jedoch auf Kosten der Lese-/Schreibgeschwindigkeit und der Lebensdauer der Zellen geht. Daher eignen sich die verschiedenen Technologien für ganz unterschiedliche Szenarien. SLC wird in Bereichen eingesetzt, in denen höchste Anforderungen an Leistung und Zuverlässigkeit gestellt werden, während das Ziel von PLC darin besteht, eine äußerst kosteneffiziente Speicherlösung für massive kalte Daten innerhalb akzeptabler Leistungs- und Lebensdauergrenzen zu bieten.

Wert, Positionierung und Zukunft der PLC-Technologie

Ultimativer Kosten- und Dichtevorteil. Die treibende Kraft hinter der Entwicklung der PLC-Technologie ist das Streben nach ultimativer Speicherdichte und Kosteneffizienz. Durch die Unterbringung von 5 Bit Daten pro Speicherzelle kann PLC eine höhere Speicherkapazität als QLC auf der gleichen Chip-Waferfläche bieten. Dies führt direkt zu niedrigeren Kosten pro GB. Der primäre Zielmarkt ist es, Bereiche zu ersetzen, die derzeit von mechanischen Festplatten mit hoher Kapazität dominiert werden, und eine kalte Datenspeicherlösung für Hyperscale-Rechenzentren anzubieten, die Vorteile beim Stromverbrauch pro Volumeneinheit, bei der Zugriffsgeschwindigkeit und beim Platzbedarf bietet.

Schwerwiegende Herausforderungen. Die Massenproduktion und die Anwendung der SPS-Technologie stehen vor mehreren großen Herausforderungen. Erstens erfordert die Unterscheidung von 32 Spannungszuständen eine noch nie dagewesene Regelungspräzision, was zu geringen anfänglichen Produktionserträgen und einer äußerst komplexen Qualitätskontrolle führt. Zweitens benötigt der Controller für eine zuverlässige Datenspeicherung leistungsstarke Echtzeit-Rechenkapazitäten, um komplexe Fehlerkorrekturalgorithmen auszuführen, was den Designaufwand und den Stromverbrauch des Hauptcontrollerchips erhöht. Schließlich ist die native Lebensdauer von PLC-Flash gering und muss durch Techniken auf Systemebene kompensiert werden, z. B. durch die Festlegung größerer Over-Provisioning-Bereiche, die Einführung effizienterer Daten Verschleißausgleich und Garbage-Collection-Mechanismen. All dies erhöht die Komplexität des Designs der Gesamtlösung.

Anwendungsszenario Positionierung.Aufgrund seiner technischen Merkmale ist das Anwendungsszenario des PLC sehr klar und spezifisch. Sie eignet sich hervorragend für extrem kalte Datenarchivierungsszenarien, in denen Schreibvorgänge extrem selten sind und die Häufigkeit von Lesezugriffen sehr gering ist. Beispiele hierfür sind tiefe Archivspeicherschichten in Cloud-Diensten, langfristige Datensicherungen zur Einhaltung gesetzlicher Vorschriften, historische Protokolldateien und die Bewahrung digitaler Bestände wie medizinischer Bilder. Umgekehrt ist PLC für schreibintensive Aufgaben wie Betriebssysteme, Datenbanken und häufig aktualisierte Anwendungsdaten völlig ungeeignet. Seine Aufgabe ist es, die kostengünstigste Basisschicht mit der höchsten Kapazität im Datenspeicher-Ökosystem zu sein.

Zukunftsaussichten.Die kommerzielle Einführung der PLC-Technologie hängt nicht nur von der Reife der Flash-Speicherchips selbst ab, sondern auch von der koordinierten Entwicklung von Controller-Chips, Firmware-Algorithmen und sogar dem gesamten Ökosystem des Datenspeichersystems. Sie stellt die Auslotung der physikalischen Grenzen der NAND-Flash-Technologie im Rahmen der derzeitigen Architektur dar. Die Industrie ist allgemein der Ansicht, dass PLC sich der praktischen Grenze der Verbesserung der Dichte auf Zellebene auf der Grundlage des Ladungsspeicherprinzips nähern könnte. Künftige Fortschritte werden sich eher auf die kontinuierliche Erhöhung der 3D-Stapelschichten und die Nutzung technologischer Innovationen wie künstliche Intelligenz zur Optimierung des Datenmanagements und der Fehlerkorrektureffizienz stützen, um so auf Systemebene einen Durchbruch bei der Leistung und Zuverlässigkeit zu erzielen.

PLC NAND Flash stellt eine wichtige Herausforderung für die physikalischen Grenzen der derzeitigen Architektur der Speichertechnologie dar. Es handelt sich um eine natürliche Entwicklung, die durch das kontinuierliche Streben nach niedrigeren Kosten und höherer Speicherdichte vorangetrieben wird. Obwohl ihre inhärenten Eigenschaften bestimmen, dass sie in erster Linie für bestimmte Bereiche eingesetzt werden, wird erwartet, dass PLC durch die kontinuierliche Optimierung von Controller-Algorithmen und Lösungen auf Systemebene eine unverzichtbare Rolle im zukünftigen Datenspeicher-Ökosystem spielen wird, indem es massive Mengen an kalten Daten aufnehmen kann.