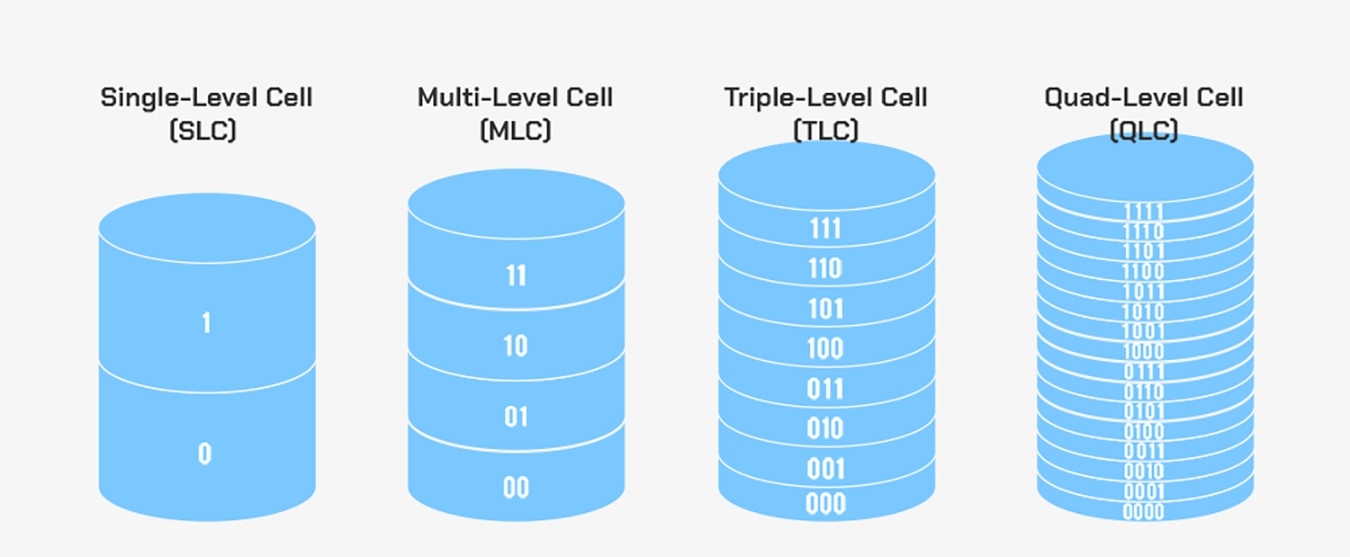

Estamos numa era de explosão do volume de dados. O treino de IA, as operações de serviços na nuvem, o arquivamento de vídeo de alta definição e a procura de substituir os discos rígidos mecânicos tradicionais estão a impulsionar um desejo quase ilimitado de capacidade de armazenamento. No entanto, a miniaturização dos processos de fabrico de semicondutores está gradualmente a aproximar-se dos limites físicos, tornando crucial a redução do custo por GB através do aumento da densidade de armazenamento. No caminho da evolução tecnológica, do SLC que armazena 1 bit por célula, ao MLC com 2 bits, ao TLC com 3 bits e ao QLC com 4 bits, cada passo representa um novo equilíbrio entre custo e fiabilidade. Atualmente, a tecnologia PLC (Penta-Level Cell), que armazena 5 bits de dados por célula, é vista como uma direção de desenvolvimento fundamental para a próxima geração de armazenamento de alta densidade.

Noções básicas sobre flash NAND: como o carregamento armazena dados

Flash NAND é um tipo de memória não volátil, o que significa que pode reter dados durante muito tempo, mesmo depois de desligada. A sua principal funcionalidade assenta no controlo preciso da quantidade de carga dentro de cada célula de memória. A célula de memória mais básica pode ser entendida como um transístor especial com uma camada isolante denominada "porta flutuante" ou uma "camada de retenção de carga" funcional semelhante. O aspeto único desta camada é que os electrões injectados são efetivamente isolados, o que permite que sejam armazenados durante muito tempo, possibilitando o armazenamento persistente de dados.

Princípio do registo de dadosO método específico de registo de dados é caracterizado pela "tensão de limiar". A tensão de limiar é a tensão mínima necessária para ligar o transístor. Ao injetar diferentes quantidades de electrões na porta flutuante, as caraterísticas eléctricas do transístor são alteradas, mudando assim a sua tensão de limiar. O controlador aplica uma tensão de referência e detecta se o transístor se liga, determinando assim o estado atual da tensão de limiar da célula. Cada estado de tensão específico corresponde a uma codificação de dados única. A essência da tecnologia de "célula multinível" é definir e distinguir com precisão mais de dois estados de tensão de limiar numa única célula, armazenando assim mais de um bit de dados.

Escrever, ler e apagarCom base nos princípios acima referidos, as operações no Flash NAND dividem-se principalmente em três tipos: escrita, leitura e apagamento. A operação de escrita, também designada por programação, é realizada através da injeção de carga na porta flutuante da célula. A operação de apagamento remove a carga da porta flutuante, repondo a célula no seu estado inicial. É particularmente importante notar que a unidade de apagamento mais pequena para NAND Flash é o "bloco", enquanto a programação e a leitura podem ser efectuadas na unidade mais pequena "página". Durante uma operação de leitura, o controlador aplica uma série de tensões de referência precisas à célula. Ao detetar se o transístor se liga a diferentes tensões, determina a tensão de limiar correspondente à carga atualmente armazenada, descodificando finalmente os dados armazenados.

A ascensão do 3D NANDÀ medida que os processos de fabrico continuam a diminuir, a tecnologia Flash NAND plana deparou-se com estrangulamentos físicos e problemas de fiabilidade com uma maior redução de tamanho. Para continuar a aumentar a capacidade, a indústria voltou-se para a tecnologia de empilhamento tridimensional, conhecida como 3D NAND. A NAND 3D empilha as células de memória verticalmente, como se estivesse a construir um arranha-céus, obtendo uma multiplicação da densidade de armazenamento na mesma área plana. No entanto, para além do empilhamento tridimensional, o aumento do número de bits armazenados por célula de memória continua a ser outra via tecnológica fundamental para aumentar ainda mais a densidade de armazenamento e reduzir os custos.

Evolução da tecnologia de armazenamento: Do SLC ao QLC

O principal objetivo da evolução da tecnologia de armazenamento é aumentar continuamente a densidade de armazenamento para reduzir o custo por GB. Este objetivo é atingido principalmente através do aumento do número de bits armazenados por célula de memória. De seguida, descreve-se o percurso de desenvolvimento tecnológico do SLC ao QLC.

SLC: A referência para desempenho e fiabilidade

SLC significa Single-Level Cell (célula de nível único), armazenando 1 bit de dados por célula. Este 1 bit de dados corresponde a dois estados de carga, normalmente representados por 0 e 1. Uma vez que só é necessário distinguir dois estados, a SLC oferece velocidades de leitura/escrita extremamente elevadas, a vida útil mais longa e a maior fiabilidade dos dados. A sua desvantagem é a densidade de armazenamento mais baixa, o que resulta no custo mais elevado por GB. Por conseguinte, o SLC é utilizado principalmente em servidores empresariais e em áreas industriais onde o desempenho e a fiabilidade são fundamentais.

MLC: O ponto de equilíbrio entre desempenho e custo

MLC significa Multi-Level Cell (célula multinível), que armazena 2 bits de dados por célula, correspondendo a quatro estados de carga. Ao armazenar mais dados em cada célula, a MLC consegue o dobro da capacidade de armazenamento da SLC na mesma área de chip, reduzindo significativamente o custo. Embora o seu desempenho, vida útil e fiabilidade não sejam tão elevados como os do SLC, atingem um bom equilíbrio. O MLC foi durante muito tempo a escolha principal para unidades de estado sólido de gama alta e armazenamento empresarial.

TLC: A escolha principal para o mercado de consumo

TLC significa Triple-Level Cell (célula de nível triplo), que armazena 3 bits de dados por célula, correspondendo a oito estados de carga. A TLC expande ainda mais as vantagens da densidade de armazenamento e da redução de custos, tornando-se o mainstream absoluto no atual mercado de SSD de consumo. Com algoritmos de controlador avançados e tecnologias de correção de erros, a sua resistência já satisfaz as necessidades da grande maioria das aplicações diárias.

QLC: A prática do armazenamento de alta densidade

QLC significa Quad-Level Cell (célula de quatro níveis), armazenando 4 bits de dados por célula, o que corresponde a dezasseis estados de carga. A vantagem do QLC reside na sua elevada densidade de armazenamento e no seu baixo custo, tornando-o muito adequado para a construção de unidades de estado sólido de grande capacidade. No entanto, as suas desvantagens são também mais óbvias, incluindo velocidades de escrita mais lentas e uma vida útil mais reduzida em comparação com a TLC. Atualmente, o QLC é utilizado principalmente em cenários com baixos requisitos de desempenho de escrita, como o armazenamento externo de grande capacidade e o armazenamento de dados a frio em centros de dados.

Principais desafios subjacentes à evolução

A evolução do SLC para o QLC não é uma simples adição linear. À medida que o número de bits por célula aumenta, o número de estados de tensão que precisam de ser distinguidos com precisão cresce exponencialmente, de 2 para 16. Isto significa que a janela de tensão utilizada para distinguir os diferentes estados é comprimida de forma extremamente estreita, tornando os requisitos de precisão do controlo de carga, a capacidade de anti-interferência do sinal e a tecnologia de correção de erros extremamente rigorosos. O desenvolvimento da tecnologia PLC é o próximo passo para enfrentar diretamente este desafio central.

A tecnologia PLC

PLC, ou Penta-Level Cell, é o próximo estágio na evolução da tecnologia NAND Flash. A sua principal caraterística é levar a densidade de armazenamento a novos patamares, mas também enfrenta desafios de engenharia sem precedentes.

Definição técnica de PLC

PLC significa Penta-Level Cell, ou seja, cada célula de memória armazena 5 bits de dados. Estes 5 bits correspondem a 32 estados diferentes de tensão de limiar. Em comparação com os 16 estados da QLC, a PLC precisa de definir com precisão o dobro do número de níveis de tensão dentro da mesma janela de tensão física. Atualmente, esta tecnologia ainda se encontra na fase de desenvolvimento e verificação, com fabricantes líderes como a Solidigm a demonstrarem pela primeira vez protótipos de produtos, indicando a direção futura do armazenamento de alta densidade.

Desafio principal: Janela de tensão estreita

O desafio fundamental que a tecnologia PLC enfrenta tem origem no nível físico. Para distinguir 32 estados de tensão, a diferença de tensão entre cada estado adjacente deve ser comprimida para um valor muito pequeno. Isto torna a janela de tensão extremamente estreita e a tolerância ao erro cai drasticamente. Qualquer pequena flutuação de carga, variação das caraterísticas do transístor ou ruído eletrónico durante a leitura pode fazer com que o controlador julgue mal o estado da tensão, conduzindo a erros de dados. Pode dizer-se que o limite de viabilidade do PLC depende diretamente da possibilidade de ultrapassar eficazmente este desafio da relação sinal/ruído.

Avanço da engenharia

Face a taxas de erro de bits nativas extremamente elevadas, a viabilidade do PLC depende em grande medida de avanços significativos nos controladores de armazenamento e na tecnologia de correção de erros. Os códigos de correção de erros tradicionais já não conseguem satisfazer as exigências; devem ser adoptados códigos de verificação de paridade de baixa densidade mais potentes combinados com tecnologia de descodificação de decisão suave. A descodificação por decisão suave não se limita a julgar o sinal como 0 ou 1, mas infere o valor mais provável dos dados através de cálculos de probabilidade, melhorando significativamente a capacidade de correção de erros. Além disso, o controlador precisa de ter mecanismos inteligentes de tentativa de leitura. Quando a leitura inicial falha, pode ajustar dinamicamente a tensão de referência para várias leituras para encontrar o ponto de sinal correto. Estes complexos processos algorítmicos colocam exigências muito elevadas à capacidade computacional do controlador.

Impacto no desempenho e no tempo de vida

As caraterísticas da tecnologia PLC também afectam diretamente o seu desempenho e fiabilidade. Dado que é necessário um controlo mais preciso da injeção de carga para fazer corresponder 32 estados de tensão, o processo de escrita requer mais ciclos de verificação de programas, o que conduz a velocidades de escrita significativamente mais lentas em comparação com a QLC e a TLC. Em termos de vida útil, as operações de carga mais frequentes e precisas aceleram o envelhecimento das células de memória. Por conseguinte, prevê-se que a resistência nativa do flash PLC seja inferior à do QLC. Para compensar esta fraqueza em aplicações práticas, são necessárias mais medidas de compensação a nível do sistema, como a configuração de um maior aprovisionamento excessivo, a adoção de algoritmos de nivelamento de desgaste de dados mais agressivos e a utilização de cache SLC para absorver as cargas de escrita de rajada.

Diferenças entre as cinco tecnologias de células de memória

A tabela abaixo mostra claramente as diferenças nas principais métricas entre as cinco tecnologias de células de memória Flash NAND, da SLC à PLC.

| Tipo de tecnologia | Bits por célula | Número de Estados | Custo relativo | Resistência relativa | Vantagem principal | Cenários de aplicação típicos |

|---|---|---|---|---|---|---|

| SLC | 1 bit | 2 | Mais alto | Mais alto | Velocidade ultra-elevada, vida útil muito longa, elevada fiabilidade | Cache de alta velocidade e de missão crítica para empresas |

| MLC | 2 bits | 4 | Elevado | Elevado | Excelente equilíbrio entre desempenho e custo | SSD para empresas, SSD para consumidores de topo de gama |

| TLC | 3 bits | 8 | Médio | Médio | Escolha comum em termos de custo e capacidade | SSD de consumo corrente, dispositivos móveis |

| QLC | 4 bits | 16 | Baixa | Relativamente baixo | Alta densidade de armazenamento, baixo custo | SSD de grande capacidade para consumidores, armazenamento a frio em centros de dados |

| PLC | 5 bits | 32 | Prevê-se que seja baixo | Prevê-se que seja baixo | Máxima densidade de armazenamento, menor custo | Arquivamento de dados a frio em escala ultra grande |

A tabela mostra uma tendência clara: à medida que o número de bits armazenados por célula aumenta, a densidade de armazenamento e a relação custo-eficácia melhoram continuamente, mas isso é feito à custa da velocidade de leitura/escrita e do tempo de vida das células. Por conseguinte, as diferentes tecnologias são adequadas para cenários distintamente diferentes. A SLC serve áreas com as exigências mais rigorosas em termos de desempenho e fiabilidade, enquanto o objetivo da PLC é fornecer uma solução de armazenamento altamente rentável para dados frios maciços dentro de limites aceitáveis de desempenho e tempo de vida útil.

Valor, posicionamento e futuro da tecnologia PLC

A melhor vantagem em termos de custo e densidade. A força motriz fundamental por detrás do desenvolvimento da tecnologia PLC é a procura da máxima densidade de armazenamento e da melhor relação custo-eficácia. Ao acomodar 5 bits de dados por célula de memória, a PLC pode proporcionar uma maior capacidade de armazenamento do que a QLC na mesma área de pastilha. Isto traduz-se diretamente num menor custo por GB. O seu principal mercado-alvo é substituir as áreas atualmente dominadas por discos rígidos mecânicos de alta capacidade, oferecendo uma solução de armazenamento de dados a frio para centros de dados de hiperescala que apresenta vantagens em termos de consumo de energia por unidade de volume, velocidade de acesso e área física.

Grandes desafios enfrentados. A produção em massa e a aplicação da tecnologia PLC enfrentam vários desafios graves. Em primeiro lugar, a distinção de 32 estados de tensão exige uma precisão de controlo sem precedentes, o que leva a baixos rendimentos iniciais de produção e a um controlo de qualidade extremamente complexo. Em segundo lugar, para conseguir um armazenamento de dados fiável, o controlador necessita de poderosas capacidades de computação em tempo real para executar algoritmos complexos de correção de erros, aumentando a dificuldade de conceção e o consumo de energia do chip controlador principal. Por último, a resistência nativa do flash PLC é baixa e tem de ser compensada por técnicas a nível do sistema, como a definição de áreas de sobreprovisionamento maiores e a adoção de mecanismos mais eficientes de nivelamento do desgaste dos dados e de recolha de lixo. Todos estes factores aumentam a complexidade da conceção da solução global.

Cenário de aplicação Posicionamento.Com base nas suas caraterísticas técnicas, o posicionamento do PLC no cenário de aplicação é muito claro e específico. É altamente adequado para cenários de arquivo de dados ultra-frios em que as operações de escrita são extremamente raras e a frequência de acesso de leitura é muito baixa. Os exemplos incluem níveis de armazenamento de arquivos profundos em serviços de nuvem, cópias de segurança de dados a longo prazo para conformidade regulamentar, ficheiros de registo históricos e a preservação de bens digitais como imagens médicas. Por outro lado, o PLC é completamente inadequado para tarefas de escrita intensiva, como sistemas operativos, bases de dados e dados de aplicações frequentemente actualizados. A sua função é ser o nível fundamental de menor custo e maior capacidade no ecossistema de armazenamento de dados.

Perspectivas futuras.A adoção comercial da tecnologia PLC depende não só da maturidade das próprias pastilhas de memória flash, mas também do desenvolvimento coordenado das pastilhas controladoras, dos algoritmos de firmware e mesmo de todo o ecossistema do sistema de armazenamento de dados. Representa a exploração dos limites físicos da tecnologia Flash NAND no âmbito da arquitetura atual. De um modo geral, a indústria considera que a PLC pode estar a aproximar-se do limite prático da melhoria da densidade a nível das células com base no princípio do armazenamento de carga. Os progressos futuros dependerão mais do aumento contínuo das camadas de empilhamento 3D e do aproveitamento de inovações tecnológicas, como a inteligência artificial, para otimizar a gestão de dados e a eficiência da correção de erros, conseguindo assim avanços a nível do sistema em termos de desempenho e fiabilidade.

O PLC NAND Flash representa um importante desafio aos limites físicos da atual arquitetura da tecnologia de armazenamento. Trata-se de uma evolução natural impulsionada pela procura contínua de necessidades de armazenamento de menor custo e maior densidade. Embora as suas caraterísticas inerentes determinem que servirá principalmente campos específicos, através da otimização contínua dos algoritmos do controlador e das soluções a nível do sistema, espera-se que a PLC desempenhe um papel indispensável no futuro ecossistema de armazenamento de dados, acomodando enormes quantidades de dados frios.