Uma vez que a memória DDR5 acaba de completar a sua penetração inicial no mercado de consumo e continua a aumentar constantemente a sua adoção no sector dos servidores, as discussões sobre a DDR6 começaram discretamente a aquecer, tanto dentro como fora da indústria. Não se trata de um "entusiasmo demasiado prematuro" no domínio da tecnologia, mas sim de um resultado inevitável da procura do mercado e da evolução tecnológica. Atualmente, áreas como a inteligência artificial generativa, a computação de alto desempenho e a computação em nuvem estão a registar um crescimento explosivo, colocando requisitos rigorosos sem precedentes na largura de banda, capacidade e eficiência energética da memória. De acordo com as previsões da TrendForce, de 2024 a 2026, as aplicações relacionadas com a IA e os servidores representarão 46%, 56% e 66% da procura total de capacidade DRAM, respetivamente, e este valor deverá ultrapassar os 70% em 2027. Mesmo a atual memória DDR5 mais potente está a tornar-se gradualmente insuficiente para satisfazer os requisitos de débito de dados maciços do treino de IA e dos cenários de processamento de dados em grande escala.

Ao mesmo tempo, no mercado de consumo, os computadores portáteis de gama alta para jogos e as estações de trabalho móveis continuam a procurar frequências de memória mais elevadas e maiores capacidades, enquanto os dispositivos finos e leves impõem limitações rigorosas ao consumo de energia da memória e ao espaço físico. Todos estes factores estão a acelerar o desenvolvimento de uma nova geração de normas de memória. Os principais fabricantes mundiais de memórias, como a Samsung, a SK hynix e a Micron, já concluíram o desenvolvimento dos primeiros protótipos das especificações DDR6 e estão a trabalhar em conjunto com os fornecedores de chips, incluindo a Intel, a AMD e a NVIDIA, para avançar com a validação da plataforma.

Como a memória DDR evoluiu

O que é a memória DDR e porque é que a "largura de banda" é tão importante

A memória DDR, abreviatura de Double Data Rate Synchronous Dynamic Random Access Memory, é o componente central dos sistemas informáticos responsável pelo armazenamento temporário de dados. Serve também como ponte de transferência de dados entre a CPU e os dispositivos de armazenamento, como os discos rígidos. O seu princípio de funcionamento baseia-se num sinal de relógio síncrono que permite que os dados sejam transferidos nas extremidades ascendente e descendente de cada ciclo de relógio. Como resultado, a eficiência da transferência de dados é duplicada com a mesma frequência de relógio, que é a origem do termo "taxa de dados dupla".

Entre todas as métricas de desempenho da memória DDR, a largura de banda é, sem dúvida, a mais crítica. A largura de banda da memória refere-se à quantidade de dados que a memória pode transferir por unidade de tempo. É calculada através da fórmula: largura de banda = frequência da memória × largura do bus × número de canais ÷ 8. A largura de banda determina diretamente a rapidez com que a CPU pode aceder aos dados. Pode ser comparada a uma "autoestrada" para transmissão de dados: quanto mais larga a autoestrada, maior a eficiência da transferência de dados. Em cenários de aplicações complexas, como a execução de grandes jogos AAA, a edição e renderização de vídeo ou o treino de modelos de IA, a CPU precisa de ler e escrever continuamente grandes quantidades de dados a alta velocidade. Se a largura de banda da memória for insuficiente, ocorre um "congestionamento de dados", fazendo com que a CPU espere pelos dados durante longos períodos. Nestes casos, mesmo uma CPU muito potente não consegue ter um desempenho pleno, criando um estrangulamento no desempenho do sistema. Por isso, melhorar a largura de banda da memória sempre foi um dos principais objectivos na evolução de cada geração da tecnologia de memória DDR.

De DDR1 a DDR5: que problemas cada geração resolveu

Da DDR1 à DDR5, cada geração de memória foi concebida para responder diretamente aos principais desafios enfrentados pela indústria na altura, alcançando melhorias significativas de desempenho através da inovação tecnológica. A DDR1, a primeira geração de memória DDR, surgiu por volta do ano 2000. A sua principal inovação foi a implementação da transmissão de taxa de dados dupla, substituindo a SDRAM tradicional e resolvendo inicialmente o problema das velocidades de transferência de memória insuficientes nos primeiros sistemas informáticos. Forneceu suporte de memória compatível para os primeiros processadores, como o Pentium 4, com velocidades de transferência de dados entre 200 e 400 MT/s.

A memória DDR2 foi introduzida por volta de 2004 e abordou principalmente as limitações da DDR1, incluindo a sua baixa velocidade máxima e o consumo de energia relativamente elevado. Ao melhorar os processos de fabrico de chips de memória e as tecnologias de processamento de sinais, a DDR2 aumentou as taxas de dados para 533-800 MT/s, ao mesmo tempo que reduziu a tensão de funcionamento de 2,5 V na DDR1 para 1,8 V. Isto reduziu significativamente o consumo de energia e a produção de calor, tornando-a mais adequada para o desenvolvimento de processadores multi-core na altura.

A memória DDR3, que surgiu em 2007, ultrapassou ainda mais as limitações de velocidade, aumentando a taxa de dados máxima para 1600 MT/s e reduzindo a tensão de funcionamento para 1,5 V, o que resultou numa grande melhoria da eficiência energética. Mais importante ainda, a DDR3 melhorou a estabilidade e a compatibilidade da memória através de um design optimizado do controlador de memória. Suportou a adoção generalizada em computadores portáteis, computadores de secretária e servidores, tornando-se uma das normas de memória mais duradouras.

A memória DDR4, lançada em 2014, foi concebida para satisfazer a dupla procura de capacidade de memória e largura de banda na era dos grandes volumes de dados. Aumentou as taxas de dados para 2133-3200 MT/s e reduziu a tensão de funcionamento para 1,2 V, ao mesmo tempo que suporta capacidades de módulo único muito maiores, com um máximo de até 128 GB por módulo. Ao introduzir a tecnologia Bank Group, a DDR4 melhorou as capacidades de acesso simultâneo à memória e reduziu eficazmente a pressão da largura de banda em cenários de multitarefas, tornando-se a configuração de memória principal para sistemas informáticos na última década.

A memória DDR5, oficialmente comercializada no final de 2021, alcançou outro grande salto em velocidade e eficiência energética para atender aos primeiros requisitos de IA e computação de alto desempenho. A sua taxa de dados máxima atinge até 8000 MT/s, a tensão de funcionamento é ainda mais reduzida para 1,1 V e adopta uma estrutura de canal de 2 × 32 bits para melhorar as capacidades de processamento paralelo. A DDR5 também introduziu a correção de erros ECC on-die pela primeira vez na memória de consumo, melhorando a estabilidade da transmissão de dados, com capacidades de módulo único que atingem até 256 GB. No entanto, à medida que as aplicações de IA continuam a crescer de forma explosiva, os limites de desempenho da DDR5 estão a tornar-se gradualmente aparentes, lançando as bases para o desenvolvimento da DDR6.

O que é a DDR6

A DDR6 é a norma de Memória de Acesso Aleatório Dinâmica Síncrona de Dupla Velocidade de Dados da próxima geração, liderada pelo JEDEC (Conselho Conjunto de Engenharia de Dispositivos Electrónicos). Ele foi projetado para atender às demandas extremas de largura de banda, capacidade e eficiência energética da memória, impulsionadas por campos emergentes como inteligência artificial, computação de alto desempenho e computação em nuvem. O processo de normalização da DDR6 começou oficialmente em 2024, com o objetivo principal de ultrapassar os limites de desempenho físico da DDR5 e criar uma plataforma de memória que ofereça elevada largura de banda, grande capacidade, elevada eficiência energética e elevada fiabilidade.

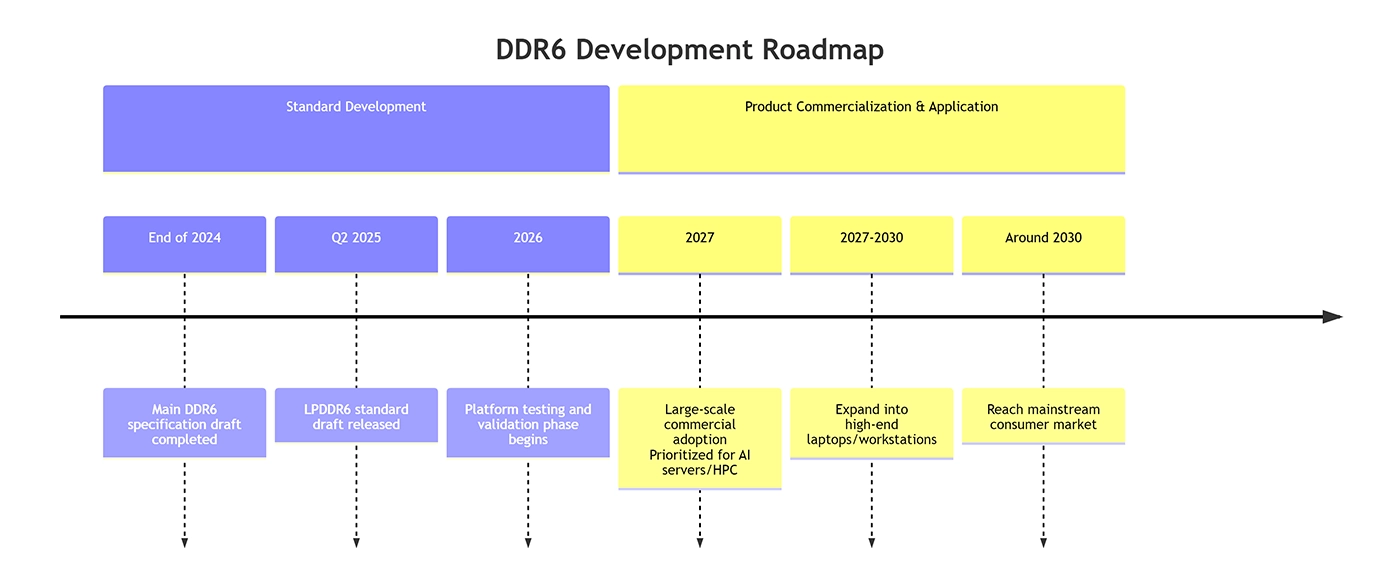

No final de 2024, o JEDEC concluiu o projeto de especificação principal da DDR6, lançando as bases para o subsequente desenvolvimento tecnológico e implementação de produtos. Ao mesmo tempo, o projeto de especificação para a versão de baixo consumo, LPDDR6, foi lançado no segundo trimestre de 2025. À semelhança dos anteriores processos de desenvolvimento de normas de memória, a formulação da DDR6 reúne os principais fabricantes mundiais de memórias, projectistas de chips e fornecedores de dispositivos finais. Isto assegura que a norma pode suportar diferentes cenários de aplicação e plataformas de hardware, ao mesmo tempo que promove o desenvolvimento coordenado em todo o ecossistema da indústria.

Os três principais problemas que a DDR6 pretende resolver

O desenvolvimento da DDR6 centra-se na resposta a três desafios fundamentais que a indústria enfrenta atualmente: largura de banda insuficiente, baixa eficiência energética e limitações arquitectónicas.

O primeiro problema é a largura de banda insuficiente. Com o rápido crescimento da procura de formação em IA e de processamento de dados em grande escala, a atual velocidade máxima da DDR5 de 8000 MT/s é cada vez mais incapaz de satisfazer os requisitos de transmissão a alta velocidade de grandes quantidades de dados, tornando-se um estrangulamento fundamental que limita o desempenho geral do sistema. A DDR6 melhora a arquitetura do canal e as tecnologias de transmissão para aumentar a taxa de dados inicial para 8800 MT/s, com planos para a aumentar para 17 600 MT/s em fases posteriores, com o objetivo de eliminar fundamentalmente os estrangulamentos da largura de banda em cenários de carga elevada.

A segunda questão é a eficiência energética. Em servidores de IA e ambientes de centros de dados, os módulos de memória são implementados em densidades cada vez mais elevadas, o que aumenta significativamente o consumo de energia e a geração de calor. Isso não só aumenta os custos operacionais, mas também impõe maiores exigências aos sistemas de refrigeração. Ao reduzir a tensão operacional e otimizar os mecanismos de gerenciamento de energia, a DDR6 melhora o desempenho e reduz o consumo de energia. Espera-se que o consumo típico de energia seja reduzido em 15-20% em comparação com a DDR5, tornando a DDR6 mais adequada para cenários de implantação de alta densidade.

A terceira questão prende-se com as limitações arquitectónicas. A estrutura de canais de 2 × 32 bits utilizada pela DDR5 é propensa a problemas de integridade do sinal a altas frequências. Além disso, os factores de forma tradicionais DIMM e SO-DIMM sofrem de grandes requisitos de espaço e limitações de frequência em configurações 2DPC. A DDR6 introduz uma inovadora arquitetura de sub-canais de 4 × 24 bits e adopta a norma de interface CAMM2. Isto não só melhora a capacidade de processamento paralelo, como também resolve os constrangimentos de espaço e frequência do empacotamento de memória tradicional, fornecendo suporte arquitetónico para a implementação de memória de alto desempenho e alta densidade.

Principais alterações técnicas na DDR6

Um grande salto na velocidade de transferência de dados

Um aumento significativo da velocidade de transferência de dados é um dos avanços tecnológicos mais importantes da DDR6. De acordo com os actuais roteiros da indústria, a DDR6 começará com uma velocidade de transferência de dados inicial de 8800 MT/s, ultrapassando já o atual máximo da DDR5 de 8000 MT/s. Ao longo de todo o ciclo de vida do produto, prevê-se que as velocidades da DDR6 aumentem ainda mais para 17.600 MT/s, com algumas versões com overclock a poderem ultrapassar os 21.000 MT/s. Prevê-se que o desempenho global seja aproximadamente duas a três vezes superior ao da DDR5.

Um aumento de velocidade tão substancial não é conseguido simplesmente através do aumento da frequência de relógio. Em vez disso, resulta do efeito combinado de várias tecnologias. Por um lado, a DDR6 optimiza os processos de fabrico de chips de memória, melhorando o desempenho elétrico e fornecendo uma base de hardware para o funcionamento a alta frequência. Por outro lado, a DDR6 introduz concepções mais avançadas de otimização da integridade do sinal, incluindo tecnologias de empacotamento melhoradas, regras de encaminhamento mais finas e um controlo mais rigoroso da temporização. Estas medidas reduzem efetivamente a interferência e a atenuação do sinal a altas frequências. Além disso, a DDR6 adopta um mecanismo de pré-busca de 16n, em comparação com a pré-busca de 8n utilizada na DDR5. Isso melhora ainda mais a eficiência da transferência de dados, permitindo que mais dados sejam transmitidos na mesma frequência de clock e possibilitando um grande salto na velocidade geral de transferência.

Alterações na arquitetura dos subcanais

A DDR6 introduz uma inovação revolucionária na arquitetura do canal ao adotar uma estrutura de sub-canais de 4 × 24 bits, substituindo a conceção de canais de 2 × 32 bits utilizada pela DDR5. O principal objetivo desta alteração arquitetónica é melhorar a largura de banda, mantendo a integridade do sinal a altas frequências de funcionamento. Os designs tradicionais de barramento largo tendem a sofrer de interferência de sinal quando as frequências aumentam para além de um determinado ponto, levando a uma redução da estabilidade da transmissão. Ao aumentar o número de canais e reduzir a largura de bits de cada canal, a DDR6 expande a largura total do barramento de 64 bits na DDR5 para 96 bits. Esta abordagem aumenta a capacidade de processamento paralelo, ao mesmo tempo que reduz a pressão de transmissão do sinal em cada canal individual.

A arquitetura de sub-canais de 4 × 24 bits permite uma transmissão de dados paralela mais eficiente, permitindo que cada sub-canal efectue operações de leitura e escrita de forma independente. Isto melhora significativamente a simultaneidade da memória e a utilização da largura de banda. Em cenários como o treino de IA e o processamento de dados em grande escala, em que vários fluxos de dados têm de ser tratados em simultâneo, as vantagens desta arquitetura tornam-se especialmente evidentes. Ao mesmo tempo, a arquitetura de sub-canal proporciona uma maior flexibilidade para expansão da capacidade e otimização da eficiência energética. Permite que o estado operacional de cada sub-canal seja ajustado dinamicamente de acordo com os requisitos da aplicação, alcançando um melhor equilíbrio entre desempenho e consumo de energia.

Alterações nos factores de forma dos módulos e interfaces (CAMM2)

A DDR6 adoptará totalmente a norma de interface CAMM2, substituindo as tradicionais interfaces DIMM e SO-DIMM que têm sido utilizadas há muitos anos. Isto representa uma grande transformação nos factores de forma dos módulos de memória. CAMM2 significa Compression Attached Memory Module. Foi originalmente introduzido pela Dell, mais tarde revisto pelo JEDEC, e tornou-se oficialmente uma norma JEDEC no final de 2023. Ao contrário dos módulos de memória tradicionais que se ligam às ranhuras através de conectores de extremidade na parte inferior, o CAMM2 utiliza um conetor de compressão que se liga através de uma placa adaptadora fina na placa-mãe e é fixado com parafusos. Esta nova forma de interface traz várias vantagens significativas:

O CAMM2 resolve efetivamente as limitações de frequência encontradas nas configurações 2DPC tradicionais. Nos designs 2DPC convencionais, a instalação de dois módulos de memória por canal aumenta a complexidade eléctrica e limita a frequência da memória. O CAMM2 desloca a topologia complexa para o próprio módulo, gerindo a complexidade internamente e permitindo que um sistema atinja o máximo desempenho e a máxima capacidade ao mesmo tempo.

O CAMM2 reduz significativamente a altura do eixo Z e a utilização geral do espaço da placa-mãe. Em comparação com o SO-DIMM, o CAMM2 reduz a espessura em 57%, tornando-o mais adequado para dispositivos com requisitos de espessura rigorosos, tais como computadores portáteis finos e leves e computadores tablet.

O conetor CAMM2 utiliza um design de pinos LGA, com almofadas de contacto tanto na placa-mãe como no módulo de memória. Isto reduz o risco de danos na interface e o próprio conetor pode ser substituído de forma independente, tornando a manutenção mais conveniente.

Maior evolução da eficiência energética e da gestão de energia

Em termos de otimização da eficiência energética, a DDR6 baseia-se nas vantagens de baixo consumo de energia da DDR5 e alcança novos avanços. A tensão de funcionamento normal da DDR5 é de 1,1 V, ao passo que a DDR6 reduzirá a tensão de funcionamento para 1,0 V ou mesmo menos. Uma tensão mais baixa conduz diretamente a uma redução do consumo de energia, prevendo-se que o consumo de energia típico da DDR6 seja 15-20% inferior ao da DDR5. Essa melhoria é especialmente importante para cenários de implantação de alta densidade, como centros de dados e servidores de IA, pois ajuda a reduzir o consumo geral de energia e os custos de resfriamento, melhorando a eficiência energética do sistema.

Para além de reduzir a tensão de funcionamento, a DDR6 introduz mecanismos de gestão de energia mais avançados. Ao otimizar a lógica de gestão de energia do controlador de memória, a DDR6 pode ajustar dinamicamente o estado de funcionamento dos módulos de memória com base na carga do sistema. Em condições de baixa carga, a frequência e a tensão da memória são automaticamente reduzidas, permitindo que o sistema entre em modos de baixo consumo de energia. Em condições de alta carga, o desempenho é rapidamente aumentado para garantir que os requisitos de transmissão de dados sejam atendidos. Esta abordagem dinâmica de gestão de energia permite que a DDR6 atinja um equilíbrio ótimo entre o desempenho e o consumo de energia em diferentes cenários de aplicação, proporcionando um elevado desempenho e conservando eficazmente a energia.

Expansão da capacidade e potencial de empilhamento

A DDR6 oferece maior potencial de expansão de capacidade, tornando-a mais adequada para atender aos requisitos de grande capacidade de memória de IA e cargas de trabalho de computação de alto desempenho. As inovações na tecnologia de empilhamento são um fator essencial para o aumento da capacidade da DDR6. A DDR6 adoptará tecnologias de embalagem de empilhamento 3D mais avançadas, empilhando mais matrizes de memória verticalmente para aumentar significativamente a densidade de capacidade por chip. Ao mesmo tempo, o design modular da interface CAMM2 facilita a expansão da capacidade, suportando configurações de módulos empilhados para aumentar a capacidade total de memória do sistema.

Por exemplo, dois módulos CAMM2 de canal único do tipo D podem teoricamente ser empilhados ao longo do eixo Z, permitindo que a memória total do sistema atinja 512 GB. À medida que a tecnologia amadurece, podem ser alcançados avanços de capacidade ainda maiores. Os módulos DDR5 CAMM2 atualmente planeados podem atingir uma capacidade máxima de 256 GB. Com chips de memória de maior densidade e tecnologias de empilhamento, espera-se que os módulos DDR6 CAMM2 ultrapassem esse limite.

Uma comparação abrangente entre DDR6 e DDR5

| Categoria | DDR5 | DDR6 |

|---|---|---|

| Taxa de dados | Até cerca de 8000 MT/s | Inicialmente 8800 MT/s, planeado para aumentar para 17.600 MT/s, as versões com overclock podem exceder 21.000 MT/s |

| Arquitetura de canais | 2 × 32 bits (largura total do barramento de 64 bits) | 4 × 24 bits (largura total do barramento de 96 bits) |

| Interface Fator de forma | Principalmente DIMM, SO-DIMM | Adoção integral de CAMM2 / LPCAMM2 |

| Tensão de funcionamento | 1.1 V | 1,0 V ou inferior |

| Consumo típico de energia | Nível de base | 15-20% inferior a DDR5 |

| Capacidade máxima por módulo | 256 GB (DIMM), 128 GB (SO-DIMM) | Prevê-se que exceda os 256 GB, o empilhamento de módulos duplos pode atingir os 512 GB |

| Mecanismo de pré-busca | 8n pré-busca | 16n pré-busca |

| Limitação de frequência 2DPC | Limitações significativas de frequência | Complexidade gerida dentro do módulo, sem limitação óbvia de frequência |

| Principais cenários de aplicação | PCs, servidores e estações de trabalho de gama média a alta (período de transição) | Servidores de IA, computação de alto desempenho, estações de trabalho topo de gama, PCs topo de gama |

Compatibilidade da DDR6

Não existe retrocompatibilidade entre DDR6 e DDR5. Isto significa que as placas-mãe concebidas para DDR5 não podem utilizar diretamente a memória DDR6 e vice-versa. A razão principal reside nas diferenças fundamentais na arquitetura, nos factores de forma da interface e nas especificações eléctricas.

Em primeiro lugar, existe uma diferença no fator de forma da interface. A DDR6 adopta totalmente a interface CAMM2, enquanto a DDR5 utiliza principalmente as interfaces DIMM e SO-DIMM tradicionais. As suas dimensões físicas e métodos de ligação são completamente diferentes, tornando-as incompatíveis entre si.

Em segundo lugar, existem diferenças nas especificações eléctricas. A DDR6 reduz a tensão de funcionamento para 1,0 V ou mesmo menos, em comparação com 1,1 V para a DDR5. Além disso, as suas definições de sinal e parâmetros de temporização são totalmente diferentes. Os controladores de memória têm de ser concebidos tendo em conta especificações eléctricas específicas para acionarem os circuitos e tratarem os sinais corretamente. Um controlador de memória DDR5 não pode cumprir os requisitos eléctricos da DDR6 e a sua utilização forçada resultaria em danos no dispositivo ou no seu funcionamento incorreto.

Por último, existem diferenças na arquitetura dos canais. A DDR6 utiliza uma arquitetura de sub-canais de 4 × 24 bits, que é fundamentalmente diferente da arquitetura de 2 × 32 bits utilizada pela DDR5. A lógica de conceção do controlador de memória é completamente diferente em cada caso, o que acaba por determinar a incompatibilidade entre as duas normas. Por conseguinte, a implementação da DDR6 exige o apoio coordenado das CPU, das placas-mãe e de todo o ecossistema da indústria para formar um sistema completo de suporte de hardware. Atualmente, os fabricantes de memórias, como a Samsung, a SK hynix e a Micron, estão a trabalhar em estreita colaboração com os fornecedores de circuitos integrados, incluindo a Intel, a AMD e a NVIDIA, para avançar em conjunto com a validação da plataforma DDR6 e acelerar o desenvolvimento do ecossistema.

Análise do cenário de aplicação da DDR6

Centros de dados e computação em nuvem

Os centros de dados e a computação em nuvem estão entre os cenários de aplicação mais importantes para a DDR6. Atualmente, os serviços de computação em nuvem estão a evoluir para grande escala, elevada concorrência e baixa latência. Os centros de dados têm de lidar com um grande número de pedidos de utilizadores e tarefas de transferência de dados, colocando exigências extremamente elevadas na largura de banda e capacidade da memória. A DDR6 pode aumentar significativamente a largura de banda da memória nos servidores dos centros de dados, acelerando o processamento e a transmissão de dados e reduzindo a latência de resposta aos pedidos dos utilizadores.

Ao mesmo tempo, a alta eficiência energética da DDR6 é adequada aos requisitos dos centros de dados. Os centros de dados operam com alta densidade de servidores e os módulos de memória são responsáveis por uma parte substancial do consumo total de energia do sistema. Em comparação com a DDR5, a DDR6 reduz o consumo de energia em 15-20%, o que pode efetivamente reduzir o uso geral de energia e os custos de refrigeração em centros de dados, melhorando a eficiência operacional. Além disso, a DDR6 suporta expansão de grande capacidade, atendendo às necessidades de cache de dados em grande escala e processamento paralelo em ambientes de computação em nuvem. Isso fornece um suporte de memória mais forte para serviços como bancos de dados em nuvem, armazenamento em nuvem e renderização em nuvem. Com a adoção comercial da DDR6, espera-se que as capacidades de computação e processamento de dados dos centros de dados dêem um salto qualitativo.

IA e computação de alto desempenho (HPC)

A IA e a computação de alto desempenho são as principais forças motrizes por trás do desenvolvimento e adoção da DDR6, e são também os cenários de aplicação em que a DDR6 pode oferecer as maiores vantagens. Em cenários de treinamento de IA, o tamanho dos parâmetros do modelo continua a crescer, exigindo o processamento de grandes quantidades de dados de treinamento. Isso impõe demandas extremas à largura de banda e à capacidade da memória. As caraterísticas de alta largura de banda da DDR6 garantem que as CPUs e GPUs possam ler e gravar rapidamente os dados de treinamento durante o processo de treinamento, evitando gargalos na transferência de dados e melhorando significativamente a eficiência do treinamento.

No domínio da computação de elevado desempenho, como a previsão meteorológica, as simulações astrofísicas e a investigação farmacêutica, os sistemas têm de efetuar grandes volumes de cálculos complexos e de processamento de dados. Estas cargas de trabalho requerem níveis extremamente elevados de capacidade de processamento paralelo e estabilidade da memória. A arquitetura de sub-canais de 4 × 24 bits da DDR6 melhora o processamento paralelo de dados, enquanto o mecanismo de pré-busca 16n e os mecanismos avançados de correção de erros garantem a eficiência e a estabilidade na transmissão de dados. Além disso, as vantagens de baixo consumo de energia da DDR6 ajudam a reduzir o consumo de energia em clusters de computação de alto desempenho, melhorando sua capacidade de operar continuamente por longos períodos. À medida que a IA e a computação de alto desempenho continuam a expandir-se, a DDR6 tornar-se-á uma configuração de memória essencial nestes campos.

PCs de consumo e estações de trabalho topo de gama

Embora a DDR6 seja implantada comercialmente em primeiro lugar nos servidores e nos domínios relacionados com a IA, espera-se que penetre gradualmente nos mercados dos PC de consumo e das estações de trabalho topo de gama à medida que o ecossistema amadurece e os custos diminuem. Para os computadores portáteis de gama alta para jogos e para os PC de secretária topo de gama, a elevada frequência e a elevada largura de banda da DDR6 podem melhorar os tempos de carregamento dos jogos e a suavidade geral. Isto é especialmente notório na execução de jogos AAA de grande dimensão, em que a DDR6 pode reduzir eficazmente a gaguez e a queda de fotogramas. Ao mesmo tempo, o design fino possibilitado pela interface CAMM2 ajuda os fabricantes a criar computadores portáteis para jogos mais finos e leves com elevado desempenho.

As estações de trabalho topo de gama também estarão entre os primeiros segmentos de consumidores a adotar a DDR6. As estações de trabalho móveis e as estações de trabalho gráficas são utilizadas principalmente para cargas de trabalho profissionais, como edição de vídeo, modelação 3D e renderização de animação, que colocam exigências muito elevadas em termos de frequência, capacidade e estabilidade da memória. A memória SO-DIMM tradicional sofre de limitações de frequência em configurações 2DPC e não consegue satisfazer os requisitos de desempenho das estações de trabalho topo de gama. A DDR6 combinada com a interface CAMM2 resolve esse problema e, ao mesmo tempo, oferece suporte a uma maior capacidade.

Progresso da normalização e cronograma de comercialização

A organização responsável pelas principais normas de tecnologia de memória, a JEDEC, concluiu o projeto da principal especificação DDR6 no final de 2024. O projeto de norma para LPDDR6, destinado a dispositivos móveis, foi também lançado no segundo trimestre de 2025. A próxima etapa será a fase crítica de teste e validação da plataforma, que deverá ter lugar em 2026. Os fabricantes de chips, como a Intel e a AMD, participarão para garantir a compatibilidade entre a DDR6 e as futuras plataformas de processadores.

De acordo com as previsões do sector, prevê-se que a DDR6 entre em grande escala comercial por volta de 2027. Prevê-se que a sua trajetória de adoção siga um padrão de ponta a ponta. Começará por ser utilizada em domínios extremamente sensíveis ao desempenho mas menos sensíveis ao custo, como os servidores de IA, os sistemas de computação de alto desempenho e os centros de dados. Em seguida, expandir-se-á gradualmente para os mercados de computadores portáteis topo de gama e estações de trabalho. Os utilizadores habituais de PCs de secretária e de computadores portáteis comuns poderão não encontrar amplamente a DDR6 até cerca de 2030.

A DDR6 não é uma simples iteração, mas uma evolução arquitetónica concebida para enfrentar desafios fundamentais. O seu principal objetivo é ultrapassar os actuais estrangulamentos na largura de banda da memória e na eficiência energética, fornecendo um suporte de infraestrutura essencial para a inteligência artificial, a computação de elevado desempenho e o futuro processamento de dados em grande escala. A jornada da DDR1 até a DDR5 demonstra um padrão consistente no qual a tecnologia de memória evolui continuamente para atender às demandas da computação. A DDR6 representa o próximo capítulo dessa progressão. Tem a missão de expandir as fronteiras da computação, e a sua forma final e adoção generalizada terão um impacto profundo na trajetória do desenvolvimento tecnológico na próxima década.