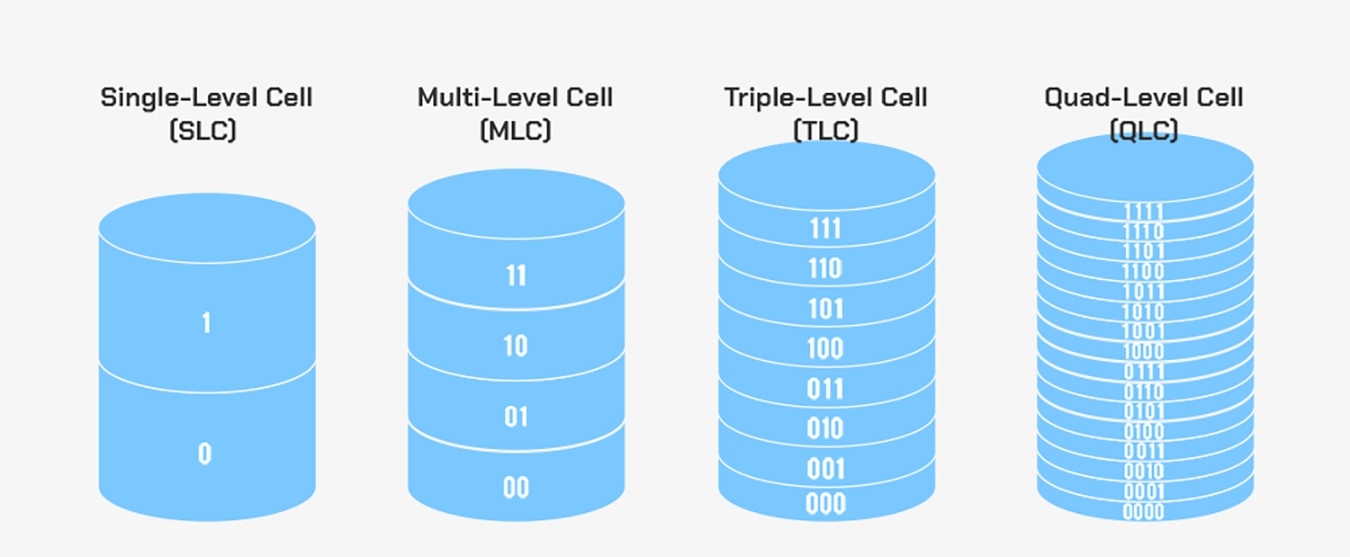

Siamo in un'epoca di esplosione del volume di dati. L'addestramento dell'intelligenza artificiale, le operazioni di servizi cloud, l'archiviazione di video ad alta definizione e la richiesta di sostituire i tradizionali dischi rigidi meccanici stanno determinando un desiderio quasi illimitato di capacità di archiviazione. Tuttavia, la miniaturizzazione dei processi di produzione dei semiconduttori si sta gradualmente avvicinando ai limiti fisici, rendendo cruciale la riduzione del costo per GB attraverso l'aumento della densità di archiviazione. Nel percorso di evoluzione tecnologica, da SLC che memorizza 1 bit per cella, a MLC con 2 bit, TLC con 3 bit e QLC con 4 bit, ogni passo rappresenta un nuovo equilibrio tra costi e affidabilità. Oggi la tecnologia PLC (Penta-Level Cell), che memorizza 5 bit di dati per cella, è considerata una direzione di sviluppo fondamentale per lo storage ad alta densità di prossima generazione.

Nozioni di base sulla NAND Flash: come la carica memorizza i dati

Flash NAND è un tipo di memoria non volatile, cioè in grado di conservare i dati per molto tempo anche dopo lo spegnimento. La sua funzionalità principale si basa sul controllo preciso della quantità di carica all'interno di ogni cella di memoria. La cella di memoria più elementare può essere intesa come uno speciale transistor con uno strato isolante chiamato "gate flottante" o un analogo strato funzionale "trappola di carica". L'aspetto unico di questo strato è che gli elettroni iniettati vengono isolati in modo efficace, consentendo di conservarli a lungo e di memorizzare i dati in modo persistente.

Principio di registrazione dei datiIl metodo specifico di registrazione dei dati è caratterizzato dalla "tensione di soglia". La tensione di soglia è la tensione minima necessaria per accendere il transistor. Iniettando diverse quantità di elettroni nel gate flottante, le caratteristiche elettriche del transistor vengono modificate, cambiando così la sua tensione di soglia. Il controllore applica una tensione di riferimento e rileva se il transistor si accende, determinando così lo stato attuale della tensione di soglia della cella. Ogni stato di tensione specifico corrisponde a una codifica di dati unica. L'essenza della tecnologia delle "celle multilivello" consiste nel definire e distinguere con precisione più di due stati di tensione di soglia all'interno di una singola cella, memorizzando così più di un bit di dati.

Scrittura, lettura e cancellazioneSulla base di questi principi, le operazioni su NAND Flash si dividono principalmente in tre tipi: scrittura, lettura e cancellazione. L'operazione di scrittura, detta anche programmazione, si ottiene iniettando carica nel gate flottante della cella. L'operazione di cancellazione rimuove la carica dal gate flottante, riportando la cella allo stato iniziale. È particolarmente importante notare che l'unità di cancellazione più piccola per la NAND Flash è il "blocco", mentre la programmazione e la lettura possono essere eseguite sull'unità più piccola "pagina". Durante un'operazione di lettura, il controller applica una serie di tensioni di riferimento precise alla cella. Rilevando se il transistor si accende a tensioni diverse, determina la tensione di soglia corrispondente alla carica attualmente memorizzata, decodificando infine i dati memorizzati.

L'ascesa della NAND 3DCon la continua riduzione dei processi di produzione, la NAND Flash planare ha incontrato colli di bottiglia fisici e problemi di affidabilità con l'ulteriore riduzione delle dimensioni. Per continuare ad aumentare la capacità, il settore si è rivolto alla tecnologia di impilamento tridimensionale, nota come 3D NAND. La 3D NAND impila le celle di memoria verticalmente, come se si trattasse di un grattacielo, ottenendo una moltiplicazione della densità di memorizzazione sulla stessa area planare. Tuttavia, oltre all'impilamento tridimensionale, l'aumento del numero di bit memorizzati per cella di memoria rimane un'altra strada tecnologica fondamentale per migliorare ulteriormente la densità di memorizzazione e ridurre i costi.

Evoluzione della tecnologia di archiviazione: Da SLC a QLC

L'obiettivo principale dell'evoluzione della tecnologia di memorizzazione è quello di aumentare continuamente la densità di memorizzazione per ridurre il costo per GB. Questo obiettivo viene raggiunto principalmente aumentando il numero di bit memorizzati per cella di memoria. Di seguito viene illustrato il percorso di sviluppo tecnologico da SLC a QLC.

SLC: il punto di riferimento per prestazioni e affidabilità

SLC è l'acronimo di Single-Level Cell, che memorizza 1 bit di dati per cella. Questo 1 bit di dati corrisponde a due stati di carica, tipicamente rappresentati come 0 e 1. Poiché è necessario distinguere solo due stati, SLC offre velocità di lettura/scrittura estremamente elevate, la durata più lunga e la massima affidabilità dei dati. Lo svantaggio è la minore densità di memorizzazione, che comporta il costo più elevato per GB. Per questo motivo, SLC viene utilizzato principalmente nei server aziendali e nei settori industriali in cui le prestazioni e l'affidabilità sono fondamentali.

MLC: il punto di equilibrio tra prestazioni e costi

MLC è l'acronimo di Multi-Level Cell, che memorizza 2 bit di dati per cella, corrispondenti a quattro stati di carica. Memorizzando più dati in ogni cella, MLC raggiunge una capacità di memorizzazione doppia rispetto a SLC sulla stessa area del chip, riducendo significativamente i costi. Sebbene le prestazioni, la durata e l'affidabilità non siano così elevate come quelle di SLC, raggiungono un buon equilibrio. L'MLC è stato a lungo la scelta principale per le unità a stato solido di fascia alta per i consumatori e per lo storage aziendale.

TLC: la scelta principale per il mercato dei consumatori

TLC è l'acronimo di Triple-Level Cell, che memorizza 3 bit di dati per cella, corrispondenti a otto stati di carica. TLC espande ulteriormente i vantaggi della densità di memorizzazione e della riduzione dei costi, diventando il mainstream assoluto nell'attuale mercato delle SSD consumer. Grazie agli algoritmi di controllo avanzati e alle tecnologie di correzione degli errori, la sua resistenza soddisfa già le esigenze della maggior parte delle applicazioni quotidiane.

QLC: la pratica dello stoccaggio ad alta densità

QLC è l'acronimo di Quad-Level Cell, che memorizza 4 bit di dati per cella, corrispondenti a sedici stati di carica. Il vantaggio del QLC risiede nell'elevata densità di memorizzazione e nel costo inferiore, che lo rendono molto adatto alla costruzione di unità a stato solido di grande capacità. Tuttavia, anche i suoi svantaggi sono più evidenti, tra cui una velocità di scrittura più bassa e una durata di vita ulteriormente ridotta rispetto a TLC. Attualmente, il QLC viene utilizzato principalmente in scenari con requisiti di prestazioni di scrittura ridotti, come l'archiviazione esterna di grande capacità e l'archiviazione di dati freddi nei data center.

Le sfide principali alla base dell'evoluzione

L'evoluzione da SLC a QLC non è una semplice addizione lineare. Con l'aumento del numero di bit per cella, il numero di stati di tensione che devono essere distinti con precisione cresce in modo esponenziale, da 2 a 16. Ciò significa che la finestra di tensione utilizzata per distinguere i diversi stati è estremamente ristretta. Ciò significa che la finestra di tensione utilizzata per distinguere i diversi stati è compressa in modo estremamente stretto, rendendo i requisiti per la precisione del controllo di carica, la capacità di anti-interferenza del segnale e la tecnologia di correzione degli errori estremamente severi. Lo sviluppo della tecnologia PLC è il passo successivo per affrontare direttamente questa sfida fondamentale.

La tecnologia PLC

PLC, o Penta-Level Cell, è la prossima fase dell'evoluzione della tecnologia NAND Flash. La sua caratteristica principale è quella di spingere la densità di memorizzazione a nuovi livelli, ma deve anche affrontare sfide ingegneristiche senza precedenti.

Definizione tecnica di PLC

PLC è l'acronimo di Penta-Level Cell, ovvero ogni cella di memoria memorizza 5 bit di dati. Questi 5 bit corrispondono a 32 diversi stati di tensione di soglia. Rispetto ai 16 stati della QLC, la PLC deve definire con precisione il doppio dei livelli di tensione all'interno della stessa finestra fisica di tensione. Attualmente questa tecnologia è ancora in fase di sviluppo e di verifica, con produttori leader come Solidigm che hanno mostrato per la prima volta dei prototipi, indicando la direzione futura della memoria ad alta densità.

Sfida principale: finestra di tensione ristretta

La sfida fondamentale che la tecnologia PLC deve affrontare deriva dal livello fisico. Per distinguere 32 stati di tensione, la differenza di tensione tra ogni stato adiacente deve essere compressa a un valore molto piccolo. Ciò rende la finestra di tensione estremamente stretta e la tolleranza all'errore si riduce drasticamente. Qualsiasi piccola fluttuazione di carica, variazione della caratteristica del transistor o rumore elettronico durante la lettura potrebbe indurre il controllore a giudicare erroneamente lo stato di tensione, causando errori nei dati. Si può affermare che il limite di fattibilità del PLC dipende direttamente dalla possibilità di superare efficacemente questa sfida del rapporto segnale/rumore.

Un'innovazione ingegneristica

Di fronte a tassi di errore di bit nativi estremamente elevati, la praticabilità del PLC dipende in larga misura da progressi significativi nei controller di archiviazione e nella tecnologia di correzione degli errori. I codici di correzione degli errori tradizionali non sono più in grado di soddisfare le richieste; è necessario adottare codici Low-Density Parity-Check più potenti combinati con la tecnologia di decodifica a decisione morbida. La decodifica soft-decision non si limita a giudicare il segnale come 0 o 1, ma infonde il valore più probabile dei dati attraverso calcoli di probabilità, migliorando notevolmente la capacità di correzione degli errori. Inoltre, il controllore deve disporre di meccanismi intelligenti di ripetizione della lettura. Quando la lettura iniziale non va a buon fine, può regolare dinamicamente la tensione di riferimento per più letture per trovare il punto di segnale corretto. Questi complessi processi algoritmici impongono requisiti molto elevati alla potenza di calcolo del controllore.

Impatto sulle prestazioni e sulla durata di vita

Anche le caratteristiche della tecnologia PLC influiscono direttamente sulle prestazioni e sull'affidabilità. Poiché è necessario un controllo più preciso dell'iniezione di carica per far corrispondere 32 stati di tensione, il processo di scrittura richiede un maggior numero di cicli di verifica del programma, con conseguenti velocità di scrittura significativamente più basse rispetto a QLC e TLC. In termini di durata, le operazioni di carica più frequenti e precise accelerano l'invecchiamento delle celle di memoria. Pertanto, la resistenza nativa delle flash PLC dovrebbe essere inferiore a quella delle QLC. Per compensare questa debolezza nelle applicazioni pratiche, sono necessarie più misure di compensazione a livello di sistema, come la configurazione di un over-provisioning più elevato, l'adozione di algoritmi di livellamento dell'usura dei dati più aggressivi e l'affidamento alla cache SLC per assorbire i carichi di scrittura a raffica.

Differenze tra le cinque tecnologie di celle di memoria

La tabella seguente mostra chiaramente le differenze nelle metriche chiave tra le cinque tecnologie di celle di memoria NAND Flash, da SLC a PLC.

| Tipo di tecnologia | Bit per cella | Numero di Stati | Costo relativo | Resistenza relativa | Vantaggio principale | Scenari applicativi tipici |

|---|---|---|---|---|---|---|

| SLC | 1 bit | 2 | Il più alto | Il più alto | Velocità elevatissima, durata di vita molto lunga, elevata affidabilità | Cache mission-critical aziendale ad alta velocità |

| MLC | 2 bit | 4 | Alto | Alto | Eccellente equilibrio tra prestazioni e costi | SSD aziendali, SSD consumer di fascia alta |

| TLC | 3 bit | 8 | Medio | Medio | Scelta mainstream per costi e capacità | SSD di largo consumo, dispositivi mobili |

| QLC | 4 bit | 16 | Basso | Relativamente basso | Alta densità di stoccaggio, basso costo | SSD di grande capacità per i consumatori, archiviazione a freddo per i centri dati |

| PLC | 5 bit | 32 | Si prevede che sia basso | Si prevede che sia basso | Massima densità di archiviazione, costo minimo | Archiviazione di dati a freddo su larghissima scala |

Dalla tabella si evince una chiara tendenza: con l'aumento del numero di bit memorizzati per cella, la densità di memorizzazione e l'economicità migliorano continuamente, ma ciò avviene a scapito della velocità di lettura/scrittura e della durata delle celle. Pertanto, le diverse tecnologie sono adatte a scenari distinti. L'SLC serve le aree con i requisiti più severi in termini di prestazioni e affidabilità, mentre l'obiettivo del PLC è quello di fornire una soluzione di memorizzazione altamente economica per i dati freddi e massicci entro limiti accettabili di prestazioni e durata.

Valore, posizionamento e futuro della tecnologia PLC

Il massimo vantaggio in termini di costi e densità. La forza motrice fondamentale dello sviluppo della tecnologia PLC è la ricerca della massima densità di memorizzazione e dell'economicità. Accogliendo 5 bit di dati per cella di memoria, il PLC è in grado di fornire una capacità di memorizzazione superiore a quella del QLC sulla stessa area del wafer del chip. Ciò si traduce direttamente in un costo inferiore per GB. Il suo mercato di riferimento principale è quello di sostituire le aree attualmente dominate dai dischi rigidi meccanici ad alta capacità, offrendo una soluzione di archiviazione dei dati freddi per i data center hyperscale che presenta vantaggi in termini di consumo energetico per unità di volume, velocità di accesso e ingombro fisico.

Gravi sfide da affrontare. La produzione e l'applicazione di massa della tecnologia PLC devono affrontare diverse sfide. In primo luogo, la distinzione di 32 stati di tensione richiede una precisione di controllo senza precedenti, con conseguenti bassi rendimenti di produzione iniziali e un controllo di qualità estremamente complesso. In secondo luogo, per ottenere una memorizzazione affidabile dei dati, il controller deve disporre di potenti capacità di calcolo in tempo reale per eseguire complessi algoritmi di correzione degli errori, aumentando la difficoltà di progettazione e il consumo di energia del chip controller principale. Infine, la resistenza nativa della flash PLC è bassa e deve essere compensata da tecniche a livello di sistema, come l'impostazione di aree di over-provisioning più ampie, l'adozione di meccanismi più efficienti di livellamento dell'usura dei dati e di garbage collection. Tutto ciò aumenta la complessità progettuale della soluzione complessiva.

Posizionamento dello scenario applicativo.Sulla base delle sue caratteristiche tecniche, il posizionamento dello scenario applicativo del PLC è molto chiaro e specifico. È particolarmente adatto a scenari di archiviazione di dati ultrafreddi in cui le operazioni di scrittura sono estremamente rare e la frequenza di accesso in lettura è molto bassa. Tra gli esempi vi sono i livelli di archiviazione profonda nei servizi cloud, i backup dei dati a lungo termine per la conformità alle normative, i file di registro storici e la conservazione di beni digitali come le immagini mediche. Al contrario, il PLC non è assolutamente adatto per attività ad alta intensità di scrittura, come sistemi operativi, database e dati applicativi aggiornati di frequente. Il suo ruolo è quello di essere il livello fondamentale a basso costo e massima capacità nell'ecosistema di archiviazione dei dati.

Prospettive future.L'adozione commerciale della tecnologia PLC si basa non solo sulla maturità dei chip di memoria flash stessi, ma anche sullo sviluppo coordinato dei chip di controllo, degli algoritmi del firmware e persino dell'intero ecosistema del sistema di archiviazione dati. Rappresenta l'esplorazione dei limiti fisici della tecnologia NAND Flash nell'ambito dell'architettura attuale. In generale, l'industria ritiene che il PLC si stia avvicinando al limite pratico del miglioramento della densità a livello di cella basato sul principio della memorizzazione della carica. I progressi futuri si baseranno maggiormente sul continuo aumento degli strati di impilamento 3D e sullo sfruttamento di innovazioni tecnologiche come l'intelligenza artificiale per ottimizzare la gestione dei dati e l'efficienza della correzione degli errori, ottenendo così progressi a livello di sistema in termini di prestazioni e affidabilità.

PLC NAND Flash rappresenta un'importante sfida ai limiti fisici dell'attuale architettura della tecnologia di archiviazione. Si tratta di un'evoluzione naturale guidata dalla continua ricerca di esigenze di archiviazione a costi inferiori e densità più elevate. Sebbene le sue caratteristiche intrinseche ne determinino l'utilizzo principalmente in campi specifici, grazie alla continua ottimizzazione degli algoritmi di controllo e delle soluzioni a livello di sistema, si prevede che la PLC svolgerà un ruolo indispensabile nel futuro ecosistema di archiviazione dei dati, ospitando enormi quantità di dati freddi.