Alors que la mémoire DDR5 vient d'achever sa pénétration initiale sur le marché grand public et continue d'augmenter régulièrement son adoption dans le secteur des serveurs, les discussions sur la mémoire DDR6 ont discrètement commencé à s'intensifier tant à l'intérieur qu'à l'extérieur de l'industrie. Il ne s'agit pas d'un "battage prématuré" dans le domaine technologique, mais d'un résultat inévitable de la demande du marché et de l'évolution technologique. À l'heure actuelle, des domaines tels que l'intelligence artificielle générative, l'informatique à haute performance et l'informatique en nuage connaissent une croissance explosive, ce qui impose des exigences sans précédent en matière de largeur de bande, de capacité et d'efficacité énergétique des mémoires. Selon les prévisions de TrendForce, entre 2024 et 2026, les applications liées à l'intelligence artificielle et aux serveurs représenteront respectivement 46%, 56% et 66% de la demande totale de capacité DRAM, et ce chiffre devrait dépasser 70% en 2027. Même les mémoires DDR5 les plus puissantes deviennent progressivement insuffisantes pour répondre aux exigences de débit de données massives des scénarios de formation à l'IA et de traitement de données à grande échelle.

Parallèlement, sur le marché grand public, les ordinateurs portables de jeu haut de gamme et les stations de travail mobiles continuent à rechercher des fréquences de mémoire plus élevées et des capacités plus importantes, tandis que les appareils minces et légers imposent des limites strictes à la consommation d'énergie de la mémoire et à l'espace physique. Tous ces facteurs accélèrent le développement d'une nouvelle génération de normes de mémoire. Les principaux fabricants mondiaux de mémoire, tels que Samsung, SK hynix et Micron, ont déjà achevé le développement des premiers prototypes des spécifications DDR6 et collaborent avec les fournisseurs de puces, notamment Intel, AMD et NVIDIA, pour faire avancer la validation de la plate-forme.

Évolution de la mémoire DDR

Qu'est-ce que la mémoire DDR et pourquoi la "bande passante" est-elle si importante ?

La mémoire DDR, abréviation de Double Data Rate Synchronous Dynamic Random Access Memory, est le composant central des systèmes informatiques chargé de stocker temporairement les données. Elle sert également de pont de transfert de données entre l'unité centrale et les dispositifs de stockage tels que les disques durs. Son principe de fonctionnement repose sur un signal d'horloge synchrone qui permet de transférer des données à la fois sur les fronts ascendants et descendants de chaque cycle d'horloge. L'efficacité du transfert de données est ainsi doublée à la même fréquence d'horloge, d'où l'expression "double débit de données".

Parmi toutes les mesures de performance de la mémoire DDR, la bande passante est sans aucun doute la plus critique. La largeur de bande de la mémoire correspond à la quantité de données que la mémoire peut transférer par unité de temps. Elle est calculée à l'aide de la formule suivante : bande passante = fréquence de la mémoire × largeur du bus × nombre de canaux ÷ 8. La bande passante détermine directement la vitesse à laquelle l'unité centrale peut accéder aux données. Elle peut être comparée à une "autoroute" pour la transmission de données : plus l'autoroute est large, plus l'efficacité du transfert de données est élevée. Dans les scénarios d'application complexes, tels que l'exécution de grands jeux AAA, l'édition et le rendu vidéo ou l'entraînement de modèles d'intelligence artificielle, l'unité centrale doit lire et écrire en permanence de grandes quantités de données à grande vitesse. Si la bande passante de la mémoire est insuffisante, il se produit un "encombrement des données" qui oblige l'unité centrale à attendre les données pendant de longues périodes. Dans ce cas, même une unité centrale très puissante ne peut pas fonctionner à plein régime, ce qui crée un goulot d'étranglement au niveau des performances du système. C'est pourquoi l'amélioration de la largeur de bande de la mémoire a toujours été l'un des principaux objectifs de l'évolution de chaque génération de la technologie de la mémoire DDR.

De la DDR1 à la DDR5 : les problèmes résolus par chaque génération

De la DDR1 à la DDR5, chaque génération de mémoire a été conçue pour répondre directement aux principaux défis auxquels l'industrie était confrontée à l'époque, en améliorant considérablement les performances grâce à l'innovation technologique. La DDR1, première génération de mémoire DDR, est apparue aux alentours de l'an 2000. Sa principale avancée a été la mise en œuvre d'une transmission à double débit de données, remplaçant la SDRAM traditionnelle et résolvant initialement le problème des vitesses de transfert de mémoire insuffisantes dans les premiers systèmes informatiques. Elle a fourni un support de mémoire compatible avec les premiers processeurs tels que le Pentium 4, avec des débits de données allant de 200 à 400 MT/s.

La mémoire DDR2 a été introduite vers 2004 et s'est principalement attaquée aux limites de la DDR1, notamment sa faible vitesse maximale et sa consommation d'énergie relativement élevée. En améliorant les processus de fabrication des puces mémoire et les technologies de traitement des signaux, la DDR2 a augmenté les débits de données à 533-800 MT/s, tout en réduisant la tension de fonctionnement de 2,5 V dans la DDR1 à 1,8 V. Cela a considérablement réduit la consommation d'énergie et la production de chaleur, ce qui l'a rendue plus adaptée au développement des processeurs multi-cœurs à l'époque.

La mémoire DDR3, apparue en 2007, a encore dépassé les limites de vitesse, en augmentant le débit de données maximal à 1600 MT/s et en réduisant la tension de fonctionnement à 1,5 V, ce qui a permis d'améliorer considérablement l'efficacité énergétique. Plus important encore, la DDR3 a amélioré la stabilité et la compatibilité de la mémoire grâce à une conception optimisée du contrôleur de mémoire. Elle a été largement adoptée par les ordinateurs portables, les ordinateurs de bureau et les serveurs, devenant ainsi l'une des normes de mémoire les plus durables.

La mémoire DDR4, lancée en 2014, a été conçue pour répondre à la double demande de capacité de mémoire et de bande passante à l'ère du big data. Elle a augmenté les débits de données à 2133-3200 MT/s et réduit la tension de fonctionnement à 1,2 V, tout en prenant en charge des capacités beaucoup plus importantes pour un seul module, avec un maximum de 128 Go par module. En introduisant la technologie Bank Group, la DDR4 a amélioré les capacités d'accès simultané à la mémoire et réduit efficacement la pression sur la bande passante dans les scénarios multitâches, devenant ainsi la configuration de mémoire la plus courante pour les systèmes informatiques au cours de la dernière décennie.

La mémoire DDR5, officiellement commercialisée à la fin de l'année 2021, a fait un nouveau bond en avant en termes de vitesse et d'efficacité énergétique pour répondre aux exigences de l'IA et de l'informatique haute performance. Son débit de données maximal atteint 8 000 MT/s, sa tension de fonctionnement est encore réduite à 1,1 V et elle adopte une structure de canaux 2 × 32 bits pour améliorer les capacités de traitement parallèle. La DDR5 a également introduit la correction d'erreur ECC on-die pour la première fois dans les mémoires grand public, améliorant ainsi la stabilité de la transmission des données, avec des capacités de module unique atteignant 256 Go. Cependant, avec la croissance explosive des applications d'intelligence artificielle, les limites de performance de la DDR5 deviennent progressivement apparentes, jetant ainsi les bases du développement de la DDR6.

Qu'est-ce que la DDR6 ?

DDR6 est la norme de mémoire vive dynamique synchrone à double débit de la prochaine génération, dirigée par le JEDEC (Joint Electron Device Engineering Council). Elle est conçue pour répondre aux exigences extrêmes en matière de bande passante, de capacité et d'efficacité énergétique de la mémoire dans des domaines émergents tels que l'intelligence artificielle, l'informatique à haute performance et l'informatique en nuage (cloud computing). Le processus de normalisation de la DDR6 a officiellement débuté en 2024, avec pour objectif principal de dépasser les limites de performance physique de la DDR5 et de créer une plateforme de mémoire offrant une large bande passante, une grande capacité, une grande efficacité énergétique et une grande fiabilité.

Fin 2024, le JEDEC a achevé le principal projet de spécification de la DDR6, jetant ainsi les bases du développement technologique et de la mise en œuvre des produits. Parallèlement, le projet de spécification de la version basse consommation, LPDDR6, a été publié au deuxième trimestre 2025. À l'instar des processus de développement des normes de mémoire précédents, la formulation de la DDR6 rassemble les principaux fabricants de mémoire, concepteurs de puces et vendeurs d'appareils finaux du monde entier. Cela garantit que la norme peut prendre en charge différents scénarios d'application et plates-formes matérielles, tout en favorisant un développement coordonné dans l'ensemble de l'écosystème industriel.

Les trois problèmes fondamentaux que la DDR6 vise à résoudre

Le développement de la DDR6 est axé sur la résolution de trois problèmes fondamentaux auxquels l'industrie est actuellement confrontée : largeur de bande insuffisante, faible efficacité énergétique et limitations architecturales.

Le premier problème est l'insuffisance de la bande passante. Compte tenu de la croissance rapide de la demande en matière de formation à l'intelligence artificielle et de traitement des données à grande échelle, la vitesse maximale actuelle de la DDR5 (8 000 MT/s) est de moins en moins en mesure de répondre aux exigences de transmission à grande vitesse de quantités massives de données, devenant ainsi un goulot d'étranglement majeur qui limite les performances globales du système. La DDR6 améliore l'architecture des canaux et les technologies de transmission pour porter le débit de données initial à 8800 MT/s, et prévoit de l'augmenter à 17 600 MT/s dans les phases ultérieures, afin d'éliminer fondamentalement les goulets d'étranglement de la bande passante dans les scénarios de forte charge.

La deuxième question est celle de l'efficacité énergétique. Dans les serveurs d'IA et les centres de données, les modules de mémoire sont déployés à des densités de plus en plus élevées, ce qui augmente considérablement la consommation d'énergie et la production de chaleur. Cela augmente non seulement les coûts d'exploitation, mais aussi les exigences en matière de systèmes de refroidissement. En réduisant la tension de fonctionnement et en optimisant les mécanismes de gestion de l'énergie, la DDR6 améliore les performances tout en réduisant la consommation d'énergie. La consommation d'énergie typique devrait être réduite de 15-20% par rapport à la DDR5, ce qui rend la DDR6 mieux adaptée aux scénarios de déploiement à haute densité.

Le troisième problème est celui des limites architecturales. La structure de canal 2 × 32 bits utilisée par la DDR5 est sujette à des problèmes d'intégrité du signal à des fréquences élevées. En outre, les facteurs de forme DIMM et SO-DIMM traditionnels souffrent d'un encombrement important et de limitations de fréquence dans les configurations 2DPC. La DDR6 introduit une architecture innovante de sous-canaux 4 × 24 bits et adopte la norme d'interface CAMM2. Cela permet non seulement d'améliorer la capacité de traitement parallèle, mais aussi de résoudre les problèmes d'espace et de fréquence liés à l'emballage traditionnel de la mémoire, en fournissant un support architectural pour le déploiement de la mémoire à haute performance et à haute densité.

Principaux changements techniques de la DDR6

Une avancée majeure dans la vitesse de transfert des données

L'augmentation significative de la vitesse de transfert des données est l'une des avancées technologiques les plus importantes de la DDR6. Selon les feuilles de route actuelles de l'industrie, la DDR6 débutera avec un débit initial de 8800 MT/s, dépassant déjà le maximum actuel de la DDR5 à 8000 MT/s. Tout au long du cycle de vie du produit, les vitesses de la DDR6 devraient encore augmenter pour atteindre 17 600 MT/s, certaines versions surcadencées pouvant même dépasser 21 000 MT/s. Les performances globales devraient être environ deux à trois fois supérieures à celles de la DDR5.

Cette augmentation substantielle de la vitesse n'est pas obtenue simplement en augmentant la fréquence d'horloge. Elle résulte plutôt de l'effet combiné de plusieurs technologies. D'une part, la DDR6 optimise les processus de fabrication des puces de mémoire, améliorant les performances électriques et fournissant une base matérielle pour un fonctionnement à haute fréquence. D'autre part, la DDR6 introduit des conceptions d'optimisation de l'intégrité des signaux plus avancées, notamment des technologies d'emballage améliorées, des règles de routage plus fines et un contrôle plus strict de la synchronisation. Ces mesures réduisent efficacement les interférences et l'atténuation des signaux à haute fréquence. En outre, la DDR6 adopte un mécanisme de préemption à 16n, par rapport à la préemption à 8n utilisée dans la DDR5. Cela améliore encore l'efficacité du transfert de données, en permettant de transmettre plus de données à la même fréquence d'horloge et en réalisant un bond en avant dans la vitesse de transfert globale.

Changements dans l'architecture des sous-canaux

La DDR6 introduit une innovation perturbatrice dans l'architecture des canaux en adoptant une structure de sous-canaux de 4 × 24 bits, qui remplace la conception de canaux de 2 × 32 bits utilisée par la DDR5. L'objectif principal de ce changement d'architecture est d'améliorer la largeur de bande tout en maintenant l'intégrité du signal à des fréquences de fonctionnement élevées. Les bus larges traditionnels ont tendance à souffrir de la diaphonie des signaux lorsque les fréquences augmentent au-delà d'un certain point, ce qui réduit la stabilité de la transmission. En augmentant le nombre de canaux et en réduisant la largeur de chaque canal, la DDR6 augmente la largeur totale du bus de 64 bits dans la DDR5 à 96 bits. Cette approche améliore la capacité de traitement parallèle tout en réduisant la pression de transmission du signal sur chaque canal individuel.

L'architecture à sous-canaux 4 × 24 bits permet une transmission parallèle des données plus efficace, en permettant à chaque sous-canal d'effectuer indépendamment des opérations de lecture et d'écriture. Cela améliore considérablement la concurrence de la mémoire et l'utilisation de la bande passante. Dans des scénarios tels que l'apprentissage de l'IA et le traitement de données à grande échelle, où plusieurs flux de données doivent être traités simultanément, les avantages de cette architecture deviennent particulièrement évidents. Parallèlement, l'architecture à sous-canaux offre une plus grande souplesse pour l'extension de la capacité et l'optimisation de l'efficacité énergétique. Elle permet d'ajuster dynamiquement l'état de fonctionnement de chaque sous-canal en fonction des exigences de l'application, ce qui permet d'atteindre un meilleur équilibre entre les performances et la consommation d'énergie.

Changements dans les facteurs de forme des modules et des interfaces (CAMM2)

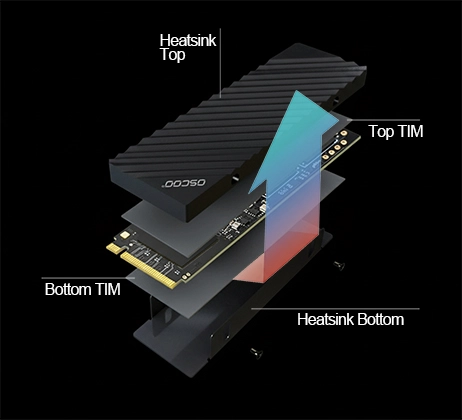

La DDR6 adoptera pleinement la norme d'interface CAMM2, remplaçant les interfaces DIMM et SO-DIMM traditionnelles utilisées depuis de nombreuses années. Cela représente une transformation majeure des facteurs de forme des modules de mémoire. CAMM2 est l'acronyme de Compression Attached Memory Module (module de mémoire attaché à la compression). Elle a été introduite à l'origine par Dell, puis révisée par le JEDEC, et est devenue officiellement une norme du JEDEC à la fin de 2023. Contrairement aux modules de mémoire traditionnels qui se connectent aux fentes par des connecteurs de bord en bas, CAMM2 utilise un connecteur de compression qui se connecte à travers une carte d'adaptateur mince sur la carte mère et est fixé par des vis. Cette nouvelle forme d'interface apporte plusieurs avantages significatifs :

Le CAMM2 résout efficacement les limitations de fréquence que l'on trouve dans les configurations 2DPC traditionnelles. Dans les conceptions 2DPC traditionnelles, l'installation de deux modules de mémoire par canal augmente la complexité électrique et limite la fréquence de la mémoire. CAMM2 déplace la topologie complexe dans le module lui-même, gérant la complexité en interne et permettant à un système d'atteindre à la fois une performance et une capacité maximales.

CAMM2 réduit considérablement la hauteur de l'axe Z et l'utilisation de l'espace global de la carte mère. Comparé au SO-DIMM, le CAMM2 réduit l'épaisseur de 57%, ce qui le rend plus adapté aux appareils ayant des exigences strictes en matière d'épaisseur, tels que les ordinateurs portables et les tablettes fines et légères.

Le connecteur CAMM2 utilise une conception de broches LGA, avec des plots de contact sur la carte mère et le module de mémoire. Cela réduit le risque d'endommagement de l'interface, et le connecteur lui-même peut être remplacé indépendamment, ce qui rend la maintenance plus pratique.

Evolution de l'efficacité énergétique et de la gestion de l'énergie

En termes d'optimisation de l'efficacité énergétique, la DDR6 s'appuie sur les avantages de la DDR5 en matière de faible consommation d'énergie et réalise de nouvelles percées. La tension de fonctionnement standard de la DDR5 est de 1,1 V, tandis que la DDR6 réduira la tension de fonctionnement à 1,0 V, voire moins. Une tension plus faible entraîne directement une réduction de la consommation d'énergie, la consommation d'énergie typique de la DDR6 devant être inférieure de 15-20% à celle de la DDR5. Cette amélioration est particulièrement importante pour les scénarios de déploiement à haute densité tels que les centres de données et les serveurs d'intelligence artificielle, car elle permet de réduire la consommation d'énergie globale et les coûts de refroidissement tout en améliorant l'efficacité énergétique du système.

Outre l'abaissement de la tension de fonctionnement, la DDR6 introduit des mécanismes de gestion de l'énergie plus avancés. En optimisant la logique de gestion de l'énergie du contrôleur de mémoire, la DDR6 peut ajuster dynamiquement l'état de fonctionnement des modules de mémoire en fonction de la charge du système. Dans des conditions de faible charge, la fréquence et la tension de la mémoire sont automatiquement réduites, ce qui permet au système d'entrer dans des modes de faible consommation. Dans des conditions de charge élevée, les performances sont rapidement augmentées pour garantir que les exigences en matière de transmission de données sont respectées. Cette approche de gestion dynamique de l'énergie permet à la DDR6 d'atteindre un équilibre optimal entre les performances et la consommation d'énergie dans différents scénarios d'application, offrant ainsi des performances élevées tout en conservant efficacement l'énergie.

Augmentation de la capacité et potentiel d'empilement

La DDR6 offre un plus grand potentiel d'extension de capacité, ce qui la rend plus apte à répondre aux exigences de grande capacité de mémoire de l'IA et des charges de travail informatiques à haute performance. Les innovations en matière de technologie d'empilage sont un élément clé de l'augmentation de la capacité de la DDR6. La DDR6 adoptera des technologies d'empilage 3D plus avancées, empilant verticalement plus de puces de mémoire pour augmenter de manière significative la densité de capacité par puce. Parallèlement, la conception modulaire de l'interface CAMM2 facilite l'extension de la capacité en prenant en charge les configurations de modules empilés afin d'augmenter la capacité totale de la mémoire du système.

Par exemple, deux modules CAMM2 à canal unique de type D peuvent théoriquement être empilés le long de l'axe Z, ce qui permet à la mémoire totale du système d'atteindre 512 Go. Au fur et à mesure que la technologie évolue, il est possible de réaliser des percées encore plus importantes en termes de capacité. Les modules DDR5 CAMM2 actuellement prévus peuvent atteindre une capacité maximale de 256 Go. Avec des puces de mémoire plus denses et des technologies d'empilage, les modules DDR6 CAMM2 devraient dépasser cette limite.

Comparaison complète entre DDR6 et DDR5

| Catégorie | DDR5 | DDR6 |

|---|---|---|

| Taux de données | Jusqu'à environ 8000 MT/s | Initialement 8800 MT/s, prévu pour augmenter à 17 600 MT/s, les versions surcadencées peuvent dépasser 21 000 MT/s |

| Architecture des canaux | 2 × 32 bits (largeur totale du bus 64 bits) | 4 × 24 bits (largeur totale du bus 96 bits) |

| Interface Facteur de forme | Principalement DIMM, SO-DIMM | Adopte entièrement CAMM2 / LPCAMM2 |

| Tension de fonctionnement | 1.1 V | 1,0 V ou moins |

| Consommation électrique typique | Niveau de référence | 15-20% inférieur à DDR5 |

| Capacité maximale par module | 256 GB (DIMM), 128 GB (SO-DIMM) | On s'attend à ce que la capacité dépasse 256 Go, l'empilage de deux modules pouvant atteindre 512 Go. |

| Mécanisme de recherche préalable (Prefetch) | 8n prefetch | 16n prefetch |

| 2DPC Limitation de fréquence | Limites de fréquence importantes | Complexité gérée au sein du module, pas de limitation de fréquence évidente |

| Principaux scénarios d'application | PC, serveurs et stations de travail de milieu et de haut de gamme (période de transition) | Serveurs d'IA, calcul à haute performance, stations de travail haut de gamme, PC phares |

Compatibilité de la DDR6

Il n'y a pas de compatibilité ascendante entre la DDR6 et la DDR5. Cela signifie que les cartes mères conçues pour la DDR5 ne peuvent pas utiliser directement la mémoire DDR6, et vice versa. La raison principale réside dans les différences fondamentales d'architecture, de facteurs de forme d'interface et de spécifications électriques.

Tout d'abord, il y a une différence dans le facteur de forme de l'interface. La DDR6 adopte entièrement l'interface CAMM2, tandis que la DDR5 utilise principalement les interfaces DIMM et SO-DIMM traditionnelles. Leurs dimensions physiques et leurs méthodes de connexion sont complètement différentes, ce qui les rend incompatibles les unes avec les autres.

Deuxièmement, il existe des différences dans les spécifications électriques. La DDR6 réduit la tension de fonctionnement à 1,0 V, voire moins, contre 1,1 V pour la DDR5. En outre, les définitions des signaux et les paramètres de synchronisation sont totalement différents. Les contrôleurs de mémoire doivent être conçus en tenant compte de spécifications électriques spécifiques afin de piloter les circuits et de traiter les signaux correctement. Un contrôleur de mémoire DDR5 ne peut pas répondre aux exigences électriques de la DDR6, et son utilisation forcée endommagerait le dispositif ou empêcherait son bon fonctionnement.

Enfin, il existe des différences dans l'architecture des canaux. La norme DDR6 utilise une architecture de sous-canaux de 4 × 24 bits, ce qui est fondamentalement différent de l'architecture de 2 × 32 bits utilisée par la norme DDR5. La logique de conception du contrôleur de mémoire est complètement différente dans les deux cas, ce qui détermine en fin de compte l'incompatibilité des deux normes. Par conséquent, le déploiement de la DDR6 nécessite un soutien coordonné de la part des CPU, des cartes mères et de l'ensemble de l'écosystème industriel pour former un système de soutien matériel complet. Actuellement, les fabricants de mémoire tels que Samsung, SK hynix et Micron travaillent en étroite collaboration avec les fournisseurs de puces, notamment Intel, AMD et NVIDIA, pour faire progresser conjointement la validation de la plateforme DDR6 et accélérer le développement de l'écosystème.

Analyse du scénario d'application de la DDR6

Centres de données et informatique en nuage

Les centres de données et l'informatique en nuage font partie des scénarios d'application les plus importants pour la DDR6. Actuellement, les services d'informatique en nuage évoluent vers une grande échelle, une forte concurrence et une faible latence. Les centres de données doivent gérer un nombre massif de demandes d'utilisateurs et de tâches de transfert de données, ce qui impose des exigences extrêmement élevées en matière de bande passante et de capacité de mémoire. La DDR6 peut augmenter de manière significative la bande passante de la mémoire dans les serveurs des centres de données, accélérant le traitement et la transmission des données tout en réduisant la latence des réponses aux demandes des utilisateurs.

En même temps, l'efficacité énergétique élevée de la DDR6 est bien adaptée aux exigences des centres de données. Les centres de données fonctionnent avec une densité de serveurs élevée et les modules de mémoire représentent une part importante de la consommation d'énergie totale du système. Par rapport à la DDR5, la DDR6 réduit la consommation d'énergie de 15-20%, ce qui permet de réduire efficacement la consommation d'énergie globale et les coûts de refroidissement dans les centres de données tout en améliorant l'efficacité opérationnelle. En outre, la DDR6 prend en charge l'expansion à grande capacité, répondant ainsi aux besoins de mise en cache de données à grande échelle et de traitement parallèle dans les environnements d'informatique en nuage. Cela permet une meilleure prise en charge de la mémoire pour des services tels que les bases de données en nuage, le stockage en nuage et le rendu en nuage. Avec l'adoption commerciale de la DDR6, les capacités informatiques et de traitement des données des centres de données devraient faire un bond qualitatif.

IA et calcul à haute performance (HPC)

L'IA et le calcul à haute performance sont les principaux moteurs du développement et de l'adoption de la DDR6, et ce sont également les scénarios d'application où la DDR6 peut offrir les plus grands avantages. Dans les scénarios d'apprentissage de l'IA, la taille des paramètres des modèles ne cesse d'augmenter, ce qui nécessite le traitement de quantités massives de données d'apprentissage. La bande passante et la capacité de la mémoire sont donc extrêmement sollicitées. Les caractéristiques de bande passante élevée de la DDR6 garantissent que les CPU et les GPU peuvent lire et écrire rapidement les données d'entraînement pendant le processus d'entraînement, en évitant les goulets d'étranglement du transfert de données et en améliorant de manière significative l'efficacité de l'entraînement.

Dans le domaine du calcul à haute performance, tel que les prévisions météorologiques, les simulations astrophysiques et la recherche pharmaceutique, les systèmes doivent effectuer de grands volumes de calculs complexes et de traitement de données. Ces charges de travail exigent des niveaux extrêmement élevés de capacité de traitement parallèle et de stabilité de la mémoire. L'architecture à sous-canaux 4 × 24 bits de la DDR6 améliore le traitement parallèle des données, tandis que le mécanisme de préemption 16n et les mécanismes avancés de correction des erreurs garantissent à la fois l'efficacité et la stabilité de la transmission des données. En outre, les avantages de la DDR6 en matière de faible consommation d'énergie permettent de réduire la consommation d'énergie dans les grappes de calcul à haute performance, améliorant ainsi leur capacité à fonctionner en continu sur de longues périodes. À mesure que l'IA et l'informatique à haute performance continuent de se développer, la DDR6 deviendra une configuration de mémoire essentielle dans ces domaines.

PC grand public et stations de travail haut de gamme

Même si la DDR6 sera d'abord déployée commercialement dans les serveurs et les domaines liés à l'IA, elle devrait progressivement pénétrer les marchés des PC grand public et des stations de travail haut de gamme à mesure que l'écosystème arrive à maturité et que les coûts diminuent. Pour les ordinateurs portables de jeu haut de gamme et les ordinateurs de bureau phares, la haute fréquence et la large bande passante de la DDR6 peuvent améliorer les temps de chargement des jeux et la fluidité générale. Cela est particulièrement visible lors de l'exécution de grands jeux AAA, où la DDR6 peut réduire efficacement les bégaiements et les chutes d'images. Dans le même temps, la conception fine permise par l'interface CAMM2 aide les fabricants à créer des ordinateurs portables de jeu plus minces et plus légers avec des performances élevées.

Les stations de travail haut de gamme seront également parmi les premiers segments de consommateurs à adopter la DDR6. Les stations de travail mobiles et les stations de travail graphiques sont principalement utilisées pour des charges de travail professionnelles telles que le montage vidéo, la modélisation 3D et le rendu d'animation, qui imposent des exigences très élevées en matière de fréquence, de capacité et de stabilité de la mémoire. La mémoire SO-DIMM traditionnelle souffre de limitations de fréquence dans les configurations 2DPC et ne peut pas répondre aux exigences de performance des stations de travail haut de gamme. La DDR6 combinée à l'interface CAMM2 résout ce problème tout en offrant une plus grande capacité.

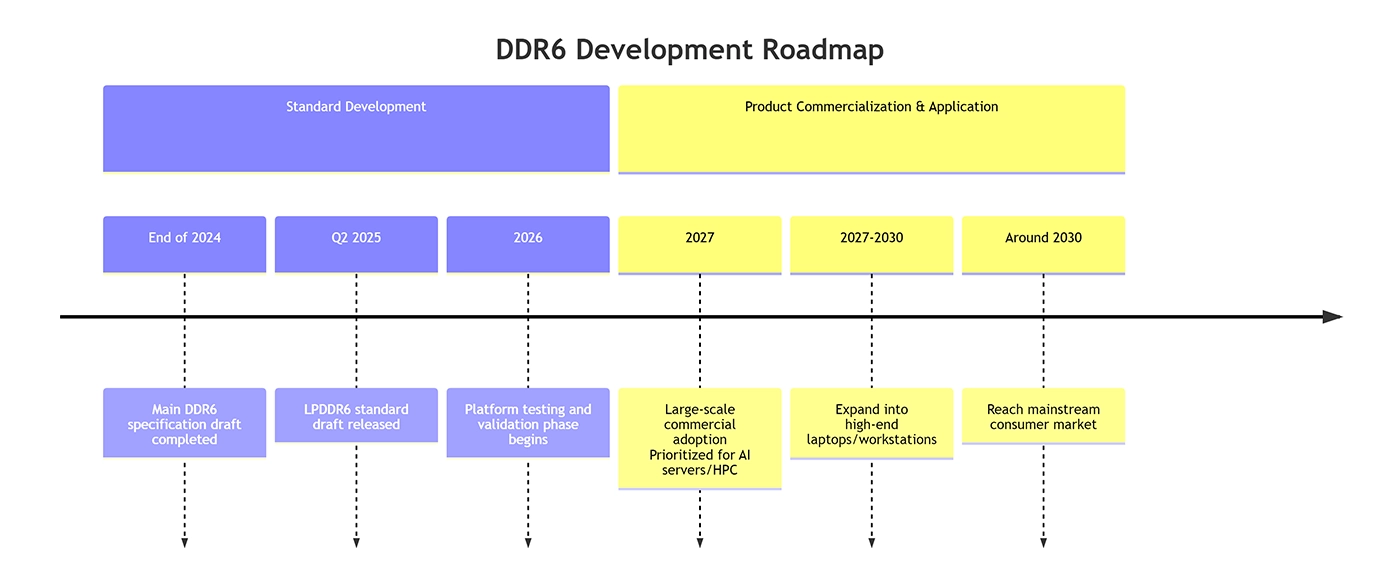

Progrès de la normalisation et calendrier de la commercialisation

L'organisation responsable de l'élaboration des normes en matière de technologie de mémoire, le JEDEC, a achevé le projet de la principale spécification DDR6 à la fin de l'année 2024. Le projet de norme pour la LPDDR6, destinée aux appareils mobiles, a également été publié au deuxième trimestre 2025. La prochaine étape sera la phase critique de test et de validation de la plateforme, qui devrait avoir lieu en 2026. Les fabricants de puces tels qu'Intel et AMD y participeront afin de garantir la compatibilité entre la DDR6 et les futures plateformes de processeurs.

Selon les prévisions de l'industrie, la DDR6 devrait commencer à être déployée commercialement à grande échelle vers 2027. Sa trajectoire d'adoption devrait suivre un modèle de haut en bas vers le courant dominant. Elle sera d'abord utilisée dans des domaines extrêmement sensibles à la performance mais moins sensibles au coût, tels que les serveurs d'IA, les systèmes informatiques à haute performance et les centres de données. Il s'étendra ensuite progressivement aux marchés des ordinateurs portables haut de gamme et des stations de travail. Les utilisateurs d'ordinateurs de bureau et d'ordinateurs portables ordinaires ne rencontreront peut-être pas la DDR6 avant 2030 environ.

DDR6 n'est pas une simple itération, mais une évolution architecturale conçue pour relever des défis fondamentaux. Son objectif principal est d'éliminer les goulets d'étranglement actuels en matière de largeur de bande de mémoire et d'efficacité énergétique, en fournissant une infrastructure essentielle pour l'intelligence artificielle, l'informatique à haute performance et le traitement futur de données à grande échelle. Le passage de la DDR1 à la DDR5 témoigne d'une évolution constante de la technologie de la mémoire pour répondre aux exigences de l'informatique. La DDR6 représente le prochain chapitre de cette progression. Elle a pour mission de repousser les limites de l'informatique, et sa forme finale ainsi que son adoption généralisée auront un impact profond sur la trajectoire du développement technologique au cours de la prochaine décennie.