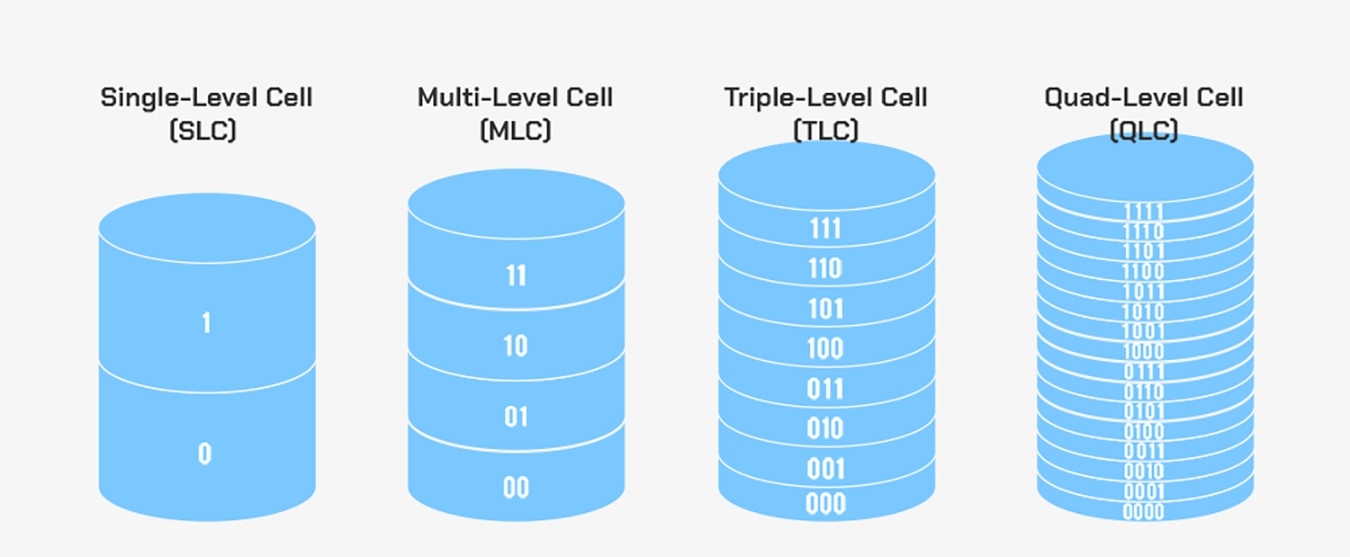

Nous sommes à l'ère de l'explosion du volume de données. La formation à l'IA, les opérations de services cloud, l'archivage vidéo haute définition et la demande de remplacement des disques durs mécaniques traditionnels sont autant d'éléments qui suscitent un désir presque illimité de capacité de stockage. Cependant, la miniaturisation des processus de fabrication des semi-conducteurs se rapproche progressivement des limites physiques, ce qui rend cruciale la réduction du coût par Go par l'augmentation de la densité de stockage. Sur la voie de l'évolution technologique, du SLC stockant 1 bit par cellule, au MLC avec 2 bits, au TLC avec 3 bits et au QLC avec 4 bits, chaque étape représente un nouvel équilibre entre le coût et la fiabilité. Aujourd'hui, la technologie PLC (Penta-Level Cell), qui stocke 5 bits de données par cellule, est considérée comme un axe de développement essentiel pour le stockage haute densité de la prochaine génération.

Principes de base de la NAND Flash : comment la charge stocke les données

Flash NAND est un type de mémoire non volatile, ce qui signifie qu'elle peut conserver des données pendant une longue période, même après une coupure de courant. Sa fonctionnalité principale repose sur un contrôle précis de la quantité de charge à l'intérieur de chaque cellule de mémoire. La cellule de mémoire la plus élémentaire peut être considérée comme un transistor spécial doté d'une couche isolante appelée "grille flottante" ou d'une "couche de piégeage de charge" fonctionnelle similaire. L'aspect unique de cette couche est que les électrons injectés sont effectivement isolés, ce qui leur permet d'être stockés pendant une longue période, permettant ainsi un stockage persistant des données.

Principe d'enregistrement des donnéesLa méthode spécifique d'enregistrement des données est caractérisée par la "tension de seuil". La tension de seuil est la tension minimale requise pour activer le transistor. En injectant différentes quantités d'électrons dans la grille flottante, les caractéristiques électriques du transistor sont modifiées, ce qui change sa tension de seuil. Le contrôleur applique une tension de référence et détecte si le transistor s'allume, déterminant ainsi l'état actuel de la tension de seuil de la cellule. Chaque état de tension spécifique correspond à un codage de données unique. L'essence de la technologie des "cellules multi-niveaux" est de définir et de distinguer avec précision plus de deux états de tension de seuil au sein d'une seule cellule, ce qui permet de stocker plus d'un bit de données.

Écriture, lecture et effacementSur la base de ces principes, les opérations sur la NAND Flash sont principalement divisées en trois types : l'écriture, la lecture et l'effacement. L'opération d'écriture, également appelée programmation, est réalisée en injectant une charge dans la porte flottante de la cellule. L'opération d'effacement supprime la charge de la porte flottante, ce qui ramène la cellule à son état initial. Il est particulièrement important de noter que la plus petite unité d'effacement pour la NAND Flash est le "bloc", alors que la programmation et la lecture peuvent être effectuées sur la plus petite unité "page". Lors d'une opération de lecture, le contrôleur applique une série de tensions de référence précises à la cellule. En détectant si le transistor s'allume à différentes tensions, il détermine la tension de seuil correspondant à la charge actuellement stockée, ce qui permet de décoder les données stockées.

L'essor de la technologie 3D NANDAlors que les processus de fabrication continuent de se réduire, la Flash NAND planaire s'est heurtée à des goulets d'étranglement physiques et à des problèmes de fiabilité lors de la poursuite de la réduction de la taille. Pour continuer à augmenter la capacité, l'industrie s'est tournée vers la technologie d'empilement tridimensionnel, connue sous le nom de 3D NAND. La technologie 3D NAND empile les cellules de mémoire verticalement, comme pour la construction d'un gratte-ciel, ce qui permet de multiplier la densité de stockage sur la même surface plane. Toutefois, au-delà de l'empilement tridimensionnel, l'augmentation du nombre de bits stockés par cellule de mémoire reste une autre voie technologique fondamentale pour améliorer encore la densité de stockage et réduire les coûts.

Évolution de la technologie de stockage : Du SLC au QLC

L'objectif principal de l'évolution de la technologie de stockage est d'augmenter continuellement la densité de stockage afin de réduire le coût par gigaoctet. Cet objectif est principalement atteint en augmentant le nombre de bits stockés par cellule de mémoire. Les paragraphes suivants décrivent l'évolution technologique du SLC au QLC.

SLC : la référence en matière de performances et de fiabilité

SLC est l'abréviation de Single-Level Cell (cellule à niveau unique), qui stocke un bit de données par cellule. Ce bit de données correspond à deux états de charge, généralement représentés par 0 et 1. Étant donné que seuls deux états doivent être distingués, les SLC offrent des vitesses de lecture et d'écriture extrêmement élevées, la plus longue durée de vie et la plus grande fiabilité des données. Son inconvénient est que la densité de stockage est la plus faible, ce qui se traduit par le coût le plus élevé par gigaoctet. C'est pourquoi le SLC est principalement utilisé dans les serveurs d'entreprise et dans les secteurs industriels où les performances et la fiabilité sont primordiales.

MLC : le point d'équilibre entre performance et coût

MLC est l'abréviation de Multi-Level Cell (cellule multiniveau), qui stocke 2 bits de données par cellule, ce qui correspond à quatre états de charge. En stockant davantage de données dans chaque cellule, la MLC permet de doubler la capacité de stockage de la SLC sur la même surface de puce, ce qui réduit considérablement les coûts. Bien que ses performances, sa durée de vie et sa fiabilité ne soient pas aussi élevées que celles des SLC, elles atteignent un bon équilibre. La technologie MLC a longtemps été le choix le plus courant pour les disques durs à semi-conducteurs haut de gamme destinés au grand public et pour le stockage en entreprise.

TLC : Le choix du grand public pour le marché de la consommation

TLC est l'abréviation de Triple-Level Cell, qui stocke 3 bits de données par cellule, ce qui correspond à huit états de charge. Le TLC accroît encore les avantages de la densité de stockage et de la réduction des coûts, devenant ainsi la norme absolue sur le marché actuel des disques SSD grand public. Grâce à des algorithmes de contrôle avancés et à des technologies de correction des erreurs, son endurance répond déjà aux besoins de la grande majorité des applications quotidiennes.

QLC : La pratique du stockage à haute densité

QLC signifie Quad-Level Cell (cellule à quatre niveaux) et stocke 4 bits de données par cellule, ce qui correspond à seize états de charge. L'avantage du QLC réside dans sa densité de stockage élevée et son coût réduit, ce qui le rend très adapté à la construction de disques durs à semi-conducteurs de grande capacité. Cependant, ses inconvénients sont également plus évidents, notamment des vitesses d'écriture plus lentes et une durée de vie plus courte que celle du TLC. Actuellement, le QLC est principalement utilisé dans des scénarios où les exigences en matière de performances d'écriture sont faibles, comme le stockage externe de grande capacité et le stockage de données froides dans les centres de données.

Les principaux défis à l'origine de l'évolution

L'évolution du SLC vers le QLC n'est pas une simple addition linéaire. À mesure que le nombre de bits par cellule augmente, le nombre d'états de tension qui doivent être distingués avec précision croît de manière exponentielle, de 2 à 16. Cela signifie que la fenêtre de tension utilisée pour distinguer les différents états est comprimée de manière extrêmement étroite, ce qui rend les exigences en matière de précision du contrôle de charge, de capacité anti-interférence du signal et de technologie de correction d'erreur extrêmement strictes. Le développement de la technologie PLC est la prochaine étape qui permettra de relever directement ce défi majeur.

La technologie PLC

Le PLC (Penta-Level Cell) est la prochaine étape de l'évolution de la technologie NAND Flash. Sa principale caractéristique est de porter la densité de stockage à de nouveaux sommets, mais elle est également confrontée à des défis techniques sans précédent.

Définition technique de l'automate

PLC signifie Penta-Level Cell, c'est-à-dire que chaque cellule de mémoire stocke 5 bits de données. Ces 5 bits correspondent à 32 états de tension de seuil différents. Par rapport aux 16 états de la QLC, la PLC doit définir avec précision deux fois plus de niveaux de tension dans la même fenêtre de tension physique. Actuellement, cette technologie en est encore au stade du développement et de la vérification. Des fabricants de premier plan, comme Solidigm, ont d'abord présenté des prototypes de produits, ce qui laisse présager l'orientation future du stockage à haute densité.

Défi principal : fenêtre de tension étroite

Le défi fondamental auquel est confrontée la technologie PLC se situe au niveau physique. Pour distinguer 32 états de tension, la différence de tension entre chaque état adjacent doit être comprimée à une valeur très faible. La fenêtre de tension est donc extrêmement étroite et la tolérance d'erreur diminue fortement. La moindre fluctuation de charge, la moindre variation des caractéristiques du transistor ou le moindre bruit électronique pendant la lecture peuvent amener le contrôleur à mal évaluer l'état de tension, ce qui entraîne des erreurs de données. On peut dire que la limite de faisabilité du PLC dépend directement de la possibilité de surmonter efficacement ce problème de rapport signal/bruit.

Progrès en matière d'ingénierie

Face à des taux d'erreurs binaires natifs extrêmement élevés, la praticabilité du PLC dépend fortement des avancées significatives dans les contrôleurs de stockage et la technologie de correction d'erreurs. Les codes de correction d'erreur traditionnels ne peuvent plus répondre aux exigences ; il faut adopter des codes de contrôle de parité à faible densité plus puissants combinés à une technologie de décodage à décision souple. Le décodage à décision souple ne se contente pas de juger le signal comme étant 0 ou 1, mais déduit la valeur la plus probable des données par des calculs de probabilité, ce qui améliore considérablement la capacité de correction des erreurs. En outre, le contrôleur doit disposer de mécanismes intelligents de reprise de lecture. Lorsque la lecture initiale échoue, il peut ajuster dynamiquement la tension de référence pour plusieurs lectures afin de trouver le point de signal correct. Ces processus algorithmiques complexes sollicitent fortement la puissance de calcul du contrôleur.

Impact sur les performances et la durée de vie

Les caractéristiques de la technologie PLC ont également une incidence directe sur ses performances et sa fiabilité. Étant donné qu'un contrôle plus fin de l'injection de charge est nécessaire pour faire correspondre 32 états de tension, le processus d'écriture nécessite davantage de cycles de programmation et de vérification, ce qui entraîne des vitesses d'écriture nettement inférieures à celles des technologies QLC et TLC. En termes de durée de vie, des opérations de charge plus fréquentes et plus précises accélèrent le vieillissement des cellules de mémoire. Par conséquent, l'endurance native de la mémoire flash PLC devrait être inférieure à celle de la mémoire QLC. Pour compenser cette faiblesse dans les applications pratiques, d'autres mesures de compensation sont nécessaires au niveau du système, telles que la configuration d'un surprovisionnement plus élevé, l'adoption d'algorithmes de nivellement de l'usure des données plus agressifs et le recours à la mise en cache SLC pour absorber les charges d'écriture en rafale.

Différences entre les cinq technologies de cellules à mémoire

Le tableau ci-dessous montre clairement les différences entre les cinq technologies de cellules de mémoire NAND Flash, de SLC à PLC, en ce qui concerne les paramètres clés.

| Type de technologie | Bits par cellule | Nombre d'États | Coût relatif | Endurance relative | Principal avantage | Scénarios d'application typiques |

|---|---|---|---|---|---|---|

| CSL | 1 bit | 2 | Le plus élevé | Le plus élevé | Très grande vitesse, très longue durée de vie, grande fiabilité | Cache à haute vitesse, critique pour la mission de l'entreprise |

| MLC | 2 bits | 4 | Haut | Haut | Excellent équilibre entre performance et coût | SSD d'entreprise, SSD grand public haut de gamme |

| TLC | 3 bits | 8 | Moyen | Moyen | Choix du grand public pour le coût et la capacité | SSD grand public, appareils mobiles |

| QLC | 4 bits | 16 | Faible | Relativement faible | Haute densité de stockage, faible coût | SSD grand public de grande capacité, stockage à froid dans les centres de données |

| PLC | 5 bits | 32 | Prévu pour être faible | Prévu pour être faible | Densité de stockage maximale, coût le plus bas | Archivage de données froides à très grande échelle |

Le tableau fait apparaître une tendance claire : à mesure que le nombre de bits stockés par cellule augmente, la densité de stockage et la rentabilité s'améliorent continuellement, mais au détriment de la vitesse de lecture/écriture et de la durée de vie des cellules. C'est pourquoi les différentes technologies sont adaptées à des scénarios nettement différents. Le SLC est utilisé dans les domaines où les exigences de performance et de fiabilité sont les plus strictes, tandis que l'objectif du PLC est de fournir une solution de stockage très rentable pour les données froides massives, dans des limites de performance et de durée de vie acceptables.

Valeur, positionnement et avenir de la technologie PLC

Avantage ultime en termes de coût et de densité. La force motrice fondamentale qui sous-tend le développement de la technologie PLC est la recherche d'une densité de stockage ultime et d'un bon rapport coût-efficacité. En accueillant 5 bits de données par cellule de mémoire, le CPL peut offrir une capacité de stockage supérieure à celle du QLC sur la même surface de plaquette. Cela se traduit directement par un coût inférieur par gigaoctet. Son marché cible principal est de remplacer les zones actuellement dominées par les disques durs mécaniques de grande capacité, en offrant une solution de stockage de données froides pour les centres de données à grande échelle qui présente des avantages en termes de consommation d'énergie par unité de volume, de vitesse d'accès et d'encombrement physique.

Des défis importants à relever. La production de masse et l'application de la technologie PLC sont confrontées à de nombreux défis importants. Tout d'abord, la distinction de 32 états de tension exige une précision de contrôle sans précédent, ce qui entraîne de faibles rendements de production initiaux et un contrôle de qualité extrêmement complexe. Ensuite, pour assurer un stockage fiable des données, le contrôleur doit disposer de puissantes capacités de calcul en temps réel pour exécuter des algorithmes complexes de correction d'erreurs, ce qui accroît la difficulté de conception et la consommation d'énergie de la puce du contrôleur principal. Enfin, l'endurance native de la flash PLC est faible et doit être compensée par des techniques au niveau du système, telles que l'établissement de zones de surprovisionnement plus grandes, l'adoption de données plus efficaces, l'utilisation d'un système de gestion de l'information et l'utilisation d'un système de gestion de l'information. nivellement de l'usure et les mécanismes de collecte des déchets. Tous ces éléments augmentent la complexité de la conception de la solution globale.

Positionnement du scénario d'application.Sur la base de ses caractéristiques techniques, le positionnement du scénario d'application de l'automate est très clair et spécifique. Il convient parfaitement aux scénarios d'archivage de données ultra-froides dans lesquels les opérations d'écriture sont extrêmement rares et la fréquence d'accès en lecture très faible. Les exemples incluent les niveaux de stockage d'archives profondes dans les services en nuage, les sauvegardes de données à long terme pour la conformité réglementaire, les fichiers journaux historiques et la préservation des actifs numériques tels que les images médicales. À l'inverse, le CPL est totalement inadapté aux tâches à forte intensité d'écriture telles que les systèmes d'exploitation, les bases de données et les données d'application fréquemment mises à jour. Son rôle est d'être le niveau de base le moins coûteux et le plus performant de l'écosystème de stockage des données.

Perspectives d'avenir.L'adoption commerciale de la technologie PLC dépend non seulement de la maturité des puces de mémoire flash elles-mêmes, mais aussi du développement coordonné de puces de contrôle, d'algorithmes de microprogrammes et même de l'ensemble de l'écosystème du système de stockage de données. Elle représente l'exploration des limites physiques de la technologie NAND Flash dans le cadre de l'architecture actuelle. L'industrie estime généralement que le PLC pourrait approcher la limite pratique de l'amélioration de la densité au niveau de la cellule sur la base du principe de stockage de la charge. Les progrès futurs dépendront davantage de l'augmentation continue des couches d'empilement 3D et de l'exploitation d'innovations technologiques telles que l'intelligence artificielle pour optimiser la gestion des données et l'efficacité de la correction des erreurs, ce qui permettra de réaliser des percées au niveau du système en termes de performance et de fiabilité.

Le PLC NAND Flash représente un défi important pour les limites physiques de l'architecture actuelle de la technologie de stockage. Il s'agit d'une évolution naturelle motivée par la recherche constante de besoins de stockage à moindre coût et à plus haute densité. Bien que ses caractéristiques inhérentes déterminent qu'il servira principalement des domaines spécifiques, grâce à l'optimisation continue des algorithmes de contrôle et des solutions au niveau du système, le CPL devrait jouer un rôle indispensable dans le futur écosystème de stockage de données en accueillant des quantités massives de données froides.