Mientras la memoria DDR5 acaba de completar su penetración inicial en el mercado de consumo y sigue aumentando su adopción en el sector de los servidores, los debates sobre la DDR6 han empezado a calentarse silenciosamente tanto dentro como fuera de la industria. No se trata de un "bombo excesivamente prematuro" en el campo tecnológico, sino de un resultado inevitable de la demanda del mercado y la evolución tecnológica. En la actualidad, campos como la inteligencia artificial generativa, la computación de alto rendimiento y la computación en nube están experimentando un crecimiento explosivo, lo que impone requisitos estrictos sin precedentes en cuanto a ancho de banda, capacidad y eficiencia energética de la memoria. Según las previsiones de TrendForce, de 2024 a 2026, las aplicaciones relacionadas con la IA y los servidores representarán 46%, 56% y 66% de la demanda total de capacidad DRAM, respectivamente, y se espera que esta cifra supere las 70% en 2027. Incluso las memorias DDR5 más potentes de la actualidad se están volviendo gradualmente insuficientes para satisfacer los requisitos de rendimiento masivo de datos del entrenamiento de IA y los escenarios de procesamiento de datos a gran escala.

Al mismo tiempo, en el mercado de consumo, los portátiles de gama alta para juegos y las estaciones de trabajo móviles siguen buscando frecuencias de memoria más altas y mayores capacidades, mientras que los dispositivos delgados y ligeros imponen estrictas limitaciones al consumo de energía de la memoria y al espacio físico. Todos estos factores están acelerando el desarrollo de una nueva generación de estándares de memoria. Los principales fabricantes de memoria del mundo, como Samsung, SK hynix y Micron, ya han completado el desarrollo de los primeros prototipos de las especificaciones DDR6 y colaboran con fabricantes de chips como Intel, AMD y NVIDIA para avanzar en la validación de las plataformas.

Cómo ha evolucionado la memoria DDR

¿Qué es la memoria DDR y por qué es tan importante el "ancho de banda"?

La memoria DDR, abreviatura de Double Data Rate Synchronous Dynamic Random Access Memory, es el componente central de los sistemas informáticos responsable del almacenamiento temporal de datos. También sirve como puente de transferencia de datos entre la CPU y los dispositivos de almacenamiento, como los discos duros. Su principio básico de funcionamiento se basa en una señal de reloj síncrona que permite transferir datos tanto en el flanco ascendente como en el descendente de cada ciclo de reloj. Como resultado, la eficacia de la transferencia de datos se duplica a la misma frecuencia de reloj, de donde procede el término "doble velocidad de datos".

Entre todas las métricas de rendimiento de la memoria DDR, el ancho de banda es sin duda la más crítica. El ancho de banda de la memoria se refiere a la cantidad de datos que la memoria puede transferir por unidad de tiempo. Se calcula mediante la fórmula: ancho de banda = frecuencia de memoria × ancho de bus × número de canales ÷ 8. El ancho de banda determina directamente la velocidad a la que la CPU puede acceder a los datos. Se puede comparar con una "autopista" para la transmisión de datos: cuanto más ancha sea la autopista, mayor será la eficiencia de la transferencia de datos. En escenarios de aplicaciones complejas, como la ejecución de grandes juegos AAA, la edición y renderización de vídeo o el entrenamiento de modelos de inteligencia artificial, la CPU necesita leer y escribir continuamente grandes cantidades de datos a gran velocidad. Si el ancho de banda de la memoria es insuficiente, se produce una "congestión de datos" que obliga a la CPU a esperar los datos durante largos periodos. En estos casos, ni siquiera una CPU muy potente puede rendir al máximo, lo que crea un cuello de botella en el rendimiento del sistema. Por eso, mejorar el ancho de banda de la memoria ha sido siempre uno de los objetivos centrales en la evolución de cada generación de tecnología de memoria DDR.

De la DDR1 a la DDR5: qué problemas resolvió cada generación

Desde la DDR1 hasta la DDR5, cada generación de memoria se diseñó para abordar directamente los principales retos a los que se enfrentaba el sector en ese momento, logrando importantes mejoras de rendimiento gracias a la innovación tecnológica. DDR1, la primera generación de memoria DDR, surgió en torno al año 2000. Su principal avance fue la implementación de la doble velocidad de transmisión de datos, que sustituyó a la tradicional SDRAM y resolvió inicialmente el problema de la insuficiente velocidad de transferencia de memoria en los primeros sistemas informáticos. Proporcionaba soporte de memoria compatible para los primeros procesadores, como el Pentium 4, con velocidades de transmisión de datos que oscilaban entre 200 y 400 MT/s.

La memoria DDR2 se introdujo alrededor de 2004 y abordaba principalmente las limitaciones de la DDR1, entre ellas su baja velocidad máxima y un consumo de energía relativamente alto. Gracias a la mejora de los procesos de fabricación de chips de memoria y de las tecnologías de procesamiento de señales, la DDR2 aumentó la velocidad de transmisión de datos a 533-800 MT/s, al tiempo que reducía el voltaje de funcionamiento de los 2,5 V de la DDR1 a 1,8 V. De este modo se redujo considerablemente el consumo de energía y la generación de calor, lo que la hizo más adecuada para el desarrollo de los procesadores multinúcleo de la época.

La memoria DDR3, que apareció en 2007, superó aún más las limitaciones de velocidad, aumentando la velocidad máxima de datos a 1600 MT/s y reduciendo el voltaje de funcionamiento a 1,5 V, lo que supuso una importante mejora de la eficiencia energética. Y lo que es más importante, la DDR3 mejoró la estabilidad y compatibilidad de la memoria gracias a un diseño optimizado del controlador de memoria. Se adoptó de forma generalizada en portátiles, ordenadores de sobremesa y servidores, convirtiéndose en uno de los estándares de memoria más duraderos.

La memoria DDR4, lanzada en 2014, se diseñó para satisfacer la doble demanda de capacidad de memoria y ancho de banda en la era de los macrodatos. Aumentó la velocidad de transmisión de datos a 2133-3200 MT/s y redujo la tensión de funcionamiento a 1,2 V, al tiempo que permitía capacidades mucho mayores en un solo módulo, con un máximo de hasta 128 GB por módulo. Al introducir la tecnología Bank Group, la DDR4 mejoró las capacidades de acceso concurrente a la memoria y redujo eficazmente la presión sobre el ancho de banda en escenarios multitarea, convirtiéndose en la configuración de memoria dominante en los sistemas informáticos de la última década.

La memoria DDR5, comercializada oficialmente a finales de 2021, logró otro gran salto en velocidad y eficiencia energética para satisfacer los primeros requisitos de la IA y la informática de alto rendimiento. Su velocidad máxima de transmisión de datos alcanza los 8.000 MT/s, la tensión de funcionamiento se reduce a 1,1 V y adopta una estructura de canales de 2 × 32 bits para mejorar la capacidad de procesamiento en paralelo. La DDR5 también introdujo la corrección de errores ECC en el chip por primera vez en las memorias de consumo, lo que mejoró la estabilidad de la transmisión de datos, con capacidades de un solo módulo de hasta 256 GB. Sin embargo, a medida que las aplicaciones de IA siguen creciendo de forma explosiva, los límites de rendimiento de la DDR5 se van haciendo patentes, lo que sienta las bases para el desarrollo de la DDR6.

Qué es la DDR6

DDR6 es el estándar de memoria dinámica de acceso aleatorio síncrona de doble velocidad de datos de próxima generación liderado por el JEDEC (Consejo Conjunto de Ingeniería de Dispositivos Electrónicos). Está diseñada para responder a las demandas extremas de ancho de banda de memoria, capacidad y eficiencia energética impulsadas por campos emergentes como la inteligencia artificial, la informática de alto rendimiento y la computación en la nube. El proceso de estandarización de la DDR6 comenzó oficialmente en 2024, con el objetivo principal de superar los límites de rendimiento físico de la DDR5 y crear una plataforma de memoria que ofrezca un gran ancho de banda, una gran capacidad, una alta eficiencia energética y una gran fiabilidad.

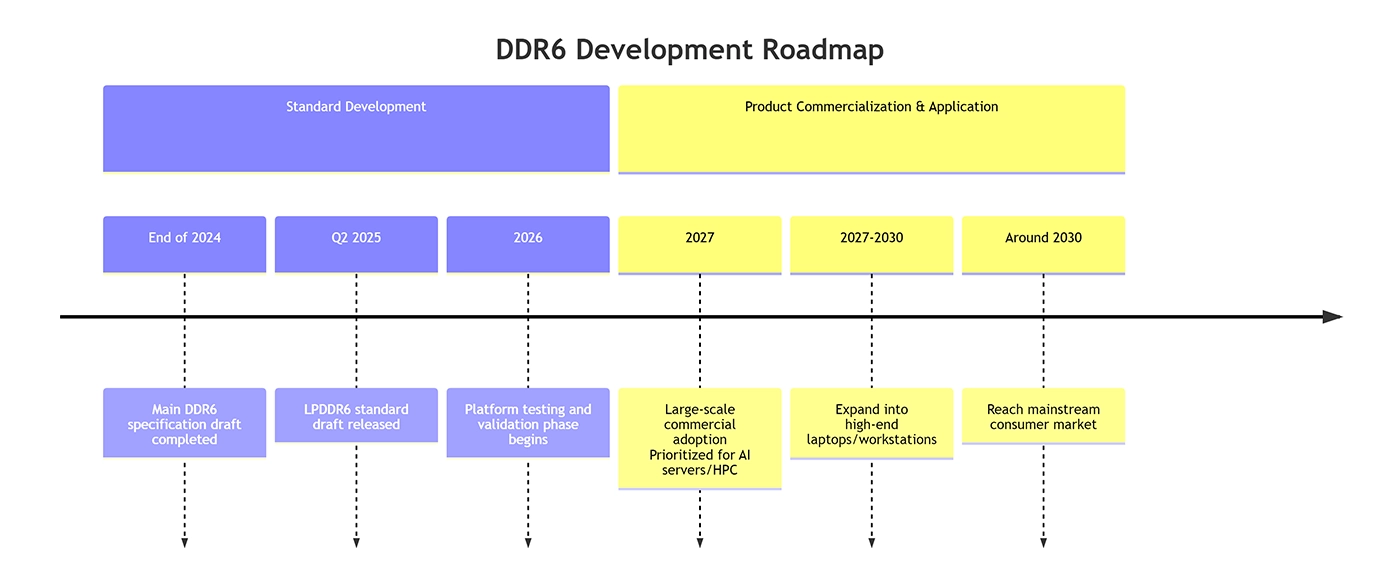

A finales de 2024, el JEDEC completó el principal proyecto de especificación de la DDR6, sentando las bases para el posterior desarrollo tecnológico y la implantación de productos. Al mismo tiempo, el proyecto de especificación para la versión de bajo consumo, LPDDR6, se publicó en el segundo trimestre de 2025. Al igual que en anteriores procesos de desarrollo de estándares de memoria, la formulación de la DDR6 reúne a los principales fabricantes mundiales de memorias, diseñadores de chips y vendedores de dispositivos finales. De este modo se garantiza que la norma sea compatible con diferentes escenarios de aplicación y plataformas de hardware, al tiempo que se promueve el desarrollo coordinado de todo el ecosistema industrial.

Los tres problemas principales que pretende resolver la DDR6

El desarrollo de la DDR6 se centra en abordar tres retos fundamentales a los que se enfrenta actualmente la industria: ancho de banda insuficiente, baja eficiencia energética y limitaciones arquitectónicas.

El primer problema es la insuficiencia de ancho de banda. Con el rápido crecimiento de la demanda de formación en IA y procesamiento de datos a gran escala, la velocidad máxima actual de la DDR5, de 8.000 MT/s, es cada vez más incapaz de satisfacer los requisitos de transmisión a alta velocidad de cantidades masivas de datos, convirtiéndose en un cuello de botella clave que limita el rendimiento global del sistema. La DDR6 mejora la arquitectura de canales y las tecnologías de transmisión para elevar la velocidad de datos inicial a 8800 MT/s, con planes para aumentarla a 17.600 MT/s en fases posteriores, con el objetivo fundamental de eliminar los cuellos de botella del ancho de banda en escenarios de alta carga.

La segunda cuestión es la eficiencia energética. En los servidores de IA y los entornos de centros de datos, los módulos de memoria se despliegan a densidades cada vez más altas, lo que aumenta significativamente el consumo de energía y la generación de calor. Esto no sólo eleva los costes operativos, sino que también impone mayores exigencias a los sistemas de refrigeración. Al reducir el voltaje de funcionamiento y optimizar los mecanismos de gestión de la energía, la DDR6 mejora el rendimiento al tiempo que reduce el consumo de energía. Se espera que el consumo de energía típico se reduzca en 15-20% en comparación con DDR5, lo que hace que DDR6 sea más adecuada para escenarios de despliegue de alta densidad.

El tercer problema son las limitaciones arquitectónicas. La estructura de canales de 2 × 32 bits utilizada por DDR5 es propensa a problemas de integridad de la señal a altas frecuencias. Además, los formatos tradicionales DIMM y SO-DIMM requieren mucho espacio y tienen limitaciones de frecuencia en configuraciones 2DPC. La DDR6 introduce una innovadora arquitectura de subcanales de 4 × 24 bits y adopta el estándar de interfaz CAMM2. Esto no sólo mejora la capacidad de procesamiento en paralelo, sino que también resuelve las limitaciones de espacio y frecuencia de los paquetes de memoria tradicionales, proporcionando soporte arquitectónico para la implantación de memorias de alto rendimiento y alta densidad.

Principales cambios técnicos de la DDR6

Un gran salto en la velocidad de transferencia de datos

Un aumento significativo de la velocidad de transferencia de datos es uno de los avances tecnológicos más importantes de la DDR6. Según las hojas de ruta actuales de la industria, la DDR6 comenzará con una velocidad de transferencia de datos inicial de 8800 MT/s, superando ya el máximo actual de la DDR5, de 8000 MT/s. A lo largo de todo el ciclo de vida del producto, se espera que las velocidades de la DDR6 sigan aumentando hasta los 17.600 MT/s, con algunas versiones overclockeadas que podrían superar los 21.000 MT/s. Se espera que el rendimiento global sea aproximadamente entre dos y tres veces superior al de la DDR5.

Un aumento tan sustancial de la velocidad no se consigue simplemente aumentando la frecuencia de reloj. Es el resultado del efecto combinado de varias tecnologías. Por un lado, la DDR6 optimiza los procesos de fabricación de chips de memoria, mejorando el rendimiento eléctrico y proporcionando una base de hardware para el funcionamiento a alta frecuencia. Por otro lado, la DDR6 introduce diseños de optimización de la integridad de la señal más avanzados, como tecnologías de empaquetado mejoradas, reglas de enrutamiento más precisas y un control de la temporización más estricto. Estas medidas reducen eficazmente las interferencias y la atenuación de la señal a altas frecuencias. Además, la DDR6 adopta un mecanismo de prefetch de 16n, frente al prefetch de 8n utilizado en la DDR5. Esto mejora aún más la eficiencia de la transferencia de datos, permitiendo transmitir más datos a la misma frecuencia de reloj y posibilitando un salto importante en la velocidad de transferencia global.

Cambios en la arquitectura de subcanales

La DDR6 introduce una innovación revolucionaria en la arquitectura de canales al adoptar una estructura de subcanales de 4 × 24 bits, en sustitución del diseño de canales de 2 × 32 bits utilizado por la DDR5. El objetivo principal de este cambio arquitectónico es mejorar el ancho de banda manteniendo la integridad de la señal a altas frecuencias de funcionamiento. Los diseños tradicionales de bus ancho tienden a sufrir de diafonía de señal cuando las frecuencias aumentan más allá de un cierto punto, lo que conduce a una menor estabilidad de transmisión. Al aumentar el número de canales y reducir la anchura de bits de cada canal, la DDR6 amplía la anchura total del bus de los 64 bits de la DDR5 a 96 bits. Este enfoque mejora la capacidad de procesamiento en paralelo al tiempo que reduce la presión de transmisión de la señal en cada canal individual.

La arquitectura de subcanales de 4 × 24 bits permite una transmisión de datos en paralelo más eficiente, permitiendo que cada subcanal realice operaciones de lectura y escritura de forma independiente. Esto mejora significativamente la concurrencia de memoria y la utilización del ancho de banda. En escenarios como el entrenamiento de inteligencia artificial y el procesamiento de datos a gran escala, en los que deben manejarse simultáneamente múltiples flujos de datos, las ventajas de esta arquitectura se hacen especialmente evidentes. Al mismo tiempo, la arquitectura de subcanales proporciona mayor flexibilidad para ampliar la capacidad y optimizar la eficiencia energética. Permite ajustar dinámicamente el estado operativo de cada subcanal en función de los requisitos de la aplicación, logrando un mejor equilibrio entre rendimiento y consumo de energía.

Cambios en los factores de forma de módulos e interfaces (CAMM2)

La DDR6 adoptará plenamente la norma de interfaz CAMM2, que sustituirá a las interfaces DIMM y SO-DIMM tradicionales que se han utilizado durante muchos años. Esto representa una importante transformación en los factores de forma de los módulos de memoria. CAMM2 son las siglas de Compression Attached Memory Module. Fue introducido originalmente por Dell, revisado posteriormente por JEDEC, y se convirtió oficialmente en un estándar JEDEC a finales de 2023. A diferencia de los módulos de memoria tradicionales, que se conectan a las ranuras mediante conectores de borde en la parte inferior, CAMM2 utiliza un conector de compresión que se conecta a través de una fina placa adaptadora en la placa base y se fija con tornillos. Esta nueva forma de interfaz aporta varias ventajas significativas:

CAMM2 resuelve eficazmente las limitaciones de frecuencia de las configuraciones 2DPC tradicionales. En los diseños 2DPC convencionales, la instalación de dos módulos de memoria por canal aumenta la complejidad eléctrica y limita la frecuencia de la memoria. CAMM2 traslada la compleja topología al propio módulo, gestionando la complejidad internamente y permitiendo que un sistema alcance el máximo rendimiento y la máxima capacidad al mismo tiempo.

CAMM2 reduce significativamente la altura del eje Z y el uso de espacio total de la placa base. En comparación con SO-DIMM, CAMM2 reduce el grosor en 57%, lo que la hace más adecuada para dispositivos con estrictos requisitos de grosor, como portátiles delgados y ligeros y tabletas.

El conector CAMM2 utiliza un diseño de patillas LGA, con almohadillas de contacto tanto en la placa base como en el módulo de memoria. Esto reduce el riesgo de daños en la interfaz, y el propio conector puede sustituirse de forma independiente, lo que hace más cómodo su mantenimiento.

Evolución de la eficiencia energética y la gestión de la energía

En cuanto a la optimización de la eficiencia energética, la DDR6 se basa en las ventajas de bajo consumo de la DDR5 y logra nuevos avances. La tensión de funcionamiento estándar de la DDR5 es de 1,1 V, mientras que la DDR6 reducirá la tensión de funcionamiento a 1,0 V o incluso menos. Un voltaje más bajo conlleva directamente una reducción del consumo de energía, y se espera que el consumo típico de la DDR6 sea 15-20% inferior al de la DDR5. Esta mejora es especialmente crítica para escenarios de despliegue de alta densidad, como centros de datos y servidores de IA, ya que ayuda a reducir el consumo total de energía y los costes de refrigeración, al tiempo que mejora la eficiencia energética del sistema.

Además de reducir el voltaje de funcionamiento, la DDR6 introduce mecanismos más avanzados de gestión de la energía. Al optimizar la lógica de gestión energética del controlador de memoria, la DDR6 puede ajustar dinámicamente el estado operativo de los módulos de memoria en función de la carga del sistema. En condiciones de baja carga, la frecuencia y el voltaje de la memoria se reducen automáticamente, lo que permite al sistema entrar en modos de bajo consumo. En condiciones de carga elevada, el rendimiento aumenta rápidamente para garantizar el cumplimiento de los requisitos de transmisión de datos. Este enfoque de gestión dinámica de la energía permite a la DDR6 alcanzar un equilibrio óptimo entre rendimiento y consumo de energía en diferentes escenarios de aplicación, ofreciendo un alto rendimiento al tiempo que se conserva eficazmente la energía.

Ampliación de la capacidad y potencial de apilamiento

La DDR6 ofrece un mayor potencial de ampliación de la capacidad, lo que la hace más adecuada para satisfacer los requisitos de gran capacidad de memoria de la IA y las cargas de trabajo informáticas de alto rendimiento. Las innovaciones en la tecnología de apilamiento son un factor clave para la ampliación de la capacidad de la DDR6. La DDR6 adoptará tecnologías de apilamiento 3D más avanzadas, apilando más troqueles de memoria verticalmente para aumentar significativamente la densidad de capacidad por chip. Al mismo tiempo, el diseño modular de la interfaz CAMM2 facilita la ampliación de la capacidad al admitir configuraciones de módulos apilados para aumentar la capacidad total de memoria del sistema.

Por ejemplo, dos módulos CAMM2 monocanal de tipo D pueden apilarse teóricamente a lo largo del eje Z, lo que permite que la memoria total del sistema alcance los 512 GB. A medida que la tecnología madure, podrán lograrse avances de capacidad aún mayores. Los módulos DDR5 CAMM2 previstos actualmente pueden alcanzar una capacidad máxima de 256 GB. Con chips de memoria de mayor densidad y tecnologías de apilamiento, se espera que los módulos DDR6 CAMM2 superen este límite.

Comparación exhaustiva entre DDR6 y DDR5

| Categoría | DDR5 | DDR6 |

|---|---|---|

| Velocidad de datos | Hasta unos 8000 MT/s | 8800 MT/s iniciales, aumento previsto a 17.600 MT/s, las versiones overclockeadas pueden superar los 21.000 MT/s |

| Arquitectura de canales | 2 × 32 bits (ancho total del bus 64 bits) | 4 × 24 bits (ancho total del bus 96 bits) |

| Interfaz Factor de forma | Principalmente DIMM, SO-DIMM | Adopta totalmente CAMM2 / LPCAMM2 |

| Tensión de funcionamiento | 1.1 V | 1,0 V o inferior |

| Consumo típico | Nivel básico | 15-20% inferior a DDR5 |

| Capacidad máxima por módulo | 256 GB (DIMM), 128 GB (SO-DIMM) | Se espera que supere los 256 GB, el apilamiento de dos módulos puede alcanzar los 512 GB |

| Mecanismo de precarga | 8n prefetch | 16n prefetch |

| 2DPC Limitación de frecuencia | Importantes limitaciones de frecuencia | Complejidad gestionada dentro del módulo, sin limitación de frecuencia evidente. |

| Principales escenarios de aplicación | PC, servidores y estaciones de trabajo de gama media y alta (periodo de transición) | Servidores de inteligencia artificial, informática de alto rendimiento, estaciones de trabajo de gama alta, PC emblemáticos |

Compatibilidad de DDR6

No existe retrocompatibilidad entre DDR6 y DDR5. Esto significa que las placas base diseñadas para DDR5 no pueden utilizar directamente memoria DDR6, y viceversa. La razón principal radica en las diferencias fundamentales de arquitectura, factores de forma de la interfaz y especificaciones eléctricas.

En primer lugar, hay una diferencia en el factor de forma de la interfaz. La DDR6 adopta por completo la interfaz CAMM2, mientras que la DDR5 utiliza principalmente las interfaces DIMM y SO-DIMM tradicionales. Sus dimensiones físicas y métodos de conexión son completamente diferentes, lo que las hace incompatibles entre sí.

En segundo lugar, hay diferencias en las especificaciones eléctricas. La DDR6 reduce la tensión de funcionamiento a 1,0 V o incluso menos, frente a los 1,1 V de la DDR5. Además, sus definiciones de señales y parámetros de temporización son totalmente diferentes. Los controladores de memoria deben diseñarse teniendo en cuenta especificaciones eléctricas concretas para controlar los circuitos y manejar las señales correctamente. Un controlador de memoria DDR5 no puede cumplir los requisitos eléctricos de DDR6, y su uso forzado provocaría daños en el dispositivo o impediría su correcto funcionamiento.

Por último, hay diferencias en la arquitectura de canales. DDR6 utiliza una arquitectura de subcanales de 4 × 24 bits, que es fundamentalmente diferente de la arquitectura de 2 × 32 bits utilizada por DDR5. La lógica de diseño del controlador de memoria es completamente distinta en cada caso, lo que en última instancia determina que los dos estándares sean incompatibles. Por tanto, la implantación de DDR6 requiere el apoyo coordinado de las CPU, las placas base y todo el ecosistema de la industria para formar un sistema completo de soporte de hardware. En la actualidad, fabricantes de memorias como Samsung, SK hynix y Micron colaboran estrechamente con proveedores de chips como Intel, AMD y NVIDIA para avanzar conjuntamente en la validación de la plataforma DDR6 y acelerar el desarrollo del ecosistema.

Análisis del escenario de aplicación de DDR6

Centros de datos y computación en nube

Los centros de datos y la computación en nube se encuentran entre los escenarios de aplicación más importantes para la DDR6. Actualmente, los servicios de computación en nube evolucionan hacia la gran escala, la alta concurrencia y la baja latencia. Los centros de datos deben gestionar un número masivo de solicitudes de usuarios y tareas de transferencia de datos, lo que exige un ancho de banda y una capacidad de memoria extremadamente elevados. La DDR6 puede aumentar significativamente el ancho de banda de la memoria en los servidores de los centros de datos, acelerando el procesamiento y la transmisión de datos y reduciendo al mismo tiempo la latencia de respuesta a las peticiones de los usuarios.

Al mismo tiempo, la alta eficiencia energética de la DDR6 se adapta bien a los requisitos de los centros de datos. Los centros de datos funcionan con una alta densidad de servidores, y los módulos de memoria representan una parte sustancial del consumo total de energía del sistema. En comparación con DDR5, DDR6 reduce el consumo de energía en 15-20%, lo que puede reducir de forma efectiva el uso total de energía y los costes de refrigeración en los centros de datos, al tiempo que mejora la eficiencia operativa. Además, la memoria DDR6 admite ampliaciones de gran capacidad, lo que satisface las necesidades de almacenamiento en caché de datos a gran escala y procesamiento paralelo en entornos de computación en nube. Esto proporciona un mayor soporte de memoria para servicios como las bases de datos en la nube, el almacenamiento en la nube y el renderizado en la nube. Con la adopción comercial de la DDR6, se espera que las capacidades informáticas y de procesamiento de datos de los centros de datos den un salto cualitativo.

IA y computación de alto rendimiento (HPC)

La IA y la informática de alto rendimiento son las principales fuerzas impulsoras del desarrollo y la adopción de la DDR6, y son también los escenarios de aplicación en los que la DDR6 puede ofrecer las mayores ventajas. En los escenarios de entrenamiento de IA, el tamaño de los parámetros de los modelos sigue creciendo, lo que exige el procesamiento de cantidades ingentes de datos de entrenamiento. Esto impone exigencias extremas al ancho de banda y la capacidad de la memoria. Las características de gran ancho de banda de la DDR6 garantizan que las CPU y GPU puedan leer y escribir rápidamente los datos de entrenamiento durante el proceso de formación, evitando cuellos de botella en la transferencia de datos y mejorando significativamente la eficiencia de la formación.

En el campo de la informática de alto rendimiento, como la predicción meteorológica, las simulaciones astrofísicas y la investigación farmacéutica, los sistemas deben realizar grandes volúmenes de cálculos complejos y procesamiento de datos. Estas cargas de trabajo requieren niveles extremadamente altos de capacidad de procesamiento paralelo y estabilidad de la memoria. La arquitectura de subcanales de 4 × 24 bits de la DDR6 mejora el procesamiento paralelo de datos, mientras que el mecanismo de prefetch de 16n y los mecanismos avanzados de corrección de errores garantizan tanto la eficiencia como la estabilidad en la transmisión de datos. Además, las ventajas de bajo consumo de la DDR6 ayudan a reducir el consumo de energía en los clusters de computación de alto rendimiento, mejorando su capacidad para funcionar de forma continua durante largos periodos. A medida que la IA y la informática de alto rendimiento sigan expandiéndose, la DDR6 se convertirá en una configuración de memoria fundamental en estos campos.

PC de consumo y estaciones de trabajo de gama alta

Aunque la DDR6 se implantará comercialmente primero en servidores y campos relacionados con la IA, se espera que penetre gradualmente en los mercados de PC de consumo y estaciones de trabajo de gama alta a medida que el ecosistema madure y los costes disminuyan. Para los portátiles de juegos de gama alta y los PC de sobremesa emblemáticos, la alta frecuencia y el gran ancho de banda de la DDR6 pueden mejorar los tiempos de carga de los juegos y la fluidez general. Esto se nota especialmente cuando se ejecutan grandes juegos AAA, en los que la DDR6 puede reducir eficazmente el tartamudeo y las caídas de fotogramas. Al mismo tiempo, el fino diseño que permite la interfaz CAMM2 ayuda a los fabricantes a crear portátiles de juego más finos y ligeros con un alto rendimiento.

Las estaciones de trabajo de gama alta también estarán entre los primeros segmentos de consumo en adoptar la DDR6. Las estaciones de trabajo móviles y gráficas se utilizan principalmente para cargas de trabajo profesionales como la edición de vídeo, el modelado 3D y el renderizado de animaciones, que plantean exigencias muy elevadas en cuanto a frecuencia, capacidad y estabilidad de la memoria. La memoria SO-DIMM tradicional sufre limitaciones de frecuencia en configuraciones 2DPC y no puede satisfacer los requisitos de rendimiento de las estaciones de trabajo de gama alta. La memoria DDR6 combinada con la interfaz CAMM2 resuelve este problema al tiempo que proporciona una mayor capacidad.

Progreso de la normalización y calendario de comercialización

La organización responsable de liderar los estándares de tecnología de memoria, JEDEC, completó el borrador de la especificación principal DDR6 a finales de 2024. El borrador de la norma LPDDR6, destinada a dispositivos móviles, también se publicó en el segundo trimestre de 2025. La siguiente etapa será la fase crítica de pruebas y validación de plataformas, que se espera que tenga lugar en 2026. Fabricantes de chips como Intel y AMD participarán para garantizar la compatibilidad entre la DDR6 y las futuras plataformas de procesadores.

Según las previsiones de la industria, se espera que la DDR6 comience su implantación comercial a gran escala en torno a 2027. Se espera que su adopción siga un patrón que va de la gama alta a la gama media. Primero se utilizará en campos extremadamente sensibles al rendimiento pero menos sensibles al coste, como los servidores de IA, los sistemas informáticos de alto rendimiento y los centros de datos. A continuación, se expandirá gradualmente a los mercados de portátiles y estaciones de trabajo de gama alta. Es posible que los usuarios habituales de ordenadores de sobremesa y portátiles no se encuentren con la DDR6 hasta 2030.

La DDR6 no es una simple iteración, sino una evolución arquitectónica diseñada para abordar retos fundamentales. Su principal objetivo es superar los actuales cuellos de botella en el ancho de banda de la memoria y la eficiencia energética, proporcionando un soporte de infraestructura esencial para la inteligencia artificial, la informática de alto rendimiento y el futuro procesamiento de datos a gran escala. El viaje de la DDR1 a la DDR5 demuestra un patrón constante en el que la tecnología de memoria evoluciona continuamente para adaptarse a las demandas informáticas. La DDR6 representa el siguiente capítulo de esta progresión. Lleva la misión de ampliar los límites de la informática, y su forma final y adopción generalizada tendrán un profundo impacto en la trayectoria del desarrollo tecnológico durante la próxima década.