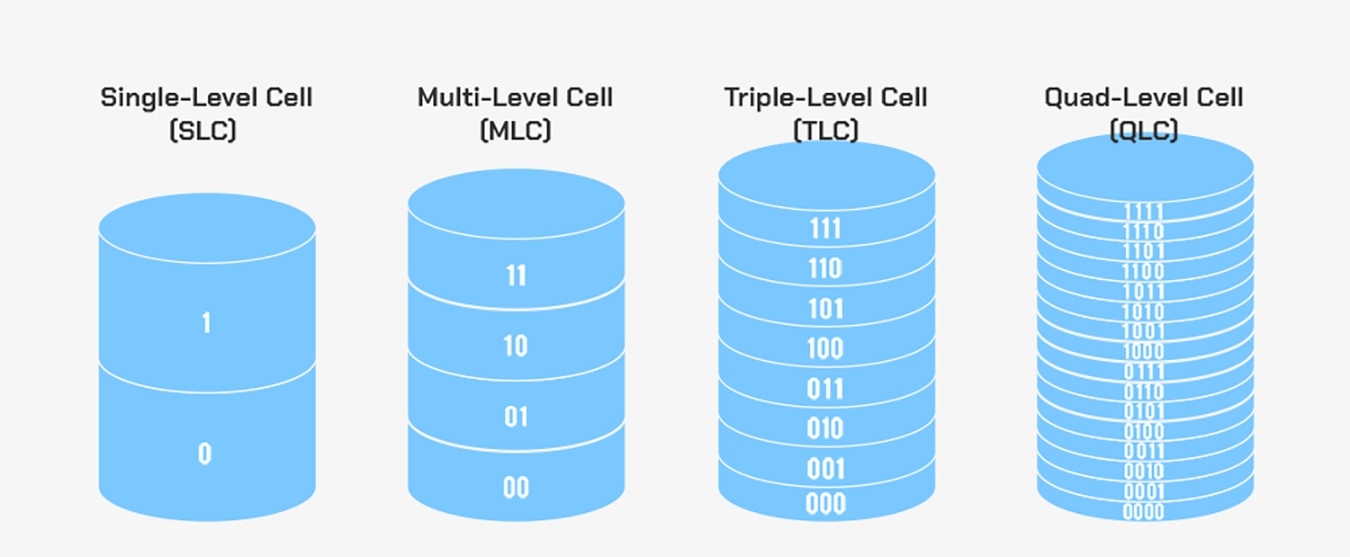

Estamos en una era de explosión del volumen de datos. La formación en IA, las operaciones de servicios en la nube, el archivado de vídeo de alta definición y la demanda de sustituir los discos duros mecánicos tradicionales están impulsando un deseo casi ilimitado de capacidad de almacenamiento. Sin embargo, la miniaturización de los procesos de fabricación de semiconductores se acerca gradualmente a los límites físicos, lo que hace crucial reducir el coste por GB aumentando la densidad de almacenamiento. En el camino de la evolución tecnológica, desde la SLC que almacena 1 bit por celda, a la MLC con 2 bits, la TLC con 3 bits y la QLC con 4 bits, cada paso representa un nuevo equilibrio entre coste y fiabilidad. Hoy en día, la tecnología PLC (Penta-Level Cell), que almacena 5 bits de datos por celda, se considera una dirección de desarrollo clave para la próxima generación de almacenamiento de alta densidad.

Conceptos básicos de NAND Flash: cómo almacena los datos la carga

Flash NAND es un tipo de memoria no volátil, lo que significa que puede retener datos durante mucho tiempo incluso después de apagarse. Su funcionalidad principal se basa en el control preciso de la cantidad de carga dentro de cada célula de memoria. La célula de memoria más básica puede entenderse como un transistor especial con una capa aislante llamada "puerta flotante" o una "capa trampa de carga" funcional similar. El aspecto único de esta capa es que los electrones inyectados quedan efectivamente aislados, lo que permite almacenarlos durante mucho tiempo, posibilitando el almacenamiento persistente de datos.

Principio de registro de datosEl método específico de registro de datos se caracteriza por la "tensión umbral". La tensión umbral es la tensión mínima necesaria para encender el transistor. Al inyectar diferentes cantidades de electrones en la puerta flotante, se alteran las características eléctricas del transistor, cambiando así su tensión umbral. El controlador aplica una tensión de referencia y detecta si el transistor se enciende, determinando así el estado de tensión umbral actual de la célula. Cada estado de tensión específico corresponde a una codificación de datos única. La esencia de la tecnología de "célula multinivel" es definir y distinguir con precisión más de dos estados de tensión umbral dentro de una misma célula, almacenando así más de un bit de datos.

Escritura, lectura y borradoBasándose en los principios anteriores, las operaciones en NAND Flash se dividen principalmente en tres tipos: escritura, lectura y borrado. La operación de escritura, también llamada programación, se consigue inyectando carga en la puerta flotante de la celda. La operación de borrado elimina la carga de la puerta flotante, restaurando la célula a su estado inicial. Es especialmente importante tener en cuenta que la unidad de borrado más pequeña para NAND Flash es el "bloque", mientras que la programación y la lectura se pueden realizar en la unidad de "página" más pequeña. Durante una operación de lectura, el controlador aplica una serie de voltajes de referencia precisos a la celda. Al detectar si el transistor se enciende a diferentes voltajes, determina el voltaje umbral correspondiente a la carga almacenada en ese momento y, en última instancia, descodifica los datos almacenados.

El auge de la NAND 3DA medida que los procesos de fabricación seguían reduciéndose, la tecnología NAND Flash planar se encontró con cuellos de botella físicos y problemas de fiabilidad al reducirse aún más el tamaño. Para seguir aumentando la capacidad, la industria recurrió a la tecnología de apilamiento tridimensional, conocida como 3D NAND. La NAND 3D apila las celdas de memoria verticalmente, como si se construyera un rascacielos, con lo que se consigue multiplicar la densidad de almacenamiento en la misma superficie plana. Sin embargo, más allá del apilamiento tridimensional, el aumento del número de bits almacenados por celda de memoria sigue siendo otra vía tecnológica fundamental para mejorar aún más la densidad de almacenamiento y reducir los costes.

Evolución de la tecnología de almacenamiento: De SLC a QLC

El objetivo central de la evolución de la tecnología de almacenamiento es aumentar continuamente la densidad de almacenamiento para reducir el coste por GB. Este objetivo se consigue principalmente aumentando el número de bits almacenados por celda de memoria. A continuación se esboza la trayectoria de desarrollo tecnológico de SLC a QLC.

SLC: la referencia en rendimiento y fiabilidad

SLC son las siglas de Single-Level Cell, que almacenan 1 bit de datos por celda. Este 1 bit de datos corresponde a dos estados de carga, normalmente representados como 0 y 1. Dado que sólo es necesario distinguir dos estados, SLC ofrece velocidades de lectura/escritura extremadamente altas, la mayor vida útil y la mayor fiabilidad de datos. Su desventaja es la menor densidad de almacenamiento, que se traduce en el mayor coste por GB. Por eso, SLC se utiliza principalmente en servidores de empresas y en campos industriales donde el rendimiento y la fiabilidad son primordiales.

MLC: el punto de equilibrio entre rendimiento y coste

MLC son las siglas de Multi-Level Cell, que almacenan 2 bits de datos por celda, correspondientes a cuatro estados de carga. Al almacenar más datos en cada celda, MLC consigue el doble de capacidad de almacenamiento que SLC en la misma superficie de chip, lo que reduce significativamente el coste. Aunque su rendimiento, vida útil y fiabilidad no son tan altos como los de SLC, alcanzan un buen equilibrio. La MLC fue durante mucho tiempo la opción dominante para las unidades de estado sólido de consumo de gama alta y el almacenamiento empresarial.

TLC: la opción dominante para el mercado de consumo

TLC son las siglas de Triple-Level Cell, que almacenan 3 bits de datos por celda, correspondientes a ocho estados de carga. TLC amplía aún más las ventajas de la densidad de almacenamiento y la reducción de costes, convirtiéndose en la corriente dominante absoluta en el mercado actual de las SSD de consumo. Con avanzados algoritmos de controlador y tecnologías de corrección de errores, su resistencia ya satisface las necesidades de la inmensa mayoría de las aplicaciones cotidianas.

QLC: La práctica del almacenamiento de alta densidad

QLC son las siglas de Quad-Level Cell, que almacenan 4 bits de datos por celda, correspondientes a dieciséis estados de carga. La ventaja de QLC radica en su alta densidad de almacenamiento y su menor coste, lo que la hace muy adecuada para construir unidades de estado sólido de gran capacidad. Sin embargo, sus desventajas también son más evidentes, como una velocidad de escritura más lenta y una vida útil más corta en comparación con la TLC. En la actualidad, QLC se utiliza principalmente en situaciones con bajos requisitos de velocidad de escritura, como el almacenamiento externo de gran capacidad y el almacenamiento de datos en frío en centros de datos.

Principales retos de la evolución

La evolución de SLC a QLC no es una simple suma lineal. A medida que aumenta el número de bits por celda, el número de estados de tensión que deben distinguirse con precisión crece exponencialmente, de 2 a 16. Esto significa que la ventana de tensión utilizada para distinguir los distintos estados se comprime hasta hacerse extremadamente estrecha. Esto significa que la ventana de tensión utilizada para distinguir diferentes estados se comprime de forma extremadamente estrecha, lo que hace que los requisitos de precisión del control de carga, capacidad antiinterferencia de la señal y tecnología de corrección de errores sean extremadamente estrictos. El desarrollo de la tecnología PLC es el siguiente paso para afrontar directamente este reto fundamental.

La tecnología PLC

PLC, o Penta-Level Cell, es la siguiente etapa en la evolución de la tecnología NAND Flash. Su principal característica es que eleva la densidad de almacenamiento a nuevas cotas, pero también se enfrenta a retos de ingeniería sin precedentes.

Definición técnica de PLC

PLC son las siglas de Penta-Level Cell, lo que significa que cada celda de memoria almacena 5 bits de datos. Estos 5 bits corresponden a 32 estados diferentes de umbral de tensión. En comparación con los 16 estados de QLC, PLC necesita definir con precisión el doble de niveles de tensión dentro de la misma ventana física de tensión. En la actualidad, esta tecnología se encuentra aún en fase de desarrollo y verificación, con fabricantes líderes como Solidigm demostrando primero productos prototipo, lo que indica la dirección futura del almacenamiento de alta densidad.

Reto principal: ventana de tensión estrecha

El reto fundamental al que se enfrenta la tecnología PLC procede del nivel físico. Para distinguir 32 estados de tensión, la diferencia de tensión entre cada estado adyacente debe comprimirse hasta un valor muy pequeño. Esto hace que la ventana de tensión sea extremadamente estrecha y que la tolerancia de error caiga en picado. Cualquier pequeña fluctuación de carga, variación de las características del transistor o ruido electrónico durante la lectura podría hacer que el controlador juzgara mal el estado de tensión, lo que provocaría errores en los datos. Puede decirse que el límite de viabilidad del PLC depende directamente de si puede superarse eficazmente este reto de la relación señal/ruido.

Avance de la ingeniería

Ante las elevadísimas tasas de error de bits nativas, la viabilidad de los PLC depende en gran medida de avances significativos en los controladores de almacenamiento y la tecnología de corrección de errores. Los códigos de corrección de errores tradicionales ya no pueden satisfacer las demandas; es necesario adoptar códigos de comprobación de paridad de baja densidad más potentes combinados con tecnología de descodificación de decisión suave. La decodificación de decisión suave no se limita a juzgar la señal como 0 o 1, sino que infiere el valor más probable de los datos mediante cálculos de probabilidad, lo que mejora significativamente la capacidad de corrección de errores. Además, el controlador debe disponer de mecanismos inteligentes de reintento de lectura. Cuando falla la lectura inicial, puede ajustar dinámicamente la tensión de referencia en varias lecturas para encontrar el punto de señal correcto. Estos complejos procesos algorítmicos plantean exigencias muy elevadas a la potencia de cálculo del controlador.

Impacto en el rendimiento y la vida útil

Las características de la tecnología PLC también afectan directamente a su rendimiento y fiabilidad. Dado que es necesario un control más preciso de la inyección de carga para que coincida con 32 estados de tensión, el proceso de escritura requiere más ciclos de programación-verificación, lo que da lugar a velocidades de escritura significativamente más lentas en comparación con QLC y TLC. En cuanto a la vida útil, las operaciones de carga más frecuentes y precisas aceleran el envejecimiento de las células de memoria. Por tanto, se espera que la resistencia nativa de la memoria flash PLC sea inferior a la de la QLC. Para compensar esta debilidad en aplicaciones prácticas, se necesitan más medidas de compensación a nivel de sistema, como configurar un mayor sobreaprovisionamiento, adoptar algoritmos de nivelación de desgaste de datos más agresivos y confiar en el almacenamiento en caché SLC para absorber las cargas de escritura en ráfagas.

Diferencias entre las cinco tecnologías de células de memoria

La siguiente tabla muestra claramente las diferencias en métricas clave entre las cinco tecnologías de celdas de memoria NAND Flash, desde SLC hasta PLC.

| Tipo de tecnología | Bits por celda | Número de Estados | Coste relativo | Resistencia relativa | Ventaja principal | Escenarios típicos de aplicación |

|---|---|---|---|---|---|---|

| SLC | 1 bit | 2 | Más alto | Más alto | Velocidad ultrarrápida, vida útil muy larga, alta fiabilidad | Caché empresarial de alta velocidad y misión crítica |

| MLC | 2 bits | 4 | Alta | Alta | Excelente equilibrio entre rendimiento y coste | SSD para empresas, SSD para consumidores de gama alta |

| TLC | 3 bits | 8 | Medio | Medio | Elección mayoritaria por coste y capacidad | SSD de consumo general, dispositivos móviles |

| QLC | 4 bits | 16 | Bajo | Relativamente bajo | Alta densidad de almacenamiento, bajo coste | SSD de gran capacidad para consumidores, almacenamiento en frío para centros de datos |

| PLC | 5 bits | 32 | Previsiblemente bajo | Previsiblemente bajo | Máxima densidad de almacenamiento, mínimo coste | Archivo de datos en frío a gran escala |

De la tabla se desprende una tendencia clara: a medida que aumenta el número de bits almacenados por celda, la densidad de almacenamiento y la rentabilidad mejoran continuamente, pero a costa de la velocidad de lectura/escritura y la vida útil de las celdas. Por tanto, las distintas tecnologías son adecuadas para escenarios claramente diferentes. SLC sirve para las áreas con mayores exigencias de rendimiento y fiabilidad, mientras que el objetivo de PLC es ofrecer una solución de almacenamiento muy rentable para datos masivos en frío dentro de unos límites aceptables de rendimiento y vida útil.

Valor, posicionamiento y futuro de la tecnología PLC

Ventaja definitiva en coste y densidad. La fuerza impulsora fundamental del desarrollo de la tecnología PLC es la búsqueda de la máxima densidad de almacenamiento y rentabilidad. Al acomodar 5 bits de datos por celda de memoria, PLC puede proporcionar una mayor capacidad de almacenamiento que QLC en la misma área de oblea de chip. Esto se traduce directamente en un menor coste por GB. Su principal mercado objetivo es sustituir las áreas actualmente dominadas por los discos duros mecánicos de alta capacidad, ofreciendo una solución de almacenamiento de datos en frío para centros de datos a hiperescala que presenta ventajas en consumo de energía por unidad de volumen, velocidad de acceso y huella física.

Dificultades graves. La producción en serie y la aplicación de la tecnología PLC se enfrentan a múltiples y graves retos. En primer lugar, distinguir 32 estados de tensión requiere una precisión de control sin precedentes, lo que conlleva un bajo rendimiento inicial de la producción y un control de calidad extremadamente complejo. En segundo lugar, para lograr un almacenamiento de datos fiable, el controlador necesita potentes capacidades informáticas en tiempo real para ejecutar complejos algoritmos de corrección de errores, lo que aumenta la dificultad de diseño y el consumo de energía del chip controlador principal. Por último, la resistencia nativa de la memoria flash PLC es baja y debe compensarse mediante técnicas a nivel de sistema, como la configuración de áreas de sobreaprovisionamiento más grandes, la adopción de mecanismos más eficientes de nivelación del desgaste de los datos y la recogida de basura. Todo ello aumenta la complejidad del diseño de la solución global.

Escenario de aplicación Posicionamiento.Basándose en sus características técnicas, el posicionamiento del PLC en los escenarios de aplicación es muy claro y específico. Es muy adecuado para escenarios de archivado de datos ultrafríos en los que las operaciones de escritura son extremadamente raras y la frecuencia de acceso de lectura es muy baja. Algunos ejemplos son los niveles de almacenamiento de archivos profundos en servicios en la nube, las copias de seguridad de datos a largo plazo para el cumplimiento de normativas, los archivos de registro históricos y la conservación de activos digitales como imágenes médicas. Por el contrario, PLC es totalmente inadecuado para tareas de escritura intensiva, como sistemas operativos, bases de datos y datos de aplicaciones actualizados con frecuencia. Su función es ser el nivel básico de menor coste y mayor capacidad del ecosistema de almacenamiento de datos.

Perspectivas de futuro.La adopción comercial de la tecnología PLC no sólo depende de la madurez de los propios chips de memoria flash, sino también del desarrollo coordinado de chips controladores, algoritmos de firmware e incluso de todo el ecosistema del sistema de almacenamiento de datos. Representa la exploración de los límites físicos por parte de la tecnología NAND Flash con la arquitectura actual. En general, la industria cree que PLC puede estar acercándose al límite práctico de la mejora de la densidad a nivel de celda basada en el principio de almacenamiento de carga. Los avances futuros dependerán más del aumento continuo de las capas de apilamiento en 3D y del aprovechamiento de innovaciones tecnológicas como la inteligencia artificial para optimizar la gestión de datos y la eficiencia de la corrección de errores, con lo que se lograrán avances a nivel de sistema en rendimiento y fiabilidad.

PLC NAND Flash representa un importante desafío a los límites físicos de la arquitectura actual de la tecnología de almacenamiento. Se trata de una evolución natural impulsada por la continua búsqueda de necesidades de almacenamiento de menor coste y mayor densidad. Aunque sus características inherentes determinan que servirá principalmente para campos específicos, mediante la optimización continua de los algoritmos de los controladores y las soluciones a nivel de sistema, se espera que PLC desempeñe un papel indispensable en el futuro ecosistema de almacenamiento de datos al dar cabida a cantidades masivas de datos fríos.